基于ZYNQ UltraScale+的高速图像数据采集系统设计

2022-06-15唐宇枫刘一清

唐宇枫,刘一清

(华东师范大学通信与电子工程学院,上海 200241)

近年来,随着5G 技术的不断发展,超高清显示面临的高数据传输速率问题逐渐得到解决。视频技术正朝着超高清的方向发展[1],图像传感器作为超高清显示中的数据源,其产生的图像数据的正确采集对超高清显示至关重要。图像传感器的并行DVP 接口由于使用单端信号线传输,数据容易受到噪声的干扰,传输速率无法满足超高清的数据传输速率要求。因此,在高分辨率图像传感器中,均使用差分LVDS 信号线传输图像数据[2-5]。

文中设计了一套基于ZYNQ UltraScale+的高速图像数据采集系统,为图像传感器提供了100 路LVDS信号线,图像数据的采集速率可达160 Gb/s,满足超高清的数据传输速率要求。设计的系统使用国产的图像传感器LN130A 进行测试,系统的核心处理器通过对图像数据进行对齐、重排列使其变为可显示的图像数据,最终通过协处理器上的万兆以太网模块将图像数据传输到上位机,实现图像的显示。

1 硬件设计

1.1 系统硬件概述

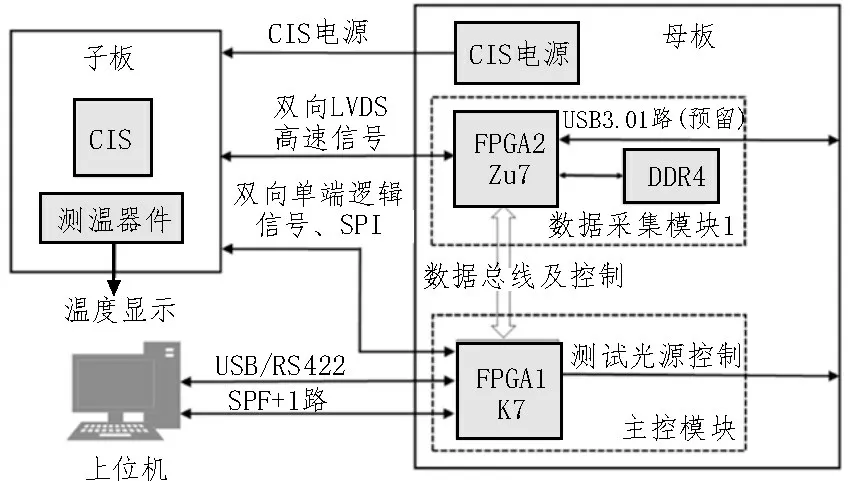

ZYNQ UltraScale+高速图像数据采集系统由母板、子板和上位机3 个部分组成。其中母板作为系统的核心部分用于完成图像数据的采集,为图像传感器提供驱动与控制信号,通过SFP+端口将采集到的图像数据传给上位机;子板上安装有图像传感器,通过QSH 系列高速座子将传感器输出的图像数据传给母板;上位机配有标准网卡,通过SFP+端口接收母板传来的图像数据,并由自行编写的上位机软件处理和显示图像数据。该系统采用子板、母板的设计实现了图像数据采集部分与图像传感器部分的分离。在采集不同图像传感器的数据时,只需要更换系统中的子板,增加了系统通用性的同时减小了更换图像传感器的开销。系统框图如图1 所示。

图1 系统框图

1.2 系统母板硬件设计

系统中的母板采用Xilinx的ZYNQ UltraScale+MP SoC系列的XCZU7EV-FFVC1156-2-E芯片作为系统的核心处理器[6]。此芯片主要包含PL(Programmable Logic,可编程逻辑)与PS(Processing System,处理系统)两个部分。其中PL 部分包含了504K 个可编程逻辑单元,1 156 个IO 管脚,能为图像传感器提供100 路LVDS 高速信号[7]。芯片上每一路LVDS 信号的数据传输速率最高为1.6 Gb/s,100 路LVDS 信号的数据传输速率可达160 Gb/s。PS 部分包含四核Cortex-A53 的APU(Application Processing Unit,应用处理单元)及双核Cortex-R5 的RPU(Real-Time Processing Unit,实时处理单元),PL 与PS 间通过AXI协议总线进行数据交互。采用此芯片作为核心处理器,其上的100 对LVDS 高速信号保证了数据采集速率,同时PS+PL 的架构也使母板上的软件开发变得多样,使软件开发更加灵活、高效[7]。

母板上的外围设计围绕核心处理器芯片的PL与PS 两部分展开,PL 部分包含前文提到的100 路LVDS 高速信号线,其通过高速信号座子与子板相连,处理器IO 口调试时使用的LED 灯、拨码开关、按键、4 路GTH 高速收发器及16路的LVDS高速信号与母板上的协处理器Kintex-7 相连。协处理器为图像传感器提供时序及控制信号,同时提供数据传输速率为10 Gb/s 的SFP+端口[8]与上位机进行数据传输,解决了核心处理器的SFP+端口IP 核需要付费使用的问题。PS部分包括4片8 Gb DDR4[9]@2 400 MHz高速缓存、一路SD2.0 接口、两片128 Mb QSPI Flash、一路USB3.0 接口、一路用于打印调试信息的USB 转UART 接口及LED 灯。母板设计以高速图像数据的采集和传输为主题,支持多种图像传感器。文中通过采集国产CIS(CMOS Image Sensor,CMOS 图像传感器)芯片LN130A 的图像数据,验证了系统用于高速图像数据采集的可行性。

1.3 CMOS图像传感器

LN130A 是一款分辨率为1 280×1 024,像素大小为9.5×9.5 μm2的具有高帧频、高动态范围的低噪声CMOS 图像传感器。该图像传感器可实现卷帘快门或全局快门。LN130A 的一些基本特征如下所示。

1)分辨率:1 280(列)×1 024(行);

2)像素大小:9.5×9.5 μm2;

3)卷帘快门时,帧频为160帧/s,读出噪声为1e-;

4)全局快门时,帧频为80 帧/s,读出噪声为3e-;

5)可实现高动态范围(≥90 dB);

6)积分时间可由外部调控;

7)共有4 路LVDS 图像数据信号通路,每一路的传输速率均为784 Mbps;

8)具有14 bit片上ADC;

9)具有SPI 接口,用于对寄存器进行设定。

下面以采集LN130A 图像数据为例,说明整个系统的软件设计。

2 软件设计

2.1 总体软件概述

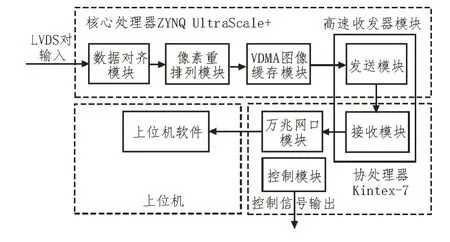

文中的高速图像数据采集系统的总体软件设计的功能框图如图2 所示。

图2 软件功能框图

CIS 芯片在接收到母板上控制模块产生的控制信号后输出图像数据,图像数据通过LVDS 接口输入到母板上的核心处理器,通过数据对齐模块确保多路LVDS 数据信号的数据位同步及像素同步。其后的像素重排列模块将4 路LVDS 信号上的以一定规律传送的像素数据按照像素0 到1 280 的顺序重新排列成一行图像数据。此模块还负责将重排列的图像数据转化为AXI4-Stream 格式,通过之后的VDMA模块缓存到DDR4 中。VDMA 图像缓存模块缓存3帧图像数据,使图像能够流畅显示。核心处理器通过高速收发器模块将缓存后的图像数据传给协处理器。协处理器上的万兆以太网模块将图像数据组成UDP 协议的数据包传到上位机,上位机中的软件负责接收和处理图像数据。

2.2 数据对齐模块功能说明

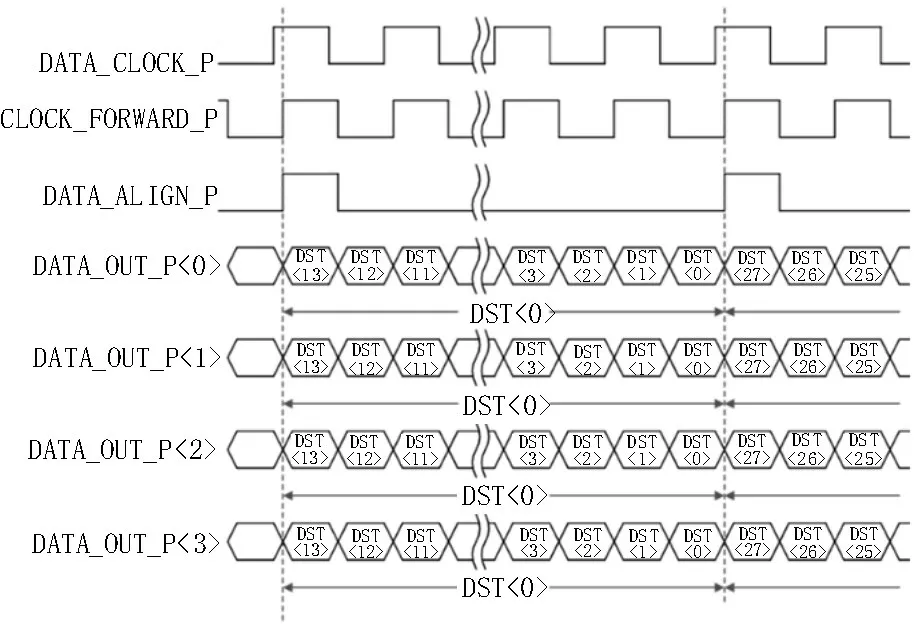

CIS 图像传感器输出数据时序图如图3 所示,这些信号之间有着严格的相位关系。

图3 图像传感器时序图

其中,DATA_OUT_P<0~3>为4 路数据信号,CLO CLK_FORWARD_P 为数据时钟,DATA_ALIGN_P 为像素同步信号。

2.2.1 数据位同步

数据对齐模块在接收到信号后需要使用核心处理器中的ISERDES 接口硬核[10],在数据时钟的边沿对数据及像素同步信号采样,并以1∶8 的比例将串行数据转换为并行数据。使用ISERDES 硬核采样前,还需使用核心处理器内的IODELAY 硬核调整上述信号的动态延时,确保信号间的相位关系与图3一致,得到正确的采样数据。

2.2.2 像素同步

在保证了数据的正确采样后,4 路数据信号和像素同步信号在ISERDES 内的串行并行数据转化环节也会存在不确定的延时,所以在数据同步模块内还需要对8 bit的并行数据进行拼接,得到正确的14 bit像素值。像素同步功能使用Verilog语言进行编写,首先将8 bit 的并行数据写入异步FIFO 并以14 bit 的形式读出并行数据,然后存入两级14 bit的寄存器中,之后用这两级寄存器中的数据排列出14 bit 数据的所有可能组合并与已知的目标序列对比,如图4 所示。

图4 像素同步过程

从图3 可知,文中系统中像素同步信号在像素同步时的已知序列为14 位的二进制数1000000000 0000(b),数据信号的已知序列为14 位的DST<0>,并可以用其后接收的已知序列DST<1>检验像素同步的正确性。完成数据位同步及像素同步后的一行图像数据的时序图如图5 所示,其中X_CLOCK 为辅助说明信号,便于读者理解此模块的输出时序,其频率为28 MHz。在一个X_CLOCK 周期内,数据对齐模块将输出8 个像素值(注:每个像素值均为14 bit)。

图5 行像素时序图

2.3 数据重排列模块功能说明

参照图5,数据对齐模块的4 路14 bit 并行数据的输出形式为DATA_OUT_P<0>上传输第N及N+1个像素的值,DATA_OUT_P<1>上传输第N+2 及N+3个像素的值,DATA_OUT_P<2>上传输第N+4 及N+5个像素的值,DATA_OUT_P<3>上传输第N+6 及N+7个像素的值,0≤N≤1 272。为了显示图像,一行图像数据的像素值需要按照0~1 279 的顺序重新排列。数据重排列模块首先将4 路14 bit 并行数据拼接为一个56 bit 的数据存入异步FIFO 中,然后以112 bit的形式读出数据,存入相同位宽的寄存器中,最后通过位拼接操作完成像素值的重排列,如图6 所示。

图6 数据重排列过程

2.4 VDMA图像缓存模块功能说明

系统中PL 端为了提供100 路的LVDS 数据接口,没有足够的管脚连接DDR4 存储芯片。用于缓存图像数据的DDR4 缓存器挂载在PS 端,因此需要使用Xilinx 公司提供的VDMA IP 核[11-12]将重排列后的图像数据缓存到DDR4 中。VDMA 图像缓存模块的主体是VDMA IP 核,其为AXI4-Stream 总线形式的数据流提供了两个DMA 通道,使PL 端的图像数据能方便高效地缓存到PS 端的内存中,防止图像出现卡顿及割裂现象。

数据重排列模块输出的图像数据首先需要转化为AXI4-Stream 总线形式,与VDMA IP 核的数据接口形式匹配。VDMA IP 核的寄存器主要用于设置缓存帧的起始地址及图像行、列像素个数。文中系统使用核心处理器PS 端的AXI4-Lite 总线配置VDMA IP 核的寄存器。

2.5 高速收发器模块功能说明

高速收发器模块的主要功能是将缓存后的图像数据从核心处理器传送到协处理器,从而通过协处理器上的万兆以太网模块,将图像数据传递到上位机进行显示及处理。此模块分为核心处理器内的发送模块及协处理器内的接收模块。

2.5.1 发送模块

核心处理器在硬件上通过GTH收发器[13]与协处理器相连接,发送模块使用Xilinx公司的GTH IP核发送数据。GTH收发器在Ultrascale+架构中支持500 Mb/s到16.375 Gb/s 的单通道速度,与PL 逻辑资源紧密集成。文中系统将GTH 发送器的速率设置为5 Gb/s,采用8/10 bit 的编码方式对发送的并行数据进行编码以降低发送信号中的直流成分,接着将并行数据转化为串行数据,以差分对的形式将数据发送出去。

2.5.2 接收模块

协处理器在硬件上通过GTX 收发器[14]与协处理器相连接,接收模块使用Xilinx 公司的GTX IP 核接收数据。GTX 收发器在7 系列FPGA 中支持500 Mb/s到10.312 5 Gb/s 的单通道速度。文中系统将GTX 接收器的速率设置为匹配的5 Gb/s,对接收数据进行解码,接着将串行数据转化为并行数据,最后对并行数据进行像素对齐得到正确的图像数据。

2.6 万兆以太网模块功能说明

万兆以太网模块以10 Gb/s的速率将图像数据传输到上位机,文中系统使用Xilinx 公司的万兆以太网子系统IP 核[15]实现万兆以太网功能。此IP 核提供给用户的数据接口为AXI4-Stream 总线形式,数据位宽为64 bit,用户时钟为156.25 MHz,时序如图7所示。

图7 万兆以太网IP核用户接口时序

为了减小协处理器与上位机通信时发送数据前的延时,文中系统将图像数据组成UDP用户数据报,并以AXI4-Steam的形式将数据流传入万兆以太网子系统IP核的用户接口中,使其以10 Gb/s的速率与上位机通信。

2.7 上位机软件功能说明

上位机软件基于微软的WPF(Windows Presentation Foundation)[16]进行界面设计,实现的功能有:1)将接收的14位像素值数据转换为8位,并以bmp格式显示图像;2)统计显示图像中的像素值(8 bit图像数据),并以直方图的形式将结果实时显示;3)调节图像的亮度及对比度;4)放大显示选中图像区域内的原始14 bit像素值;5)以TIF 格式存储图像;6)录制视频。

3 测试及验证

文中系统通过控制模块的SPI 接口信号修改LN130A 芯片内寄存器的值,使其产生分辨率为1 280×1 024、80 帧/s 的灰阶图像数据,从而进行系统的图像数据采集测试,最终的图像数据传递到上位机拼接成灰度图像进行显示。

4 结束语

文中以Xilinx 公司的ZYNQ 作为核心处理器,设计高速图像数据采集平台,采样速率可达160 Gb/s。从软硬件两方面现实了基于并行LVDS 接口的图像传感器的数据采集。文中系统采用子、母板的设计方式实现了图像数据采集部分与图像传感器部分的分离,通过更换子板实现多种图像传感器的数据采集,具有通用性,也降低了更换图像传感器时的开销,为并行LVDS 接口的图像传感器的图像数据采集提供了一个可行的解决方案。