基于CMOS 高密度微电极阵列芯片的研究与设计

2022-04-20李丹凤高超嵩孙向明

李丹凤,高超嵩,孙向明

(华中师范大学物理科学与技术学院,湖北武汉 430079)

为了充分掌握大脑的意识活动,科学家与工程师一直在寻找并探索意识活动的起源与机制。神经网络的高度连通性和协调的电信号活动被认为是大脑能够处理高度复杂信息的原因[1]。为了研究其工作机制,传统采用光学仪器的检测方式效果较差[2]。为了能够深入的探索神经信号的特性,科学家们研制出了多种技术,例如膜片钳[3]、细胞染色技术[4]。随着科学的发展,需要对神经细胞进行长时间、无伤害以及多次多方面检测时[5],上述方案目前也难以解决。最近几年,互补金属氧化物半导体[6](Complementary Metal Oxide Semiconductor,CMOS)的提出,上述场景的实现变得可行化。将微电极阵列(Micro-Electrode Array,MEA)[7-11]用CMOS的形式实现,将电极与信号处理集成在一起,可以记录神经细胞的状态以及信号的传输。

文中提出了一种检测神经信号的高密度微电极阵列芯片,用于活体组织或者体外培养的神经组织刺激后,进行信号的记录。将非侵入性电极与模拟前端电路集成在一块芯片上,有利于提高模拟-数字转换等信号处理模块的信噪比,有利于提高芯片移植入脑的可行性,使得神经细胞信号的记录更具真实性。

1 系统结构

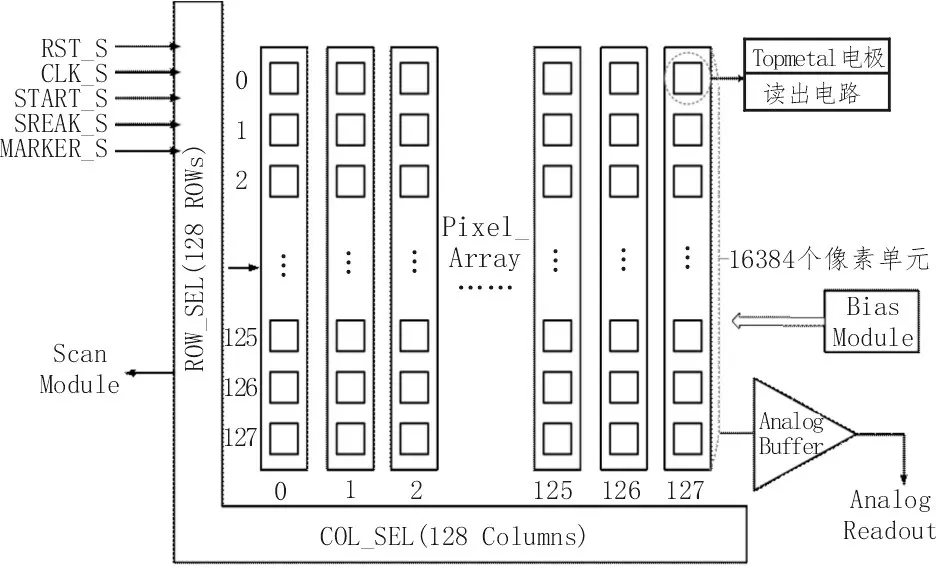

高密度微电极阵列(MEA)芯片结构框图如图1所示,其主要是由16 384 个像素单元、Scan Module、Analog Buffer、偏置Bias Module 等部分组成。像素单元可以刺激测试细胞,使其产生电位变化,读出其电位,并通过片内集成的Scan Module、Analog Buffer 读出电位信息。每个像素模拟输出后接行开关,一列像素最下端接列开关,通过Rolling-Shutter 的读出结构,依次打开一行像素,在该行开关打开时,依次打开每一列的列开关,依次将每个像素记录电位信息发送至模拟驱动电路,将像素中的模拟电压值读出至芯片外。

图1 高密度微电极阵列芯片结构框图

2 电路设计

2.1 像素单元工作原理

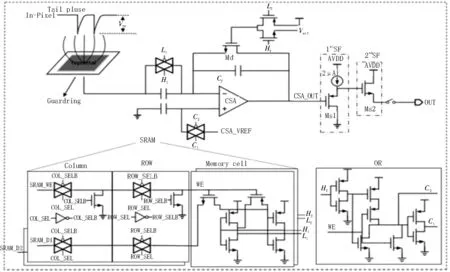

高密度微电极阵列(MEA)芯片中单个像素的原理框图如图2 所示,其中包含电极(Topmetal)[12]、电荷灵敏放大器(CSA)[13]、传输门、两级源跟随电路、5bit SRAM 电路以及或门。电极用于收集电信号,收集的电荷量通过电荷灵敏放大器放大后输出,经两级源跟随后通过行列开关控制输出。SRAM 电路可控制传输门的通断,以实现刺激与记录电位两种不同的工作模式:当传输门全闭合时,运放构成源跟随器,使得电极具有CSA_VREF 提供的电压值,给测试细胞以电压刺激;当传输门打开时,电路恢复成电荷灵敏放大器的模式,记录测试细胞的电位,以此记录测试细胞在电压刺激下产生的电位变化。

图2 单个像素的原理框图

2.1.1 电 极

电极主要是通过将像素阵列中单个像素点上的中心金属暴露出来形成的;电极与内部电路相连,当外部电荷发生变化时,电路会将该物理信号转换成为电信号。裸露电极感应到电信号后,通过电荷灵敏放大器将当前的微弱信号进行放大,得到脉冲信号,可通过缓冲器以模拟形式输出至外部示波器进行观察,或可通过数字处理后输入至FPGA 再进行处理与分析。

2.1.2 电荷灵敏放大器(CSA)电路

电荷灵敏放大器(CSA)主要是运用在高能物理离子探测器的过程中,粒子通过探测器产生电信号。其设计结构如图3 所示,主要组成部分是密勒积分器[14],它拥有输出电压幅度稳定、较高的信噪比等优点。反馈电容Cf连接在放大器的输入与输出之间,从而构成一个负反馈电路。Rf为反馈电阻,它不仅可以泄放Cf上积累的电荷(泄放时间常数τf=Cf×Rf),还可提供一个直流通路,从而使得CSA电路中运放的静态工作点保持稳定。

图3 电荷灵敏放大器的基本模型

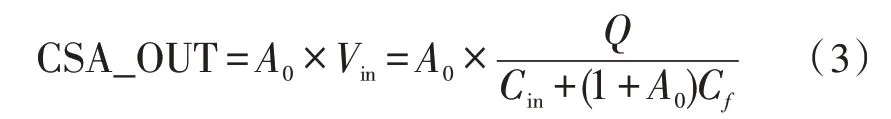

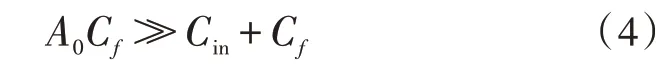

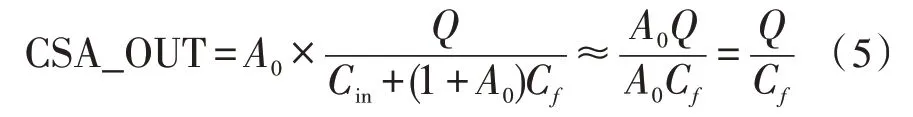

其反馈电容Cf折合到输入端,可由密勒效应得到,总的输入电容为:

输入电压幅度为:

输出电压幅度为:

当A0足够大时,使得:

则输出幅度可以近似为:

从式(5)可知,当A0Cf≫Cin+Cf时,只要Cf是恒定的,不管Cin、A0是否稳定,输出电压CSA_OUT与输入电荷Q都成正比关系。而反馈电容Cf的改变同时对整体电路的灵敏性也发生变化,同时其容值的选取也与噪声相关,容值小,噪声小,若容值过小,则会影响输出的稳定性,所以综合考虑,进行折中选择。

反馈电阻Rf主要是泄放积累在电容Cf上电荷量。由于需要较大的阻值,为防止像素面积过大,利用MOS 管的特性,使其工作在线性区充当电阻的作用,其导通电阻为:

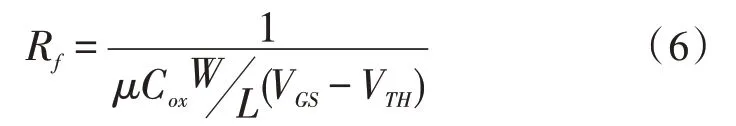

2.1.3 两级源跟随

像素的CSA 将电极收集的电荷转换成模拟电压后,需要通过外部的读出电路进行输出的读出。为了保证所有像素CSA 的输出稳定可靠,源跟随电路是必不可少的。图4 是源跟随电路结构图。两级源跟随的设计方案采用经典源跟随电路结构[15]:第一级为P管跟随,其静态工作电流利用像素阵列中的偏置电路使其静态工作电流保持2 μA,从而可以提高CSA 输出的稳定性;第二级釆用N管跟随,主要通过阵列中SCAN 模块进行控制,以保证读出过程中能够依次独立地选择到每一个像素,其工作电流通过阵列共享的N管电流镜在芯片外部设置。从版图中可以得出第二级的驱动电路较多、金属走线过长,从而产生了大容量的负载工作电流,其相比第一级要大很多,当前电路的典型值为20 μA。

图4 源跟随电路结构图

2.1.4 SRAM模块

5-bit SRAM 存储像素阵列的开关数据。单个SRAM 单元采用6 管结构,该结构会增加电路中的静态电流,SRAM 数据的写入控制通过WE 引脚进行操作,当WE 引脚为高时功能有效。SDRAM 只有当阵列的行列选择信号以及WE 使能有效时,SRAM 内部数据才会被刷新,其时刻均保持原来数据不变。

在传统6 管的结构上,对存储单元进行了改进,如图5 所示,M6 的漏极不是直接连到SRAM_Q 上,而是通过晶体管M5 连接,晶体管M5 导通时,会切断输出信号SRAM_Q 和输入信号D,避免写入存储单元时,SRAM_Q 和D 之间的竞争,这个存储单元是在没有读取启用的情况下设计的,是直接驱动负载,当M6 导通时,数据写入。

图5 SRAM电路结构图

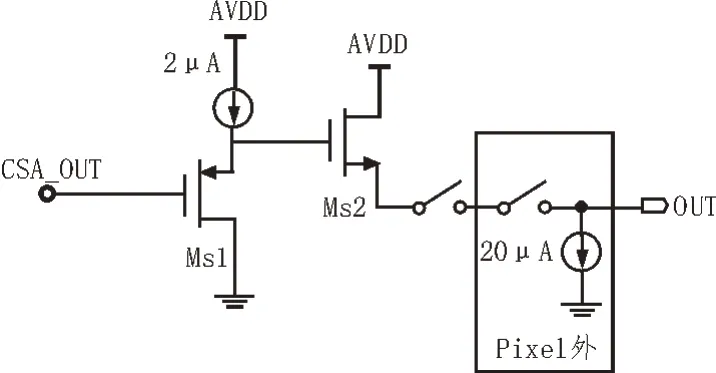

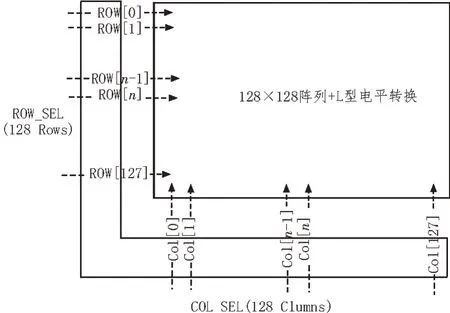

2.2 行列扫描模块工作原理

高密度微电极阵列(MEA)芯片的像素是128行×128 列。行列扫描(Scan)模块产生COL<0:127>,ROW<0:127>的开关信号,扫描到某行某列时,输出该像素内的模拟信号。

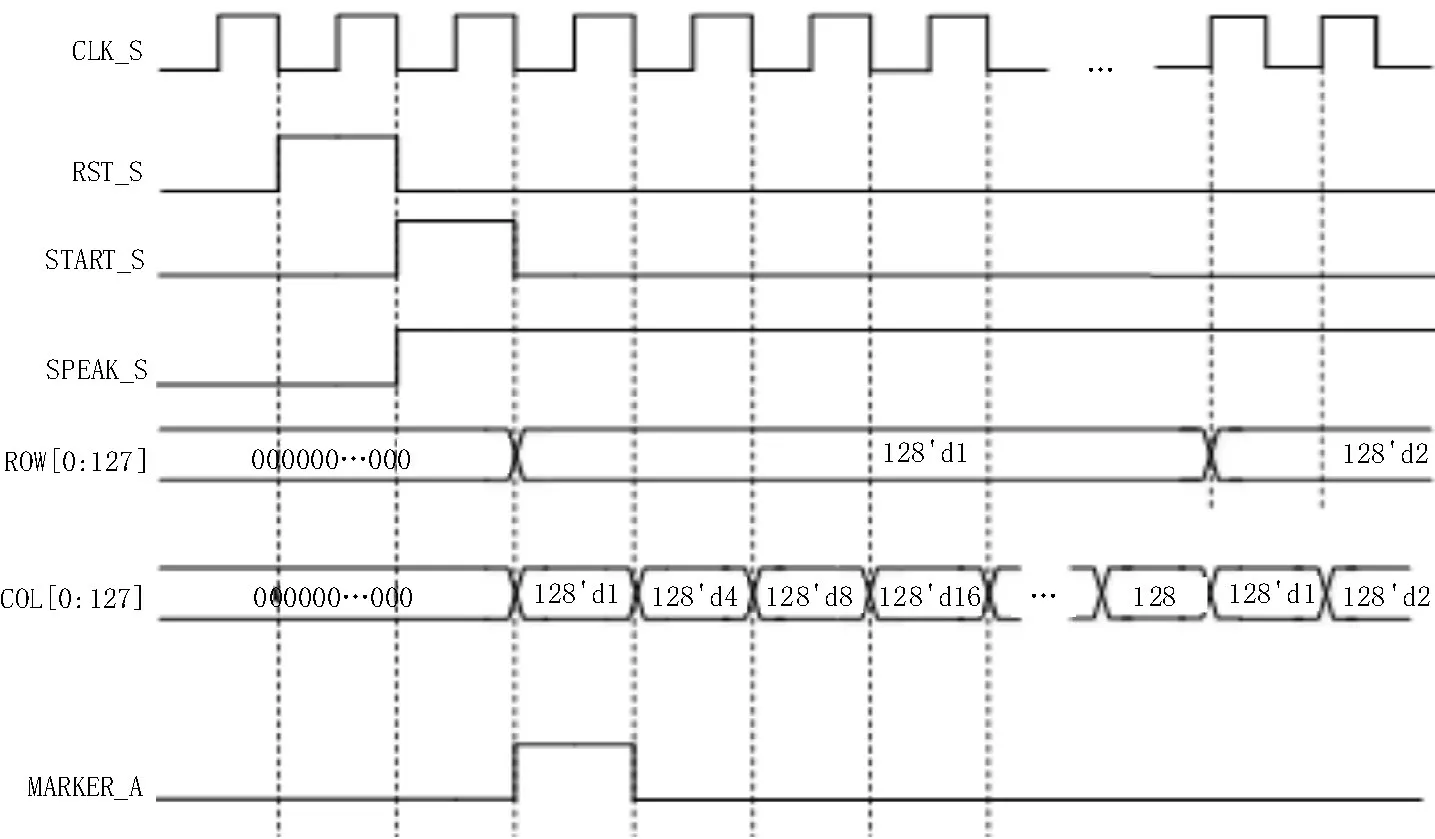

Scan 模块信号框图如图6 所示,“L”型放置于芯片的左下边缘成半包围的结构。输入端共有一个时钟信号,3 个控制信号,输出为1 位标志位信号和行列扫描控制信号。时钟信号CLK_S 频率范围在1~40 MHz 之间才能有效的驱动该模块,时钟高电平为1.2 V,低电平为0 V;RST_S 为异步复位信号,高电位有效;START_S 为像素扫描起始信号,单脉冲高电位有效;SPEAK_S 为状态切换信号,当该信号为高电平时,为扫描状态;低电平时,扫描停止在当前像素。信号之间的时序如图7 所示。

图6 Scan模块整体布局

图7 Scan模块时序图

MARKER_A 为标志信号,每次扫描到像素阵列的第一个像素时,输出一个脉冲信号,宽度为一个时钟周期,每出现一次该信号,说明芯片扫描完成一帧。时序图根据仿真结果计算得到,在实际测试过程中,复位信号可适当增长,START_S 和SPEAK_S信号也可在复位信号结束后几个周期再启动,确保系统能够正常工作。

3 版图设计与仿真

3.1 电极的版图结构

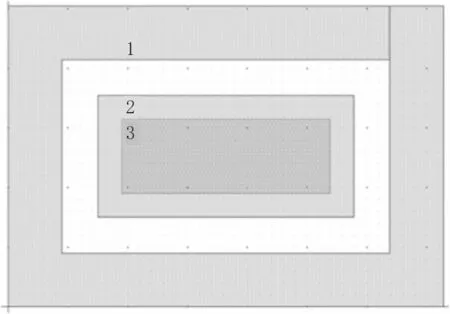

单个像素电极的版图结构如图8 所示,整体面积是36.5 μm×25.5 μm,其中,标注1是保护环Guarding,与Topmetal 电极距离为3 μm(工艺允许的最小间距),环绕Topmetal 一圈,采用顶层金属MTT 层;标注2 是Topmetal 电极,面积是21.4 μm×10.3 μm,为顶层金属MTT 层;标注3 是电极开窗,位于电极中心区域17.4 μm×6.3 μm 的部分,利用PA 层开窗后形成的裸露电极,用来收集电荷。

图8 单个像素电极版图结构

Guardring 与Topmetal 电极是彼此互不相关的,二者之间会产生电势差,从而在电极周围会形成一个电场,在电场的驱动下,会将更多的电荷收集到像素点上,从而提高电荷收集效率以及信号变化强度。

3.2 电荷灵敏大器之反馈电容版图结构

由式(5)可知,反馈电容的值决定电荷灵敏放大器的灵敏度以及噪声的大小,折中考虑后其容值选择为10 fF。反馈电阻是用工作在线性区的MOS 管替代的,利用版图中引伸出两层金属走线,层数之间增加一个10 fF的反馈电容,提高了灵敏度与信噪比。

对单个像素的版图不断寄生提取与优化,从而提升CSA 的电路性能。反馈电容与反馈电阻部分版图如图9 所示。

图9 反馈电容与反馈电阻部分版图结构

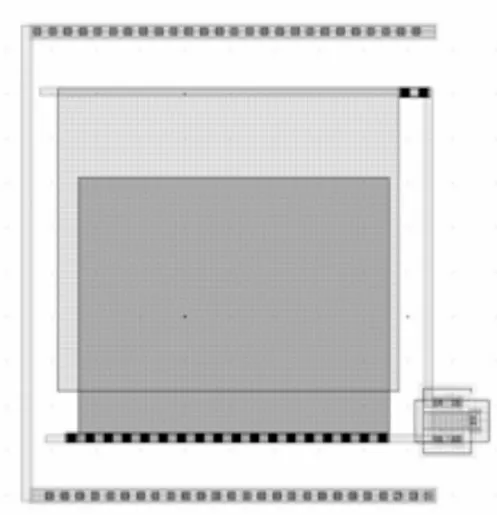

3.3 芯片的整体版图结构

该芯片采用的是华虹宏力CMOS 130 nm 工艺,版图加上IOPAD 后的面积是5.8 mm × 4.2 mm,包含181 个引脚分布在芯片的四周,版图如图10 所示,并在图中放大其中4 个像素。

图10 高密度微电极阵列芯片整体版图

3.4 仿真验证

利用Cadence、Spectre工具进行后仿真验证,版图的仿真波形如图11所示。当输入的电荷数是1 K库仑时,理论值的计算是16 mV,输出的幅度是11.79 mV。且得到等效电荷噪声ENC为27e-,上升时间为1 μs。

图11 版图的仿真波形

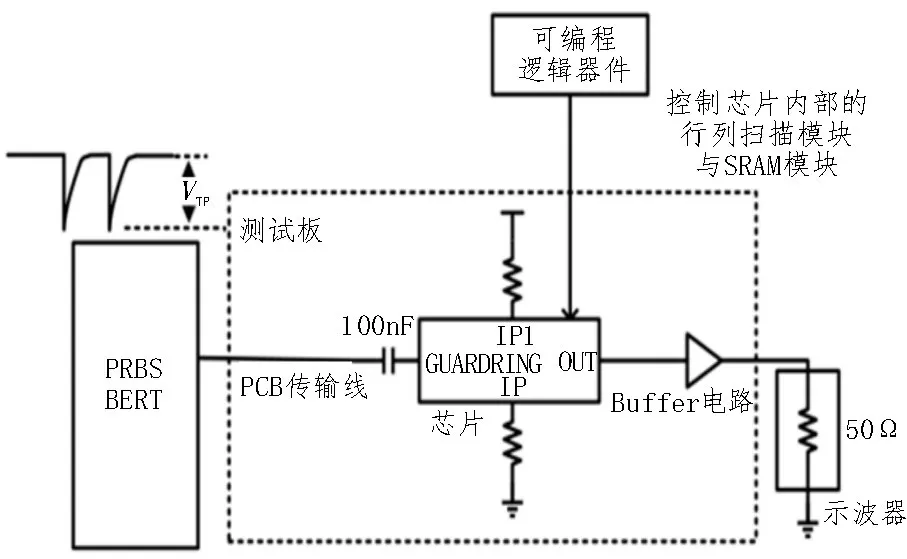

4 芯片电学测试

高密度微电极阵列芯片已完成流片工作,并已经完成印制电路板(PCB)设计,且完成了芯片的性能测试,通过显微镜可以查看该芯片的外观图,如图12所示。图13为芯片测试框图,信号源伪随机码序列[16](PBRS)BERT 为芯片提供下降幅度为4 mV 的输入信号,通过可编程逻辑器件,为芯片提供所需的参考电压,示波器内部是50 Ω的电阻。基于此,观察输出信号,输出信号如图14 所示。

图12 芯片在显微镜下的实物图

图13 芯片电学性能测试框图

图14 输出信号结果图

5 结论

该设计采用商用GSMCR CMOS 130 nm 工艺,设计了一款高密度微电极阵列芯片,后仿真结果表明,各项指标均达到预期。等效电荷噪声ENC 为27e-,上升时间为1 μs;像素面积为36.5 μm×25.5 μm。该芯片实现了16 384 个读出通道的技术可行性,可用于高空间分辨率的神经元网络活动记录。文中设计的这款高密度微电极阵列芯片可以在不同波形、振幅和持续时间刺激的情况下测试细胞,并记录其电位变化。通过细胞外记录,评估体外细胞的行为,筛选药物或检测有害物质。