基于大功率可控硅芯片SCR的失效分析研究*

2022-01-06张凯虹万永康

王 敦 张凯虹 万永康

(中国电子科技集团公司第五十八研究所 无锡 214035)

1 引言

多功能、微型化以及集成度高的芯片已经成为发展趋势,由于使用环境要求越来越高,芯片失效率也逐年增加,电子产品的可靠性逐渐成为质量管理的焦点。失效分析技术是一门发展中的新兴学科,在国外主要应用在汽车电子、航空电子等高科技技术领域,需要结合物理、金相和化学等多学科交叉进行分析。利用失效分析技术可以管控电子元器件质量,提高电子元器件以及电子控制系统的可靠性[1]。在产品研发和生产整个项目生命周期各个环节都可能发生产品失效等问题,20世纪初,汽车工业首先将失效分析技术FMEA作为对汽车电子设计和生产制造的质量评审一部分[2]。随后,1993年,美国质量汽车工业协会制定了失效分析技术FMEA第一版本手册。随着汽车电子技术的发展,FMEA被细分为设计阶段的DFMEA和生产阶段的PFMEA[3]。这就为电子产品失效分析提供了技术支持,PCB已经成为电子信息产品的最为重要的一部分,但是由于设计和工艺的原因,PCB在生产和应用过程中存在大量的失效问题。其中大功耗的可控硅芯片SCR已经是PCB上失效频率最高的元器件[4]。本文基于PCBA主控板上可控硅芯片SCR进行失效分析,通过I-V电学复测、X-Ray射线、C-SAM超声以及SEM等失效分析测试设备,确定器件失效的模式,分析造成器件失效的机理,定位失效点并查找失效原因,并提出设计优化建议。为PCBA电控板可靠性设计与失效分析提供了一定的参考依据。

2 案例背景分析

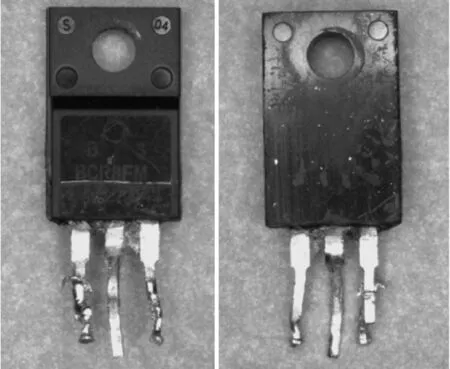

根据用户提供失效信息,该器件为PCBA主控板上可控硅芯片,在整机使用过程中失效,经拆机确认T1和T2端口短路失效,且PCB板上无其它元器件失效现象,SCR器件如图1所示。通过对失效器件进行电学测试、物理和化学试验,确定器件失效的模式,分析造成器件失效的机理,定位失效点并查找失效原因,为电路设计优化,提高电子产品可靠性具有十分重要的作用。芯片失效分析流程主要包括外观检查、电学复测、X-Ray射线测试、超声C-SAM测试,开封测试,去层分析等[5]。

图1 双向可控硅芯片SCR实物照片正面(左)及反面(右)

3 测试结果与分析

3.1 器件外观检查与分析

对失效器件进行外观检查,如图1所示,器件从PCBA板上解焊后,表面存在残留的胶体,引脚处存在多余的锡焊料。与良品对比,失效样品表面标识清晰,器件封装结构正常,未见破损、凸起、裂痕等明显异常形貌。

3.2 器件电学参数测试与分析

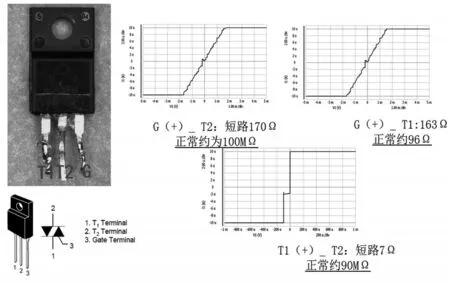

对器件进行电学参数复测,分别测试主电极和控制极之间电性能参数,检查T1、T2和G极间是否存在功能异常现象,如图2所示。可由I-V特性曲线图看出,在+/-0.2V区间内,失效样品呈现出阻性,与正常器件对比,I/V变化曲线超过30%不同。同时,对地电阻测试结果如表1所示,G(+)→T2电阻值为170Ω,T1(+)→T2电阻值为7Ω,而正常器件电阻值在MΩ级别,TR1器件G和T1电极均与T2电极短路,说明器件内部损坏[7],为了进一步研究失效结果,确定失效的位置。对芯片进行无损X-Ray射线测试。

图2 SCR器件电学I-V测试结果

表1 功能正常与异常器件电学参数测试结果

3.3 器件X-Ray射线测试与分析

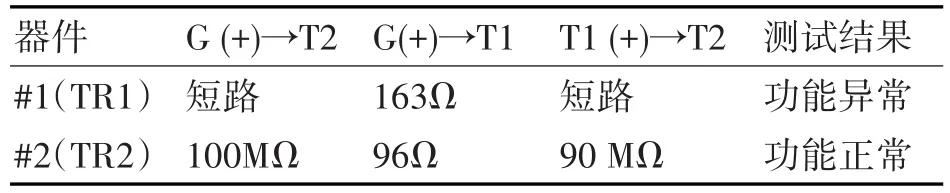

对失效器件进行X-Ray射线测试,由图3可知,封装内部框架清晰,无异物粘结,芯片结构完整,芯片DIE与基底之间的粘结料存在溢出现象,主要是在贴片DIE工艺时,粘结料溢出导致,根据法规标准要求,并不影响器件功能[8]。

图3 失效器件X-Ray测试结果俯视图(左)和侧视图(右)

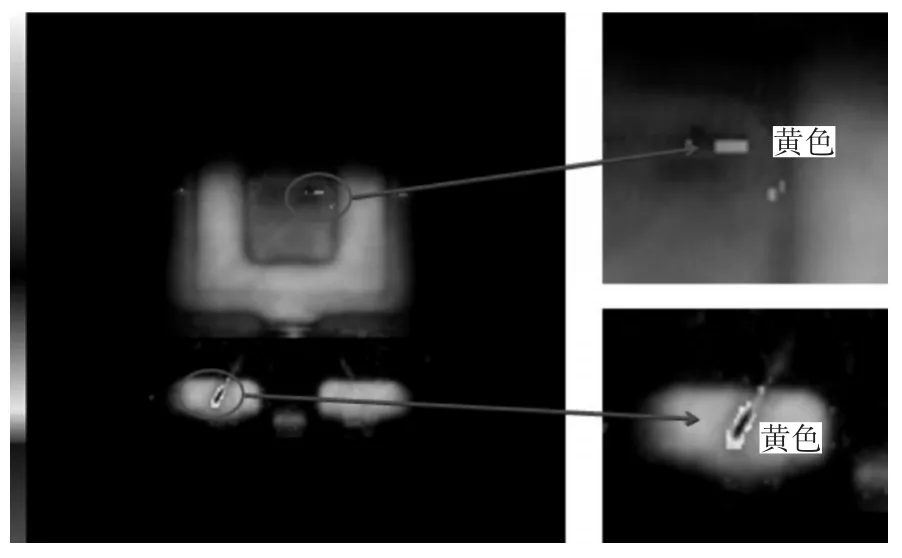

3.4 器件C-SAM超声测试与分析

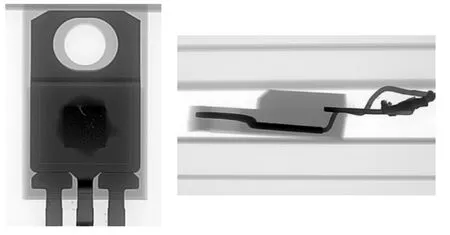

为了进一步确认器件内部是否存在缺陷,检查引线键合和芯片是否存在分层、模塑化合物的空洞和裂纹、引线框架以及芯片的粘接区域缺陷,采用超声C-SAM扫描测试分析[9]。测试结果见图4,图中黄色区域表明,SCR器件芯片键合丝区域的引脚出现异常。芯片的引线键合区主要受到引线焊接材料稳定性不足以及容易氧化、硬度和弯曲度变化等影响[10]。

图4 失效器件超声C-SAM测试结果正视图(左)和放大图(右)

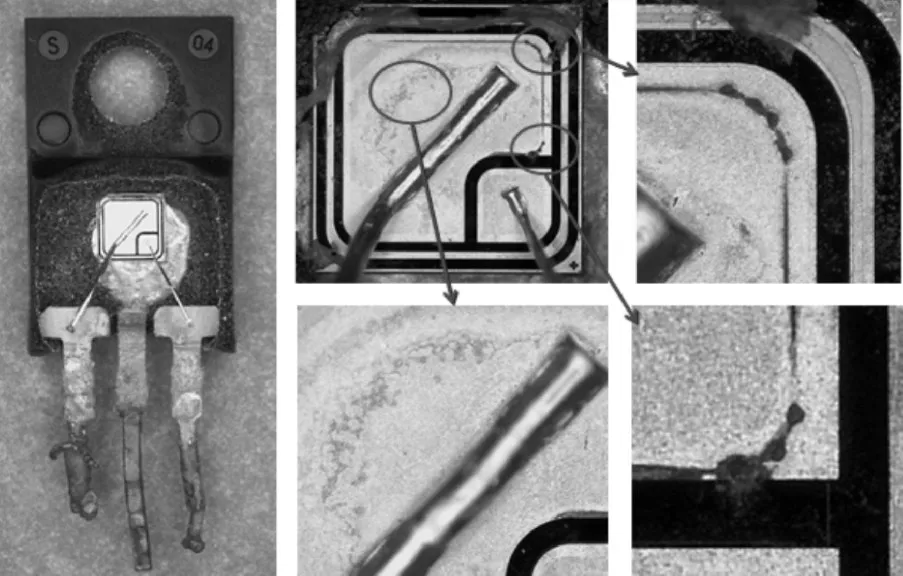

3.5 器件开封测试与分析

对器件无损开封后进行内部检查,检查内部材料、结构是否存在缺陷,内部引线键合丝是否损伤,内部芯片是否存在破损、腐蚀、过电压击穿或过电流过热等异常形貌[11]。测试结果见图5,对失效样品进行化学开封,暴露出芯片DIE以及键合引线,在光学显微镜下观察,芯片采用的键合丝是硅铝丝,开封后保留完整,未见到脱落损坏等现象。芯片表面边缘存在烧毁等异常形貌。说明器件使用过程中受到过压或过流过热等应力冲击[12]。

图5 失效器件开封测试结果正视图(左)和放大图(右)

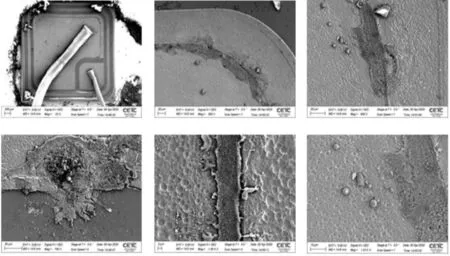

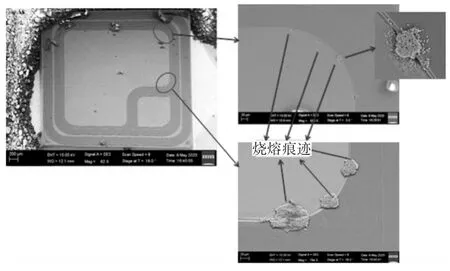

3.6 器件开封后SEM测试与分析

下面通过SEM电镜测试观察,进一步对芯片内部进行分析。如图6所示,芯片表面及边缘有黑色物质,芯片表面T1电极附近出现烧熔痕迹,且伴随有圆形坑状形貌。对器件化学腐蚀掉表面金属电极,去掉钝化层后,可以观察到PN结交界处有热熔等异常形貌[13]。此外芯片表面的其它区域未见有明显的异常和缺陷,如图7所示。

图6 失效器件电镜S4EM测试结果

图7 失效器件去层后表面测试结果

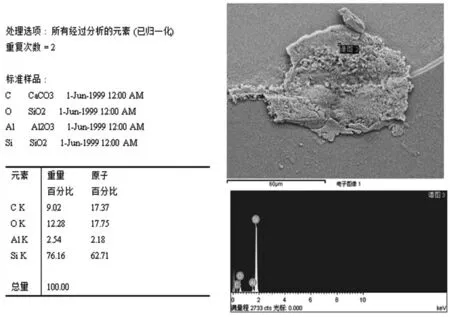

根据能谱EDS分析,见图8,测试结果显示芯片烧熔处主要成分为Si,O还有少量AL。芯片烧熔区域混合有SiO2塑封填充料成分,结合熔融形貌,判断金属和塑封料中球状SiO2颗粒出现高温互溶现象[14]。通过对器件进行外观检查、X射线检查、无损开封、内部目检试验后得出以下结论,该器件T1和T2两端电极短路,可能由于过电应力引起芯片出现局部烧熔后导致失效[15]。芯片内部的烧痕斑点主要出现在PN结相邻区域,当芯片输入端受到过电应力时,正常门极触发导通,导通区域不能迅速扩展,门极区域局部温度将快速升温,由于硅材料的比热容和热传导率都比较小,当输入端的电流上升率迅速过大,PN结交接处就会因为过度的局部温升而产生的热量烧毁[16]。由瞬态过电应力破坏器件的温度主要集中在1100℃~1300℃之间,温度低于硅熔点(1412℃)。这主要由两种因素造成:其一是在导通区和未导通区之间存在很高的温度梯度,能使硅片局部受到的热应力作用,造成硅片损坏;其二是,当温度超过600℃时,与硅片接触的金属电极就会与硅产生熔融的混合体,使器件发生短路。综合以上分析结果可知,可控硅芯片内部的损伤主要是过电应力瞬间冲击下导致。造成芯片过电失效的原因有很多,在PCB电路设计中,尽量减少电源本身所产生的干扰源对可控硅芯片造成的损伤,利用抑制干扰的方法或产生干扰较小的元器件和电路,并进行合理布局;其次是通过接地、滤波、屏蔽等技术抑制电源的EMI,主要包含以下设计:1)较少dv/dt和di/dt(降低其峰值、减缓其斜率);2)压敏电阻的合理应用,以降低浪涌电压;3)阻尼网路抑制过冲;4)采用软恢复特性的二极管,以降低高频段EMI;5)有源功率因数校正,以及其他谐波校正技术;6)采用合理设计的电源线滤波电器。

图8 芯片DIE表面成分EDS测试结果

4 结语

本文针对PCBA主控板上可控硅芯片SCR进行失效分析,通过I-V电学复测、X-Ray射线和C-SAM超声以及SEM等失效分析测试设备,确定器件失效的模式,分析造成器件失效的机理,定位失效点并查找失效原因,并提出设计优化建议。为PCBA电控板可靠性设计与失效分析提供了一定的参考依据。