基于ZYNQ的机载SAR实时回波仿真研究

2021-11-17赵文达

赵文达,韩 松

(1.中国科学院空天信息创新研究院,北京 100094;2.中国科学院大学,北京 100049;3.中国科学院电子学研究所,北京 100190)

1 引言

合成孔径雷达(Synthetic Aperture Radar,SAR)是一种全天时、全天候的主动式微波遥感成像雷达,与传统光学成像技术相比具有穿透云、雾、雨的能力以及不依赖光源等优点,在地形图像生成,目标检测识别与分类等领域用途广泛[2]。在实验室条件下为了优化机载合成孔径雷达的设计步骤、降低硬件设计成本、简化系统的设计难度,通常是模拟机载合成孔径雷达真实的工作环境,将仿真器与待测雷达组成一个完整的环路,利用半实物仿真测试(Hardware-In-Loop Simulation,HILS)的方法来验证成像雷达是否达到设计要求。

针对机载合成孔径雷达的仿真,文献[1]对SAR回波信号仿真的电磁散射理论与计算机软件实现方法进行了原理性阐述。文献[4]对比分析了目前若干成熟的回波仿真算法,比较典型的有距离时域脉冲相干方法(Range-Time Pulse Coherence,RTPC),距离频域脉冲相干方法(Range-Frequency Pulse Coherence,RFPC)以及二维快速傅里叶变换方法(Two-Dimension Fast Fourier Transform,2D-FFT)。

关于回波仿真算法实现的硬件平台,现场可编程门阵列(Field Programmable Gate Array,FPGA)通过硬件描述语言综合生成相应的寄存器级电路,可快速重配置于需要并行处理与硬件加速的应用。文献[3]提出了一种高层次综合的方法,将FPGA的硬件加速应用到SAR回波仿真。ARM(Advanced RISC Machine)是运行精简指令集的微控制器芯片,通常作为嵌入式微处理器应用于便携式设备中并提供软核与硬核解决方案。本文算法落地平台采用赛灵思推出ZYNQ异构SoC FPGA芯片,结合了两种集成电路的优势,并且通过基于AMBA协议的AXI总线实现PS-PL(Process System-Programmable Logic)之间的高效互联。

针对上述回波仿真算法与硬件实现中存在的软件与数字信号处理衔接实时性差的问题,本文从高性能回波仿真算法实现以及时域和频域仿真技术两方面进行研究,弥补SAR实时回波仿真器研制中的不足。基于以上分析,本文的设计针对实际机载合成孔径雷达的仿真需求,在对多种回波仿真算法深入研究的基础上进行优化,结合ZYNQ异构平台的特点设计具有较高工作效率的回波仿真器,并得到回波仿真器的相应实验结果,最后对机载SAR回波仿真器地实验结果进行了进一步的分析与论证。

2 回波仿真算法

2.1 回波仿真算法与优化

合成孔径雷达通过载荷平台与目标之间的相对运动,完成对目标区域的扫描,沿方位向接收目标反射的回波信号,由后端设备进行数据存储及处理,成像处理器通过对距离向脉冲压缩和方位向匹配滤波二维处理以及距离徙动校正后可以获得高分辨率图像[1]。

合成孔径雷达接收与发送信号均为线性调频信号,所接收信号可表示为

(1)

其中,A0为表示幅度调制的复常量,x表示距离向位置,y表示方位向位置,yc为波束中心偏离位置,f0为雷达中心频率,Kr为距离向线性调频率,R表示雷达与目标之间的斜距,wr与wa分别表示距离向与方位向的包络。由式(1)可以看出,SAR回波信号仿真中有两个关键点:一是方位向回波信号要保持满足多普勒相位函数的相参关系,二是由于距离徙动导致方位向回波信号要沿距离向发生偏移。由此所对应的即是合成孔径雷达仿真技术的频域仿真与时域仿真。

从算法流程层面上分析,RTPC算法符合真实合成孔径雷达的工作方式,RFPC算法从一维频域的角度对回波信号进行叠加,但二者实现效率不高;2D-FFT算法从卷积角度将点目标冲激响应与整个二维后向散射系数矩阵进行处理,如式(2),无论是在算法效率还是存储优化上均有较大提升,本文针对二维面目标回波仿真算法,给出了通过快速傅里叶变换改进的算法。

s(x,y)=g(x,y)⊗h(x,y)+n(x,y)

(2)

其中,s(x,y)为目标模型基带信号数据,g(x,y)为后向散射系数矩阵,h(x,y)为单位幅度点目标冲激响应,n(x,y)为噪声矩阵。

通过快速傅里叶变换,将时域卷积变换至频域相乘,表示为如下形式。

s2dfft=IFFT(FFT2(g(x,y))·FFT2(h(x,y)))+n(x,y)

(3)

式中采用的二维傅里叶正变换可以表示为

(4)

相应的,二维傅里叶变换的逆变换可以表示为

(5)

关于本文所采用的2D-FFT回波仿真算法,其流程如下所述。

算法1:2D-FFT

1)初始化雷达参数与环境参数;

2)加载目标区域的后向散射系数矩阵;

3)计算得到单位幅值点目标冲激响应;

4)后向散射系数矩阵与点目标冲激响应卷积;

5)计算并处理基带回波数据。

2.2 回波仿真算法性能对比

经过8次不同目标复杂度,复杂度依次提升的算法测试,得到图1所示为三种算法在目标仿真中的性能对比,图2(a)得出随着目标模型复杂度提升,RTPC算法耗时显著,其它两类基于频域的算法耗时维持稳定;图2(b)表示在该趋势下,2D-FFT算法的应对多种复杂模型的能力要优于其它两类算法。得出改进的2D-FFT算法无论在时间消耗还是对目标模型的适应性上都有明显优势。

图1 机载SAR信号获取示意图

图2 回波仿真算法性能比较

回波仿真算法是目标模型的实现方法以及后端数字信号处理的入口,其高效性和衔接程度影响着回波仿真器整体的实现性能。机载合成孔径雷达回波仿真中的关键问题可以划分为算法与流程两个层面分别加以解决。首先,算法上应保证回波信号的真实性与有效性以及回波信息存储的高效性;流程上保证回波仿真信号的实时性和严格的时序特性,保证产生的信号可以与待测雷达建立同步,在保证相参的条件下以较高的速率传输回波仿真数据。

3 机载SAR回波仿真方法

SAR回波信号仿真中,频域仿真方法用于计算回波信号的相位信息,时域仿真方法控制距离向回波的延时时间和脉冲宽度,从而在整个二维信号平面上呈现距离弯曲现象。

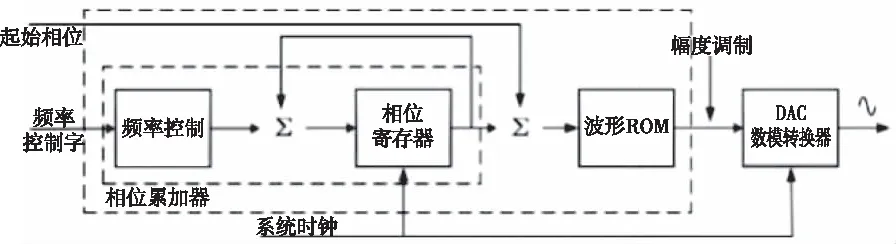

3.1 合成孔径雷达频域仿真技术

随着高性能数字集成电路的发展,直接数字频率合成(Direct Digital Synthesis,DDS)为频率合成的首选方案,其原理如图3所示。在文献[2]中,Sunderland,Nicholas等学者都提出了针对上述存储结构的优化方法,通常是对ROM存储的波表结构进行压缩,这解决了基于ROM DDS设计中的存储部分问题,证明了在具有大存储容量的通用计算机中基于ROM的DDS的可行性。在某些场景中考虑到数据结构的特点,特别是在大场景的机载SAR面目标回波仿真中,可以对信号的相位信息进行进一步压缩。考虑到传统的硬件往往难以兼顾大容量存储与实时仿真。根据合成孔径雷达回波信号的特点,对传统的ROM结构进行优化,来实现较高的压缩比。

图3 直接数字频率合成原理

机载SAR雷达回波信号表示为如下形式:

s(x,y)=A0·wr(x)·wa(y)·θ(x,y)

(6)

其中,A0代表回波幅度调制,wr(τ)与wa(η)分别为回波信号在距离向与方位向的范围,而表征回波相位信息的为θ(τ,η),对其展开可得

θ(x,y)=exp(jπKr(x-tau(y))2-j2πf0·tau(y))

=cos(πKr(x-tau(y))2)·cos(2πf0·tau(y))+

sin(πKr(x-tau(y))2)·sin(2πf0·tau(y))+

j·sin(2πf0·tau(y))

(7)

令A=πKr(x-tau(y))2,B=2πf0·tau(y),最终相位信息的存储可以表示为

θ(x,y)=cosA·cosB+sinA·sinB+j·sinB

(8)

由以上分析可知,针对特定的仿真场景,例如单点目标的回波仿真或复杂面目标回波场景,对回波信号的相位信息进行压缩存储与处理。除此之外,随着测试需求的不断丰富,机载SAR回波信号仿真器也应具有多模式工作的能力,本文进一步对传统的基于DDS的方法进行优化。

高速乘法器与大存储量通用处理器的广泛应用缓和了资源与速度的矛盾,在需要严格相参的高速信号处理场合,坐标旋转数字计算(COordinate Rotation DIgital Computation,CORDIC)算法为FPGA中应用的首选。CORDIC算法通过2的幂指数作为伪旋转角度,经过有限次迭代来实现所需精度的相位分辨率,其数值计算原理如式(8)所示。CORDIC算法可以基于圆坐标系、线性坐标系以及双曲坐标系,工作于旋转模式或向量模式下

(9)

通过计算z得到循环误差,进而迭代计算x,y来不断提高运算结果的精度。

zi+1=zi-di·arctan(2-i)

(10)

xi+1=xi-yi·di·2-i

(11)

yi+1=yi+xi·di·2-i

(12)

当N取足够大的数值时,即zN=0时,得到最终的计算结果。

xN=AN·(x0·cos(z0)-y0·sin(z0))

(13)

yN=AN·(y0·cos(z0)+x0·sin(z0))

(14)

其中,可以预先计算出幅度因子,作为校正,如下式。

(15)

CORDIC算法的另一个优势在于硬件电路实现,根据迭代方程组(8)可知,计算量主要集中在已知次数的相乘计算,乘数因子被量化为2的幂次,因此在可编程逻辑器件中通过移位器和加法器即可组成工作在流水线模式下的硬件电路,这一类以高速时钟驱动的逻辑电路计算效率高于通用处理器,具体实现形式则如图4所示。

图4 坐标旋转数字计算的硬件实现形式

坐标旋转数字计算的算法流程如下所示。

算法2:CORDIC

1)确定旋转方向di

2)根据(3)式1,2进行迭代计算

3)根据(3)式4追踪累加的旋转角度

4)计算伸缩因子Kn

5)将输出x(n),y(n)与伸缩相乘

6)输出超越函数值sine/cosine

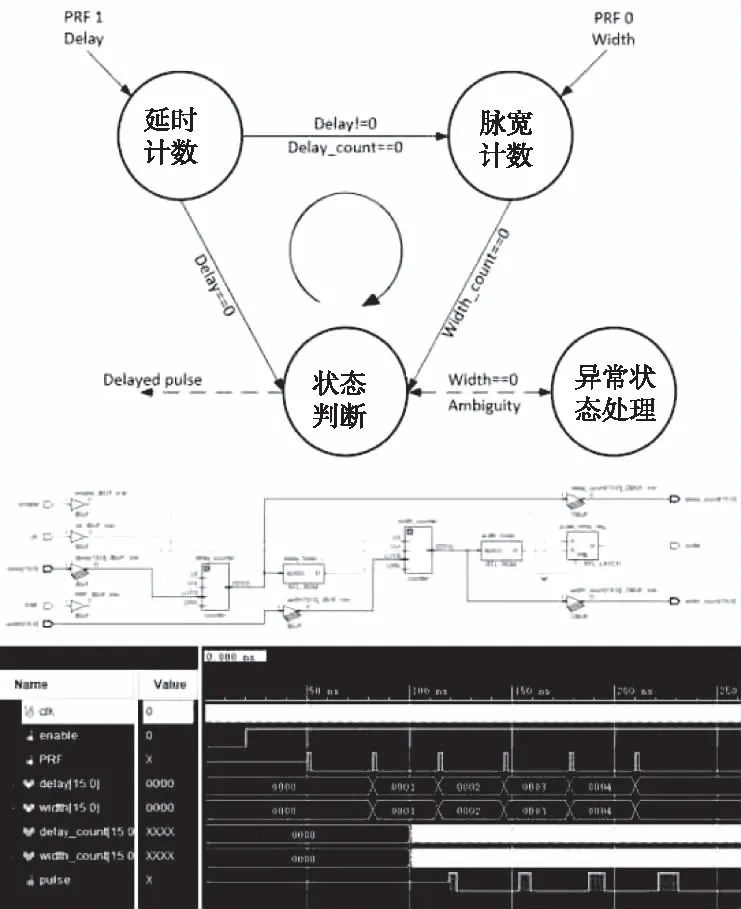

3.2 合成孔径雷达时域仿真技术

回波的时域仿真技术要求对仿真回波的起止时刻和脉冲宽度进行精确的控制。本文通过有限状态机(Finite State Machine,FSM)的方法,结合计数器IP对回波信号的延时和脉冲宽度进行控制,原理框图、综合电路以及时序特性如图5所示,可以由时序图验证逻辑电路响应雷达同步脉冲,实现了对仿真回波的时域控制。

图5 时域仿真状态转移图,电路以及时序图

在仿真中,通过雷达脉冲同步信号PRF触发,状态机根据延时数据和脉冲宽度数据对雷达输出信号进行控制,具体流程如下所示。

算法3:时域延时与脉宽控制Delay-width_Control

1)监听雷达同步触发脉冲 PRF,上升沿执行下一步

2)监听延时值

如果延时值为零,延时计数置为零

否则延时计数为延时值

3)进入延时计数器,计数值依时钟周期递减归零

延时结束,生成脉冲起始标志

4)监听脉宽数据

如果脉宽为零,进入异常状态处理

否则脉宽计数为脉宽值

5)进入脉宽计数器,计数值依时钟周期递减归零

脉宽结束,生成脉冲结束标志

4 回波仿真器设计与分析

4.1 硬件实现平台

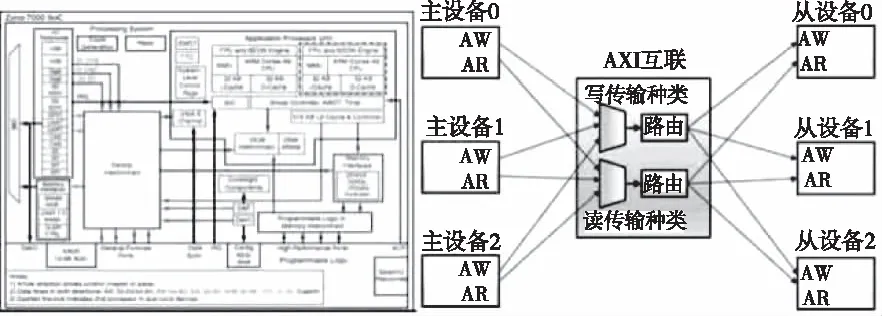

本文的仿真平台设计使用CPU(ARM)和现场可编程门阵列(FPGA)结合的ZYNQ片上系统,简化了回波仿真器的系统级设计。ZYNQ-7000提供AXI接口和总线类型,分别为高性能和带宽的标准接口AXI_HP,用以处理DMA类不带缓存AXI外设的加速器一致性接口AXI_ACP以及通用接口AXI_GP。AXI接口总线类型可分为面向高性能地址映射通信的AXI4,在AXI4基础上对占用资源进行精简的AXI4-Lite与面向高速数据流传输的AXI4-Stream。合成孔径雷达回波仿真器设计中所采用的芯片为XC7Z010-1CLG400,其具有双核ARM Cortex-A9 MPCoreTM处理器(Processing System,PS)以及28nm Artix-7架构的FPGA(Programmable Logic,PL),处理器部分最高频率为866MHz,PL部分包含28K可编程逻辑单元、17600查找表、35200触发器以及2.1Mb BRAM和80个DSP处理块。

图6 ZYNQ片内架构与AXI互联

4.2 脚本CORDIC仿真方法

传统的带有数字信号处理能力的回波仿真器大多数是基于ROM的DDS方法,消耗仿真器的大量存储,尤其是在复杂场景SAR目标仿真中。

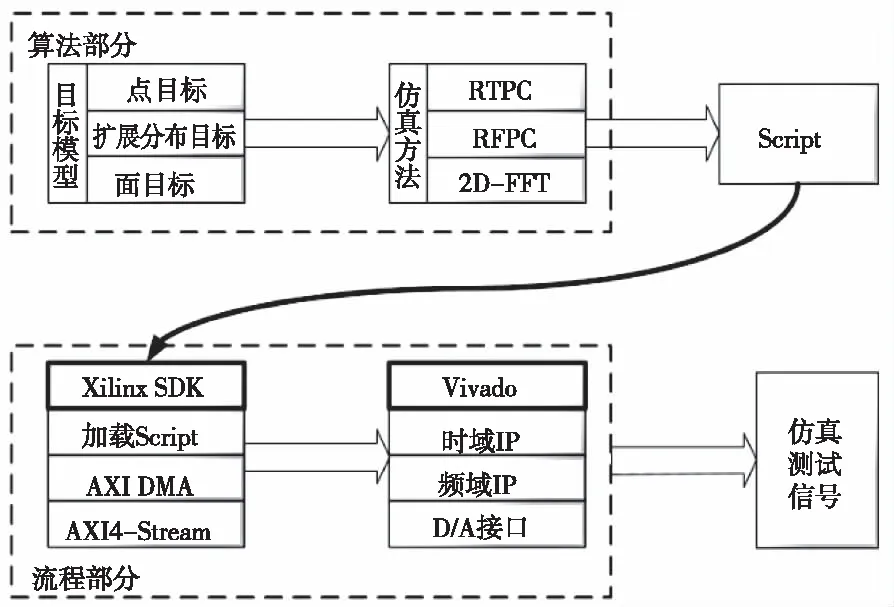

为解决此问题,本文提出了基于脚本坐标旋转数字计算(Script-CORDIC)的回波仿真方法来清晰地规划回波仿真算法与流程之间的关系。

对于回波仿真器的算法设计部分,通过Matlab生成脚本,在回波仿真器设计中将其存储在ARM端的DDR,减少对逻辑存储资源的消耗; 对于回波仿真器的流程设计部分,首先通过PS部分DDR存储的回波相位信息经过AXI DMA发送至PL端,由PL部分的CORDIC DDS IP核实时计算回波信号的频域信息,并通过时域仿真IP控制数据接收的起始。

通过上述基于脚本的回波仿真方法,进一步使算法部分的设计适应于多模式SAR目标回波仿真要求,流程部分适应于实时回波仿真的要求,工作流程如图7所示。

图7 回波仿真工作流程

回波仿真器流程算法如下所示。

流程:回波仿真器程序

1)Matlab/SystemGenerator/ModelComposer

加载目标模型

选择回波仿真算法 RTPC/RFPC/2D-FFT

生成回波相位数据脚本

得出仿真时间、脚本大小信息

2)启动Xilinx SDK,进入Debug模式

主程序中调用脚本

通过AXI接口,以DMA方式将数据发送至PL IP

3)进入Vivado

检查时域控制IP

检查频域CORDIC IP

通过D/A数据转换,有D/A接口输出仿真信号

4)回到步骤1.1,重新加载目标模型

回到步骤1.2,重新选择回波仿真算法

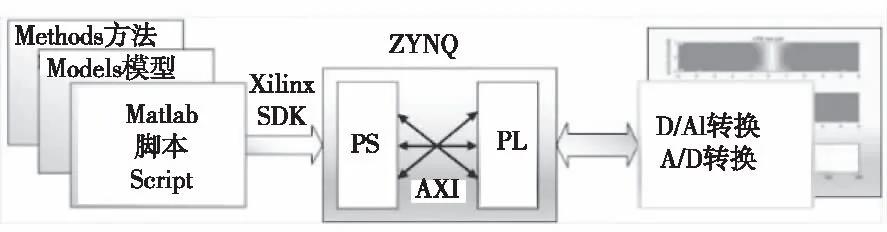

回波仿真器的硬件设计在ZYNQ-7010CLG400实验板上,通过AD/DA模块实现,D/A模块主芯片采用ADI AD9708,A/D模块主芯片采用ADI AD9280;软件设计则是使用Matlab、Vivado等集成设计工具进行开发。回波仿真器的工作流程是经由脚本生成器产生仿真目标的数据,在ZYNQ PS端加载脚本并对PL端进行初始化,将仿真数据通过AXI DMA以及AXI FIFO发送至CORDIC DDS IP,并通过DA转换得到目标的仿真回波,如图8所示。

图8 回波仿真器整体设计

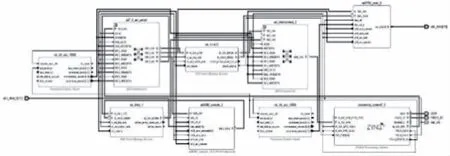

由Vivado的原理图设计得到回波仿真器的整体图,以IP核互联的方法搭建回波仿真器ZYNQ处理器核、DMA传输核、A/D采样数据转换核、D/A转换数据处理核、复位以及时钟核等,并引出8位A/D采样数据接口和8位D/A数据传输接口。

图9 回波仿真器FPGA电路原理图

5 实验结果及分析

机载SAR回波仿真器的实验平台基于ZYNQ XC7Z010,数字后端连接DA模块。

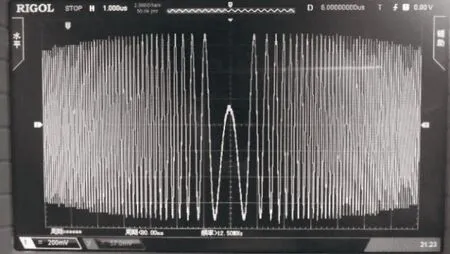

仿真器数模转换接口通过BNC连接线至示波器,得到基于2D-FFT算法的SAR回波信号的实验结果。

图10 回波仿真信号DA转换示波器波形(取s(:,180))

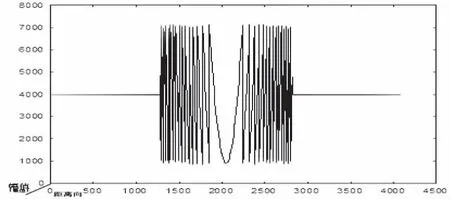

同时,在ZYNQ FPGA的逻辑部分可以对Matlab生成的仿真回波数据进行预先处理与查看,如下图所示。

图11 ZYNQPL部分回波仿真图

进一步,结合实验的结果首先对目标回波仿真结果进行分析。如下图所示,点目标回波经过距离-多普勒算法成像,验证了其作为卷积核的正确性。

图12 单点目标成像测试

实际生成的面目标回波按距离向排列成相位不断变化的线性调频信号,每个信号之间的时延模拟了实际接收情形,符合SAR信号接收的距离弯曲等式。

图13 距离向回波仿真信号(取s(:,160))

实验中定义了预设为十字状的面目标,经过2D-FFT算法得到仿真信号,然后经过距离多普勒成像进行验证。

图14 面目标回波仿真信号幅度图(a)及RD成像算法验证(b)

通过对实验结果的分析,可知在上述面目标仿真模型下采用传统DDS方法将会消耗5MB左右FPGA片内BRAM存储,远远超过ZYNQ PL部分所能负荷的2.1Mb。而DDR端可以灵活读写的内存大小为2Gb,可以容纳复杂仿真回波模型,同时降低芯片功耗。

6 结论

为提高机载SAR回波仿真器的实时性能和复杂模型的加载能力,设计了基于ZYNQ的机载SAR回波仿真器,并提出了回波仿真器中由脚本加载模型的方法,以及回波仿真在频域和时域中仿真技术的实现。第一种方法针对回波仿真算法,以优化二维快速傅里叶变换为基础来计算雷达仿真回波;第二种方法针对回波仿真器本身工作特点,通过脚本CORDIC的观点来平衡PS与PL的工作负荷,充分发挥了异构平台在回波仿真应用中的优势。对比仿真与FPGA硬件平台实验结果,表明回波仿真器具有实时产生高质量机载SAR回波信号的能力。