MSK调制直接射频合成算法的设计与FPGA实现

2021-11-03四川九洲电器集团有限责任公司朱爱红杨伟军汪小林

四川九洲电器集团有限责任公司 朱爱红 杨伟军 程 旗 汪小林 何 敏

根据软件无线电发射电路的信号处理要求,提出了一种MSK调制直接射频合成算法。在FPGA实现方面,提出了DDS直接数字合成器和分布式单端口RAM查表两种实现方式,并在以FPGA及DAC为关键器件的硬件平台上进行了验证。电子设计自动化(Electronic Design Automatic,EDA)工具的综合与实现结果表明,两种方式各有优缺点,适用于不同的场景。

近年来随着软件可配置、可编程芯片的成熟应用,问世了多款高性能集成芯片,其中包括有力推动发射电路很大程度上接近理想软件无线电架构的核心器件,例如高采样低功耗的射频DAC集成芯片以及高速超大容量高互联带宽的FPGA芯片。

FPGA+DAC的硬件架构可实现发射通道的主要功能,包括数字直接射频合成、数字滤波以及数模转换。数字直接射频合成是是一种同时进行数字基带信号产生和数字上变频的联合信号处理算法,不同于过去数字基带调制和数字混频功能分开处理,当前工程应用越来越趋向于将这两种功能进行融合处理。

MSK调制是FSK调制的改进。FSK信号的两种码元波形没有严格正交,传输时包络会出现起伏,误码率性能较差。MSK信号则是一种包络恒定、相位连续、带宽最小且严格正交的FSK信号。因此,MSK调制方式具有功率谱密度较集中,频带利用率高等优点。

1 算法设计与实现

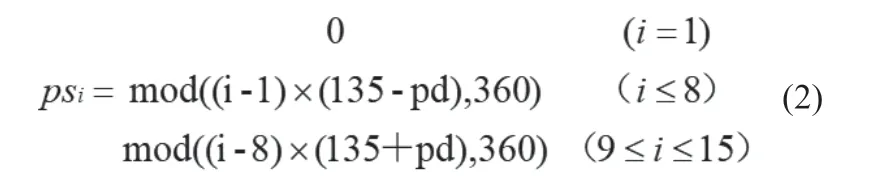

MSK调制直接射频合成算法是在发射调制框架内按照模数转换频率依次输出q×m×n个MSK数字基带调制信号,q为发射调制框架内输入符号个数,m为每个符号采样点个数,n为MSK基带调制信号路数,每路基带调制信号的初始相位不同。在发射调制框架内先发送第1个输入符号的第1个采样的第1路调制基带信号,最后发送第q个输入符号的第m个采样的第n路调制基带信号,第i个输入符号的第j个采样的第k路调制基带信号在发射调制框架内的位置pmi,j,k的计算公式如式(1)所示:

其中,i=1,2,…,q;j=1,2,…,m;k=1,2,…,n。

1.1 算法设计仿真

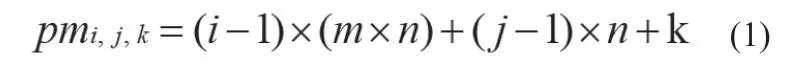

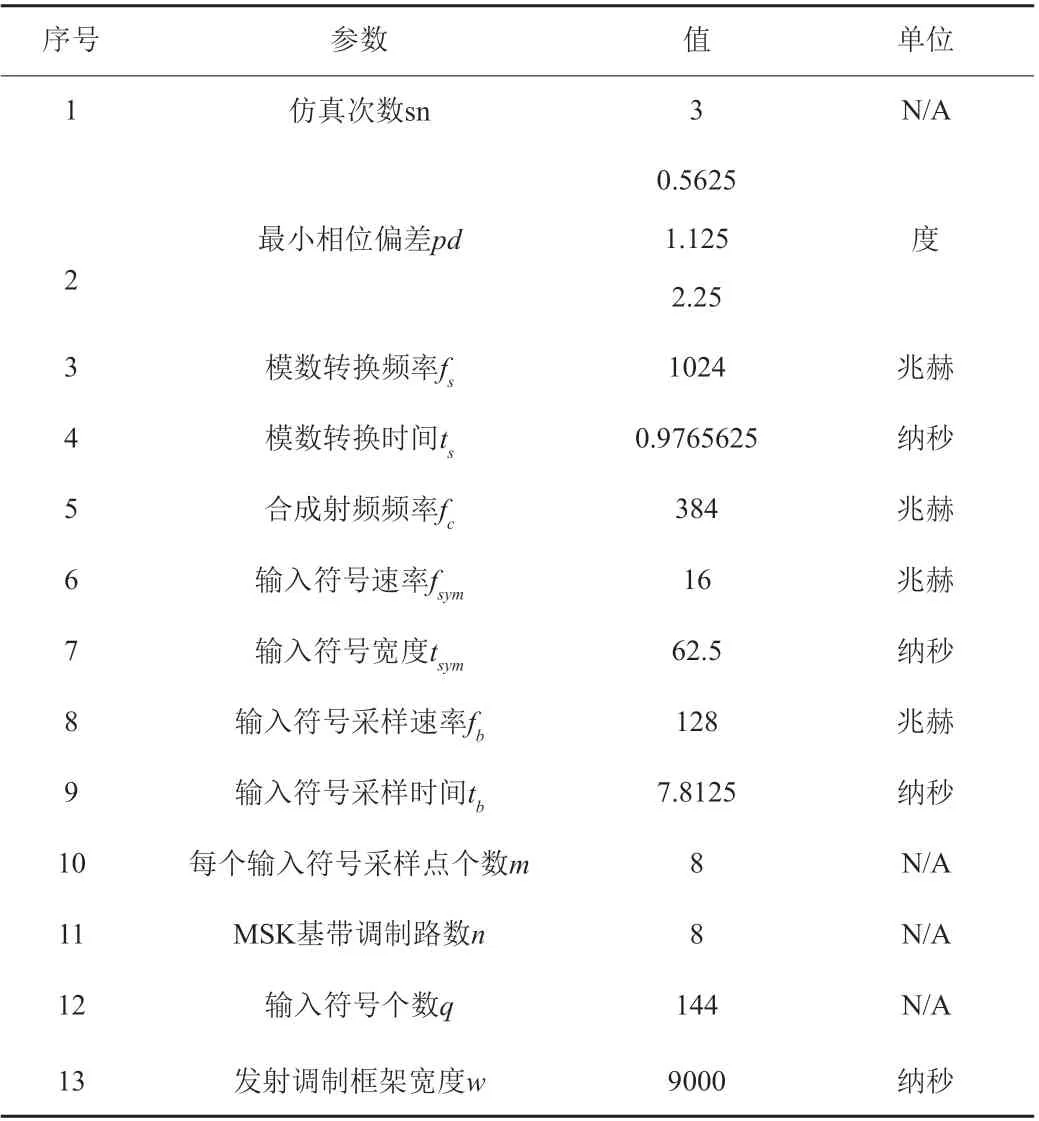

使用Matlab软件进行算法的设计仿真,基本参数设定如表1所示,流程图如图1所示。

表1 设计仿真程序基本参数

图1 设计仿真程序流程图

1.1.1 设置最小相位偏差pd

三次仿真,pd分别设置为0.5625°、1.125°及2.25°。

1.1.2 计算2×n-1个初始相位ps

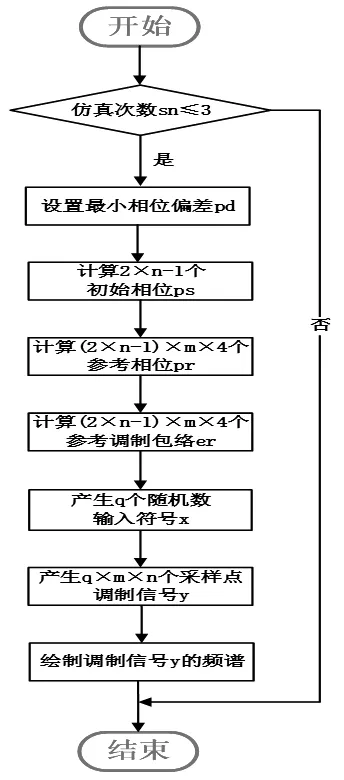

当n为8时,15个ps(单位度)计算公式如式(2)所示:

式中,mod()为求模运算;i=1,2,…,15。

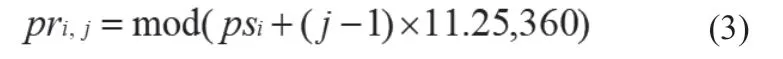

1.1.3 计算(2×n-1)×m×4个参考相位pr

当n为8且m为8时,15×32个pr(单位度)计算公式如式(3)所示:

式中,mod()为求模运算;i=1,2,…,15;j=1,2,…,32。

1.1.4 计算(2×n-1)×m×4个参考调制包络er

当n为8且m为8时,15×32个er计算公式如式(4)所示:

式中,sin()为求正弦值运算;i=1,2,…,15;j=1,2,…,32。

1.1.5 产生q个随机数输入符号x

调用Matlab函数randi产生q个正态分布随机数整数数组,该数组作为输入符号x,数组元素取值0或1。

1.1.6 产生q×m×n个采样点调制信号y

MSK数字基带调制是使用差分或非差分编码最小频移键控调制方法输出消息信号(即输入符号)的复数包络。本算法采用差分编码最小频移键控调制方法,调制包络y为适应硬件平台的DAC芯片进行了简化,只取复数包络的虚部。

(1)差分编码最小频移动键控调制

差分编码最小频移键控调制规则如下:

a.每个符号的调制相位累加值都等于90°

b.所有采样点的调制相位是连续变化的;

c.每个采样点的调制相位变化量等于90°/m,例如,本算法m为8,每个采样点的调制相位变化量为11.25°;

d.输入符号为‘1’,当前采样点的调制相位在前一采样点的调制相位基础上累减11.25°;

e.输入符号为‘0’,当前采样点的调制相位在前一采样点的调制相位基础上累加11.25°。

(2)调制信号y的计算方法

当q为144且m为8且n为8时,调制信号y是9216个采样点复数包络虚部。采样点复数包络虚部的计算方法如下:

a.计算参考调制包络er行地址ar;

b.计算参考调制包络er列地址ac;

c.参考调制包络er中行地址ar列地址ac所对应的的元素取值即为该采样点复数包络虚部。

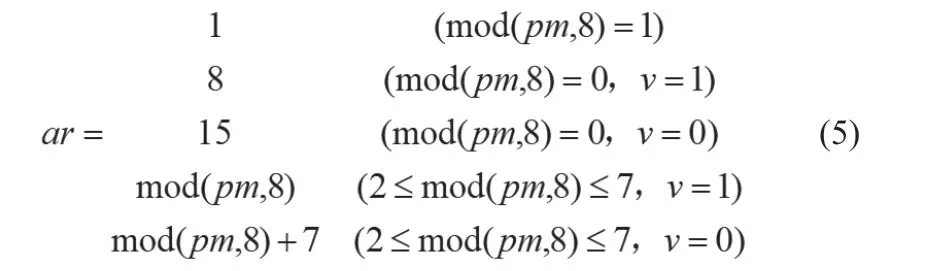

(3)参考调制包络行地址ar的计算方法

ar为大于0且小于16的整数,由采样点在发射调制框架中的位置pm以及该位置对应输入符号取值v确定,计算公式如式(5):

式中,mod()为求模运算;pm为大于0且小于9217的整数。

(4)参考调制包络行地址ac的计算方法

ac为大于0且小于33的整数,第1个采样点的ac取值等于1,其余采样点ac取值由前一采样点参考调制包络列地址acp以及该采样点在发射调制框架中的位置pm对应的输入符号取值v确定,计算公式如式(6):

式中,mod()为求模运算;pm为大于0且小于9217的整数;

acp为大于0且小于33的整数。

1.1.7 绘制调制信号y的频谱

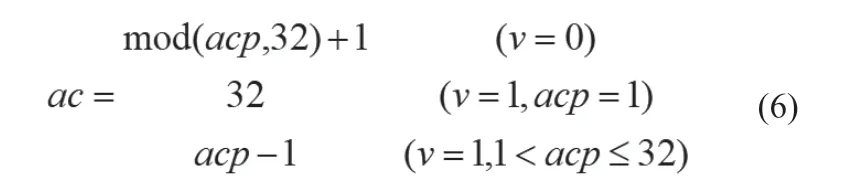

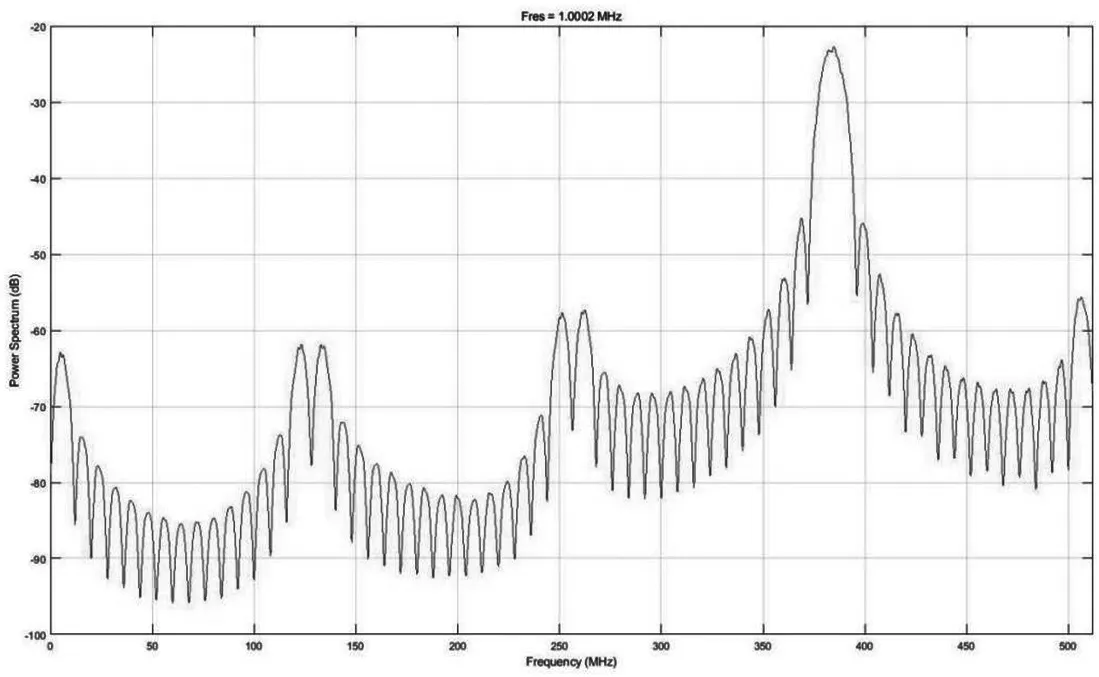

调用Matlab函数 pspectrum()绘制三种调制信号y的频谱,如图2~4:

图2 Pd=0.5625°调制信号频谱

图3 Pd=1.125°调制信号频谱

图4 Pd=2.25°调制信号频谱

最小相位偏差Pd对主瓣幅度没有影响,但会影响第一、第二旁瓣幅度,当取值0.5625°及2.25°时,第一、第二旁瓣幅度比主瓣幅度低36dB左右,当取值1.125°时,第一、第二旁瓣幅度比主瓣幅度低46dB左右,因此最小相位偏差Pd的较优取值为1.125°,在FPGA实现中Pd取值设置为1.125°。

1.2 算法FPGA实现

使用vivado软件进行FPGA算法设计、仿真、综合、布局布线并产生位流文件后进行在线加载调试。

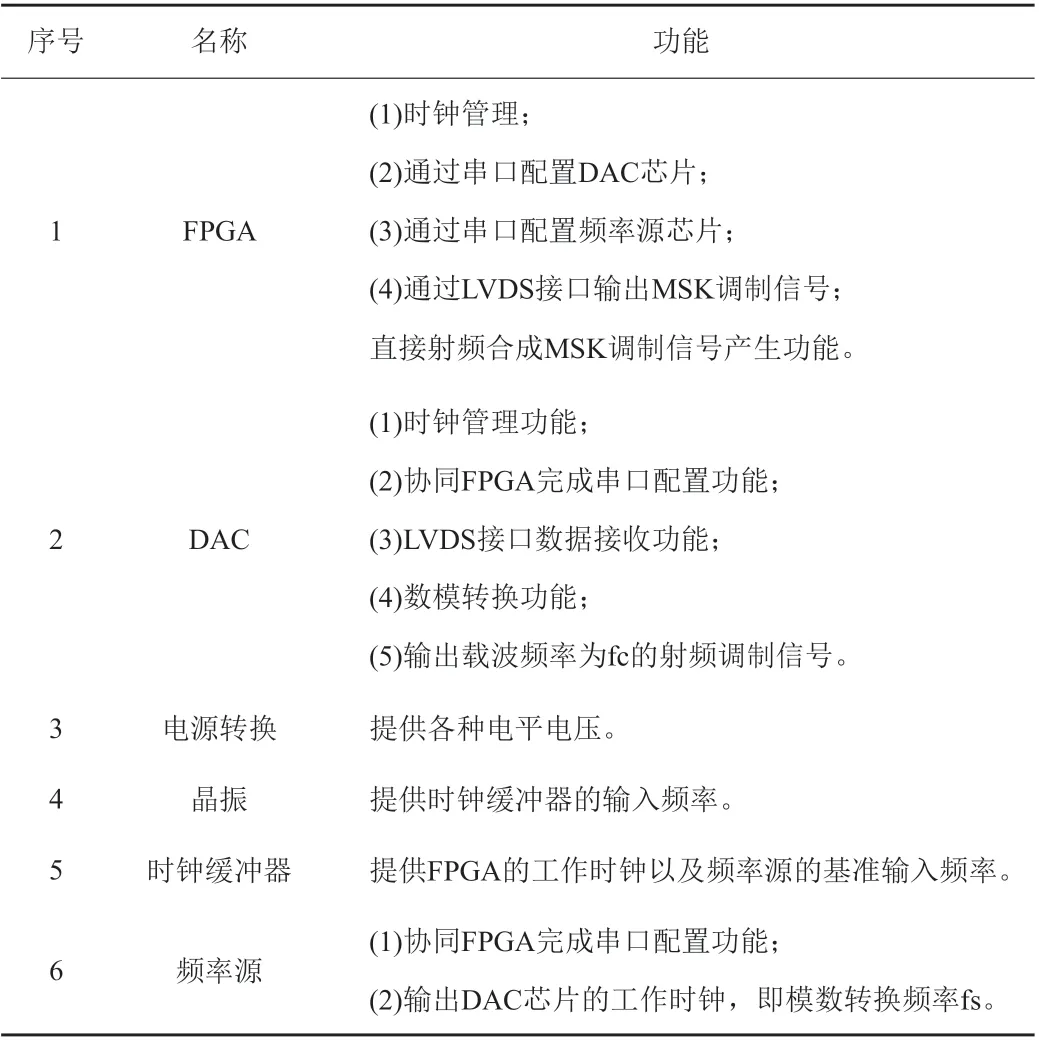

硬件平台采用5V直流电压供电,由FPGA、DAC、电源转换、晶振、时钟缓冲器以及频率源等芯片组成,芯片功能如表2所示。

表2 硬件平台芯片功能

表2列出的FPGA的前四项功能是为了在硬件平台验证MSK调制直接射频合成算法的附加功能,本论文不做描述。实际工程实践中,利用FPGA实现直接射频合成MSK调制信号产生功能通常有两种算法,一种是DDS直接数字合成器算法,另一种是分布式单端口RAM查表算法。

1.2.1 DDS直接数字合成器算法

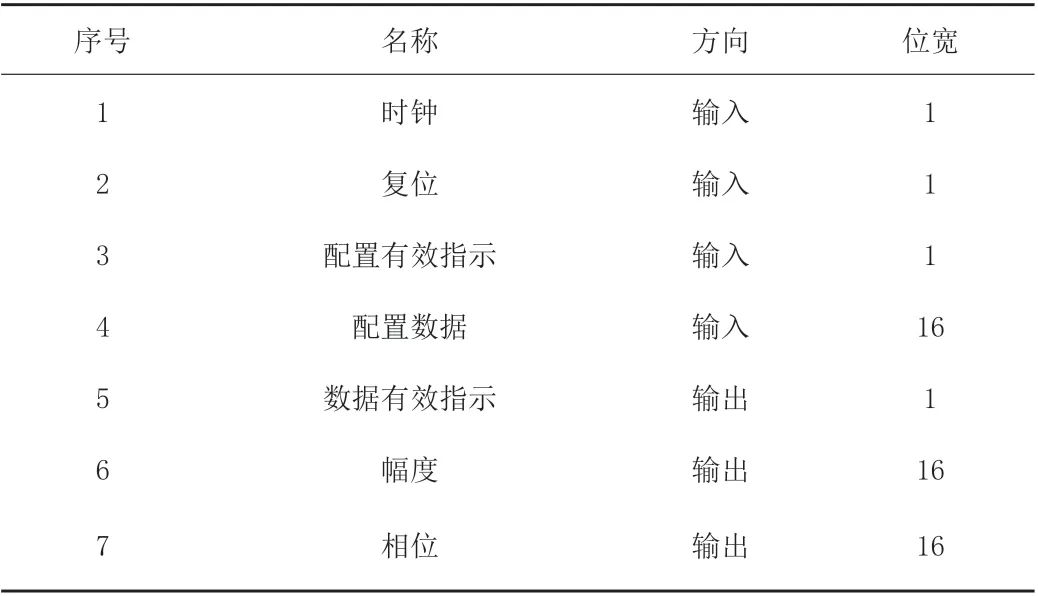

核心部件是DDS直接数字合成器(简称DDS),一种由FPGA厂家提供的数字信号处理调制类IP核。DDS由相位发生器和正弦/余弦查找表两部分组成,两部分可独立或联合使用。DDS配置参数如表3所示,输入输出端口如表4所示。

表3 DDS配置参数

表4 DDS DDS输入输出端口

MSK基带调制路数n为8,因此需要例化8个DDS核。

1.2.2 分布式单端口RAM查表算法

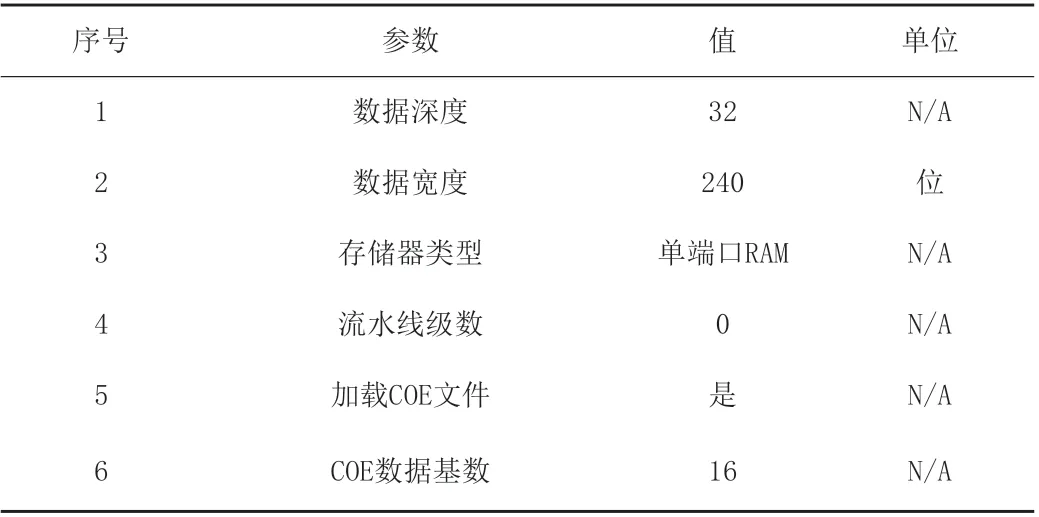

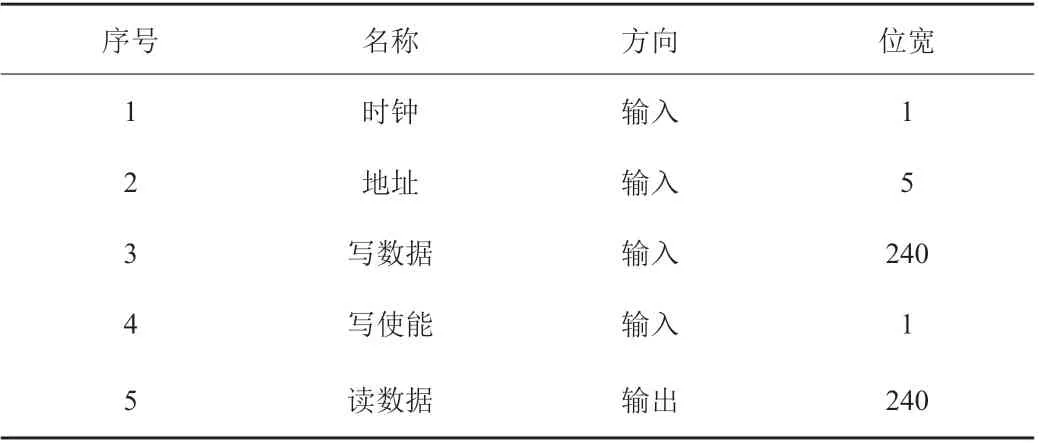

分布式单端口RAM算法(以下简称查表法)的核心部件是分布式单端口RAM,一种由FPGA厂家提供的存储类IP核。分布式单端口RAM配置参数如表5所示,输入输出如表6所示,加载COE文件是预先将参考调制包络er数据转换为32行240位格式化数据获得。

表5 分布式单端口RAM配置参数

表6 分布式单端口RAM输入输出端口

2 性能分析

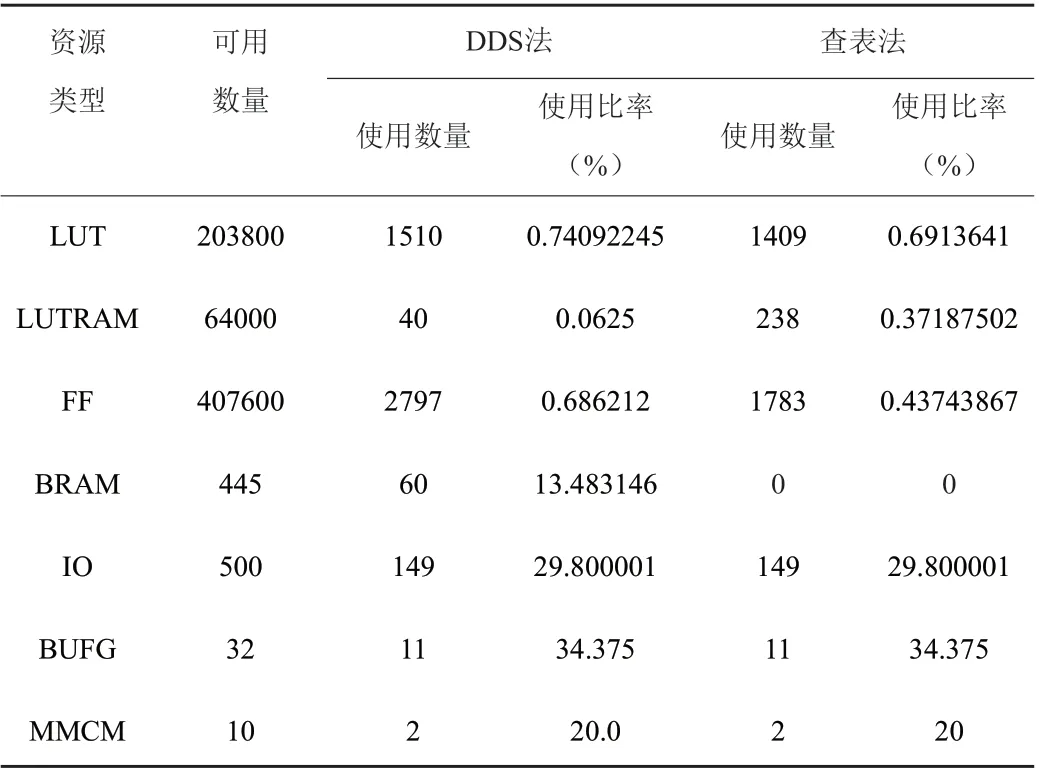

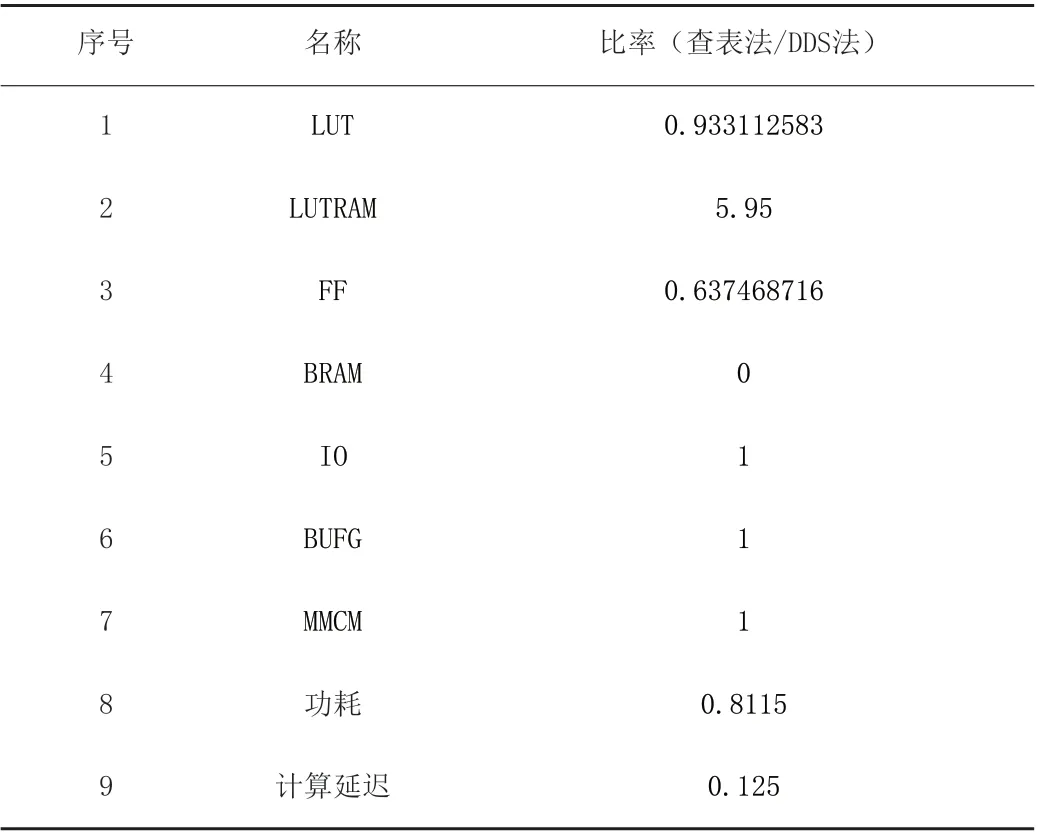

利用vivado软件分别实现了DDS法和查表法两种算法。预估功耗方面,查表法为0.934W,DDS法为1.151W;计算延迟方面,查表法1个时钟,DDS法8个时钟;两种算法资源消耗情况如表7所示,两种算法的资源消耗、功率消耗及计算延迟比率如表8所示。

表7 算法的资源消耗情况

表8 算法数据分析表

两种算法的IO、BUFG及MMCM等资源消耗完全相同,查表法除了LUTRAM资源消耗明显增多之外,LUT、FF及BRAM等资源消耗都比DDS法要少,尤其是BRAM的资源消耗等于零。另外,查表法的功耗更低。总体而言,查表法不仅总体资源消耗优于DDS法而且延迟比DDS法显著减小;DDS法主要优势是可复用及可扩展,支持多种调制方式。

综上所述,DDS法适合调制方式较多的时分复用应用系统,而查表法适合高实时性、低功耗统且主要调制方式为MSK的应用系系统。