基于FPGA的高速串行IO研究

2021-10-15闫胜刚江伟伟

闫胜刚,江伟伟

(中国船舶集团有限公司第八研究院,南京 211153)

0 引 言

I/O接口在工业应用中一直扮演着重要角色,随着信号处理越来越复杂,其I/O传输数据率也从600 Mb/s激增到12 Gb/s,甚至更高的带宽。由于无法提供可靠的系统同步时钟、并行端口位宽的激增以及同步开关噪声问题的引入,传统并行I/O接口不再是可靠、经济的方法。千兆位串行I/O技术由于较少的引脚数、不需要同步时钟、EMI较低,逐渐成为解决高速接口的选择,广泛用于芯片到芯片的接口、VPX背板连接以及系统板级的通信。

基于GTX核的高速差分串行通信方式已成为FPGA内构建串行SRIO协议、PCIE协议、千兆以太网的标准物理基础。根据传输链路的物理特性,合理设置GTX的收发参数成为高速I/O可靠传输数据的基础。本文基于Virtex-6的FPGA芯片,配置GTX的相关参数,分析相关设置对链路的影响,最后将该参数用于SRIO协议的物理层,通过实际测试验证SRIO的传输性能。

1 GTX工作原理

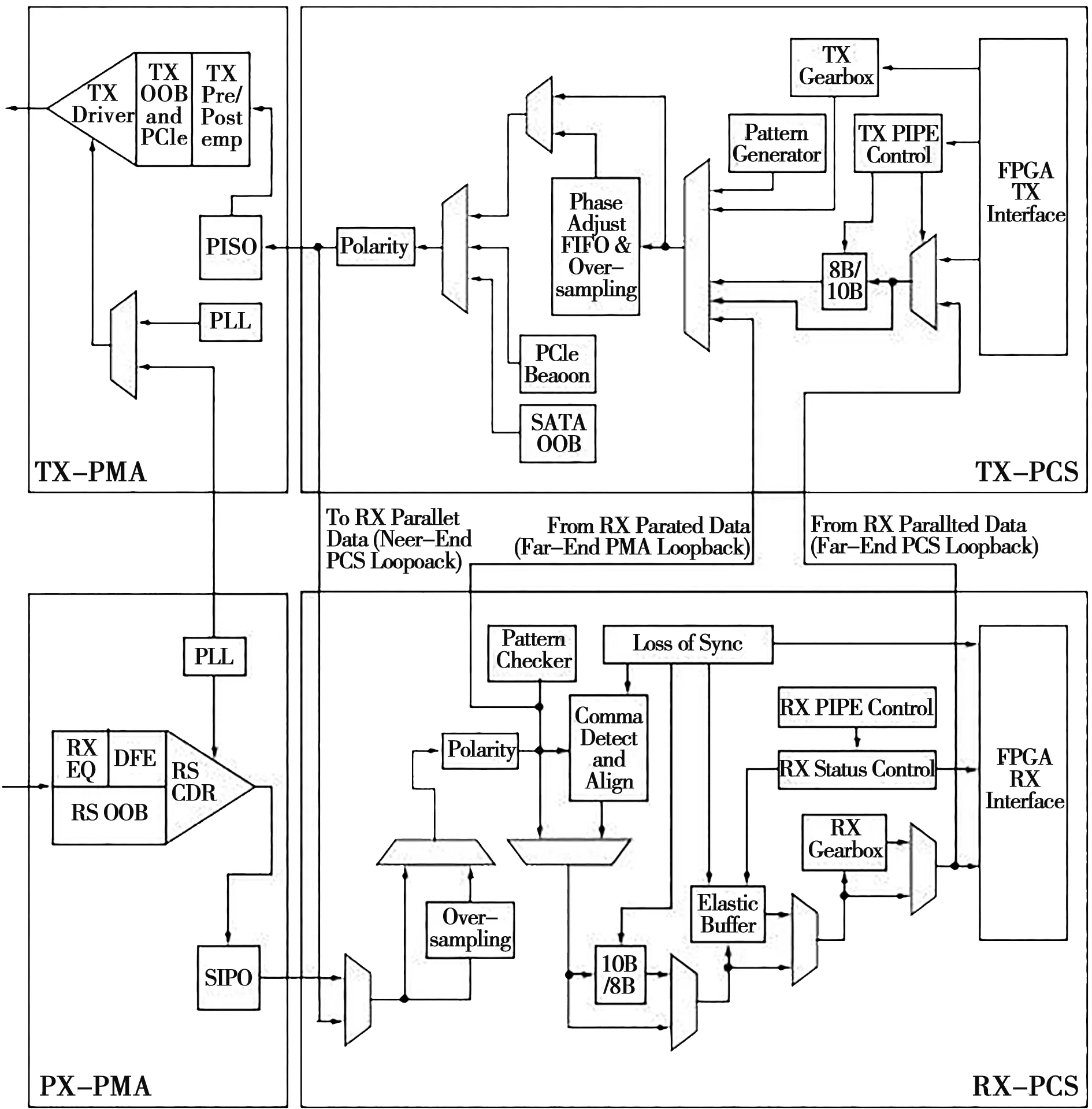

GTX由发送模块和接收模块、时钟管理模块三部分组成,如图1所示。

图1 GTX结构图

发送模块在内部接收并行数据,经过线路编码、发送FIFO缓存、极性控制、并串转换、预加重等处理,最后通过发送前端输出串行信号。

接收模块通过模拟前端接收串行数据,经过RX均衡器、时钟数据恢复模块、串并转换、字节对齐模块、失步状态机、线路解码、时钟修正和通道绑定等处理,转换成并行数据输入。

时钟管理模块由FPGA专用时钟引脚,在FPGA内部通过PLL锁相环产生串行发送器时钟以及接收器的参考时钟,并且通过分频供内部并行通道以及外部逻辑使用。

1.1 数据编码

数据编码将输入的原始数据转变成一种数据格式,保证有足够的高低电平切换提供给时钟恢复电路,并提供约定的comma控制字符用于数据按字对齐,同时编码后的数据保持0和1个数一致以达到良好的直流平衡。

FPGA可用的编码机制有8 b/10 b编码、64 b/66 b和扰码技术。由于8 b/10 b编码机制连0或连1最长为5位,相对64 b/66 b和扰码具有更丰富的0/1跳变,但是8 b/10 b编码开销相对较大,为了获得8 G的带宽,需要10 G的线路速率,而64 b/66 b开销小很多。扰码技术采用随机码对数据进行按位异或实现数据的随机化,不需要额外的带宽。在高速数据传输时考虑码间串扰影响,同时参考SRIO传输规范,本文采用8 b/10 b编码机制。

1.2 预加重处理

发送的数据随着传输速率的提高,数据间的干扰逐渐严重,如果串行流中包含多个比特的相同数据,而其后面跟着一个比特的相反数据,就会发生符号间串扰,具体原因是由于传输通道在短时间过程中没有足够时间充电,从而产生较低的幅度,进而造成0/1的错误判断。图2描述了这种现象的发生情况。

图2 码间串扰

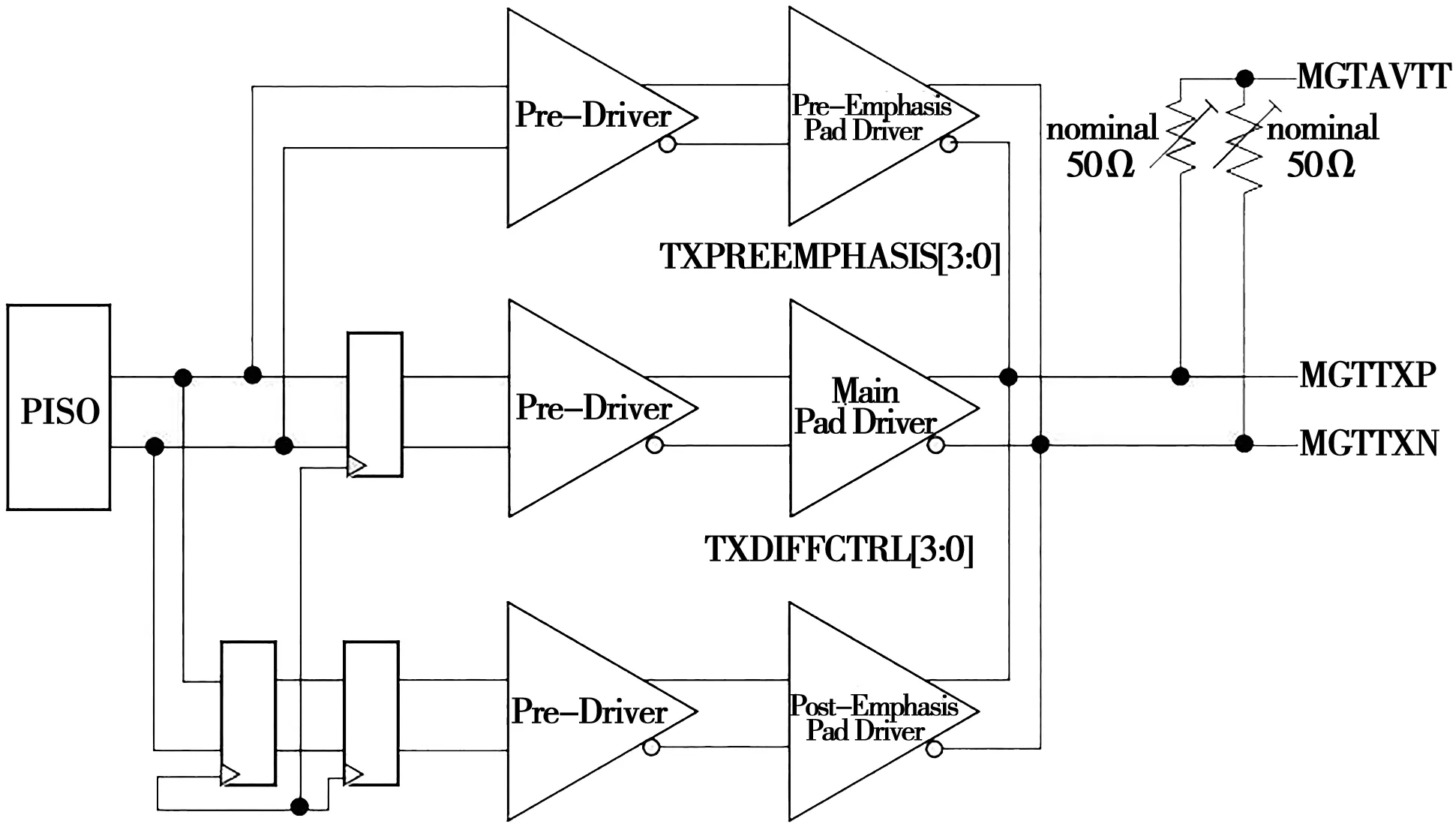

采用预加重技术,使发送转变的数据有过量驱动,通过设置前加重、后加重以及去加重参数减小码间串扰的影响,从而可以降低数据传输的误码率,预加重电路如图3所示。

图3 预加重电路

1.3 线路均衡技术

发送的数据在链路传输过程中,由于高频衰减、阻抗匹配以及频率不同引起波移。通过线路均衡能够达到一定的补偿作用,弥补传输过程中的损失,提高接收数据的正确判断。均衡通常有两种方式:频率响应补偿均衡器和判决反馈均衡器。频率均衡器采用抑制低频放大高频的方式对接收的频带进行线性滤波,但是链路的实际衰减比较复杂,针对不同链路,频率衰减曲线各不相同,并且随着时间和温度变化,衰减会有响应变化。频率均衡技术如图4所示,只能选择最接近线路衰减的一种曲线进行补偿,并不能完全匹配线路真实衰减。

图4 频率补偿滤波器

对于串扰的精细调节,可以通过调节判决反馈均衡器中的反馈系数,消除每个数据的响应拖尾,进而消除对后续数据的影响,此方法适用于更高频率的串扰处理。判决反馈均衡器结构如图5所示。

图5 判决反馈均衡器

1.4 时钟数据恢复和comma字节对齐

时钟数据恢复和comma字节对齐是高速串行传输的核心,由于高速串行数据包含了时钟信息,所以需要从收到的数据中恢复时钟,并采用恢复时钟读取接收的串行码,获得串行数据,并采用comma字节对齐功能对串行数据设置窗口,从而保障串行到并行的转换后,数据不会乱码。

2 Ibert配置及参数调节

串行信号进入Gbit级别后,对串行信号传输质量的测试变得十分必要,Xilinx提供了IBERT辅助工具,用于串行IO接口传输性能的测试。IBERT可以在线调整高速串行接口的多种参数,还能实时测量传输误比特率以及眼图参数的功能。

2.1 测试回路设置

采用VPX机箱搭建测试平台,如图6所示,通过光纤远程环回模式进行测试,FPGA板的发送端发送PRBS-7类型的测试数据,通过VPX背板的高速差分线转发到控制接口模块,控制接口模块转化为光信号后发送出去,通过光纤链路回收光信号,并最终传输到FPGA板的接收端,通过和发送端的PRBS-7模型对比判定接收数据的误码率。

图6 测试链路

2.2 IBERT配置

打开ISE开发环境,新建测试工程,设置器件的类型、封装、速度等级等,生成工程文件。新建IP核,在Debug&Verification下选择IBERT核,配置参考时钟为200 MHz、GTX协议相关的位置选择117、数据宽度为20 bit和线速率为4 G,生成bitstream。由于IBERT核只能独立使用,不可以插入工程,所以要注意配置和芯片参数一致,并且生成不依赖工程的独立bit文件,使用JTAG边界扫描链连接FPGA芯片,加载bit文件后,在chipscope软件中打开ibert console窗口,由MGT settings、DRP settings、Port settings和Sweep Test Settings功能框组成,如图7所示。

2.3 参数调节

在MGT界面查看MGT LINK status和PLL status,确认收发链路正常工作,在loopback mode中设置环回方式,设置发送端的参数,TX Data Pattern设置数据模型,采用BRPS-7 bit模型,在TX Diff output swing设置发送端的输出电压幅度,在pre-cursor和post-cursor调节预加重处理系数,通过数字示波器查看输出信号波形图。图8为调整前示波器测试眼图,图9为调整后眼图,通过比较发现眼图形状有明显改善。

图9 调整后波形眼图

设置好输出端口系数后,进一步调试接收端系数,在DRP Setting界面把工作模式转换为测试垂直眼图功能,如图10所示。调节REqualization和DFETAPOVERD,通过DFEEYEDACMON值查看内置眼图张开幅度,从而判定接收均衡器和反馈系数的值。从图7可以看到,当设置的参数比较理想时,眼图张开到最大值200 mV。

图10 工作模式设置界面

最后把工作模式转换为水平采样点测试功能,在Sweep Test Settings界面测试采样点位置和误码率之间的关系,如图11所示,发送端和接收端参数都理想时,采样点在0.375~0.87之间,误码率可以达到10-10,在MGT界面精细调节采样点,在0.598UI时可以达到10-13的精度,从而确定采样点最优位置。

图11 采样误码关系图

3 工程应用

SRIO协议是一种高性能、低引脚数、基于数据包交换的体系结构,是为满足高性能嵌入式系统需求而设计的一种开放式互连技术标准。图12为SRIO协议工作流图,数据在逻辑层和传输层按照协议打包处理后发送到物理层。

图12 SRIO工作流图

在FPGA的SRIO协议程序中,为了保证数据无误码传输,对物理层的收发端口修改参数,使用ibert验证过的参数设置。另外,采用/K27.7/码实现四通道绑定,采用/K29.7/码进行时钟补偿,采用/K28.5/码完成comma对齐功能,采用8 B/10 B编码提高数据变化率。在链路正常工作后,监测非8 B/10 B有效编码的计数器值,在参考时钟为125 MHz,线速率为4*3.125 GHz时,经过6 h的监测,计数器累计值一直为0,说明传输误码率低于10-13,链路的物理设置保证了SRIO的高速稳定无误码工作。

4 结束语

在工程设计中,FPGA的高速串行端口数据高速稳定传输至关重要。本文通过ibert工具调试电压摆幅、预加重参数、线路均衡和反馈参数以及时钟采样位置,得到误码率较低的理想参数,最后把相应参数以及串行技术用到SRIO协议中,进一步验证了本文方法的正确性。