航空电缆故障检测设备的ADC增频方法

2021-09-28李海亮

高 松,蔡 景,李海亮

(1.东航江苏有限公司,江苏 南京 211113;2.南京航空航天大学 民航学院,江苏 南京 211106)

飞机上的电源设备和其他系统设备之间主要是靠电气线路互联系统(Electrical Wiring Interconnection System,EWIS)传输电能和相关电子信号的,航空电缆作为EWIS系统的重要组成部分,其性能直接影响飞机的运行安全[1]。航空电缆如果在飞机的飞行过程中出现故障,很可能会导致电子信号或电能的传输中断,进而导致电器系统瘫痪,从而威胁到飞机的运行安全,甚至造成坠机事件[2]。

由于航空作业的风险和成本都很高,故要求航空电缆具有较高的安全性和可用性[3]。为了保证航空电缆的性能完整,必须对其故障进行严格的检测和排除,但是航空电缆的故障检测难度较大,主要有三方面原因:飞机上电缆数量庞大,例如在波音737上,电缆的总长度达到280 km;航空电缆通常是集束安装在机载设备与其他飞机结构之间的狭窄空间内,故障隐蔽性较高;航空电缆故障的检测空间和检测点数量有限。机务人员在进行电缆故障排除时,需要拆卸大量机载设备和飞机结构,会造成大量人力、物力和财力的浪费[4]。

对于电缆故障的检测方法从20世纪就已经开始了,最早的检测方法是电桥法,之后研究出了波反射法,目前最常见的电缆故障检测方法包括时域反射法(Time Domain Reflectometry,TDR)、频域反射法(Frequency Domain Reflectometer,FDR)、时频域联合反射法(Time-Frequency Domain Reflectometry,TFDR)等,其中TDR技术是最为成熟的[5]。

TDR技术根据反射脉冲与发射脉冲的时间间隔和相位关系即可判断故障位置和故障类型[6],原理十分简单,并且只需连接电缆的一端即可完成检测,操作十分方便。应用TDR技术检测电缆故障的关键问题是定位反射脉冲并识别其相位,针对该问题,目前主要有两种方法:比较电压法和ADC采样法[7]。

在比较电压法中,需要为电压比较器设置基准电压,然后通过D/A(Digital/Analog)转换器转换为模拟量后作为比较器的比较基准电压,高于该比较基准电压的输入脉冲信号通过比较器,而低于该比较基准电压的输入脉冲则不能通过。但是对于不同的航空电缆,反射脉冲的幅值是不同的,如果基准电压设置的较大,反射脉冲就可能无法通过比较器;如果基准电压设置的较小,干扰脉冲就有可能通过比较器,从而造成误判。同时比较电压法也无法绘制检测脉冲的波形,还会造成设备成本和系统复杂度的增加。基于以上原因,比较电压法在基于TDR技术的电缆故障检测中的应用较少[8]。

基于TDR技术的电缆故障检测设备一般采用ADC采样模块对检测信号进行采样,ADC采样频率在很大程度上决定了故障检测精度,ADC采样频率越大,故障检测精度越高[9]。为了使ADC采样的分辨率更高,目前主要有以下两种方法。

① 使用高精度ADC采样模块:目前ADC模块的最高采样率能够达到500 MHz左右,但是在实际的生产制造过程中,ADC采样模块的价格是与其采样速度紧密相关的,比如采样率为100 MHz的ADC的价格是20 MHz的15倍以上,100 MHz以上的ADC价格就呈指数增长。此外,更快的ADC对系统的时钟以及PCB(Printed Circuit Board)设计提出了更高的要求,同时为了配合高速的ADC 还需对存储系统和控制逻辑进行一些特殊处理,最终的系统开发成本显然也是相当高的[10]。

② 使用延时线法:该方法能够使ADC采样精度成倍增长,但是延时线法的关键问题就是延时线的构建,虽然随着大规模集成电路的发展,能够使延时线在一片集成芯片内构建,但是仍会大幅度增加整个TDR检测系统的复杂程度,同时会增加开发成本[11]。

针对上述问题,设计了一种应用于TDR电缆故障检测技术的ADC增频方法,这种方法能够在使用频率较低的采样模块的情况下,成倍增长ADC采样频率,从而极大地提高TDR电缆故障检测的精度。

1 基于TDR技术的电缆故障检测原理

为了确定反射脉冲的影响因素,需要对基于TDR技术的电缆故障检测原理进行分析。

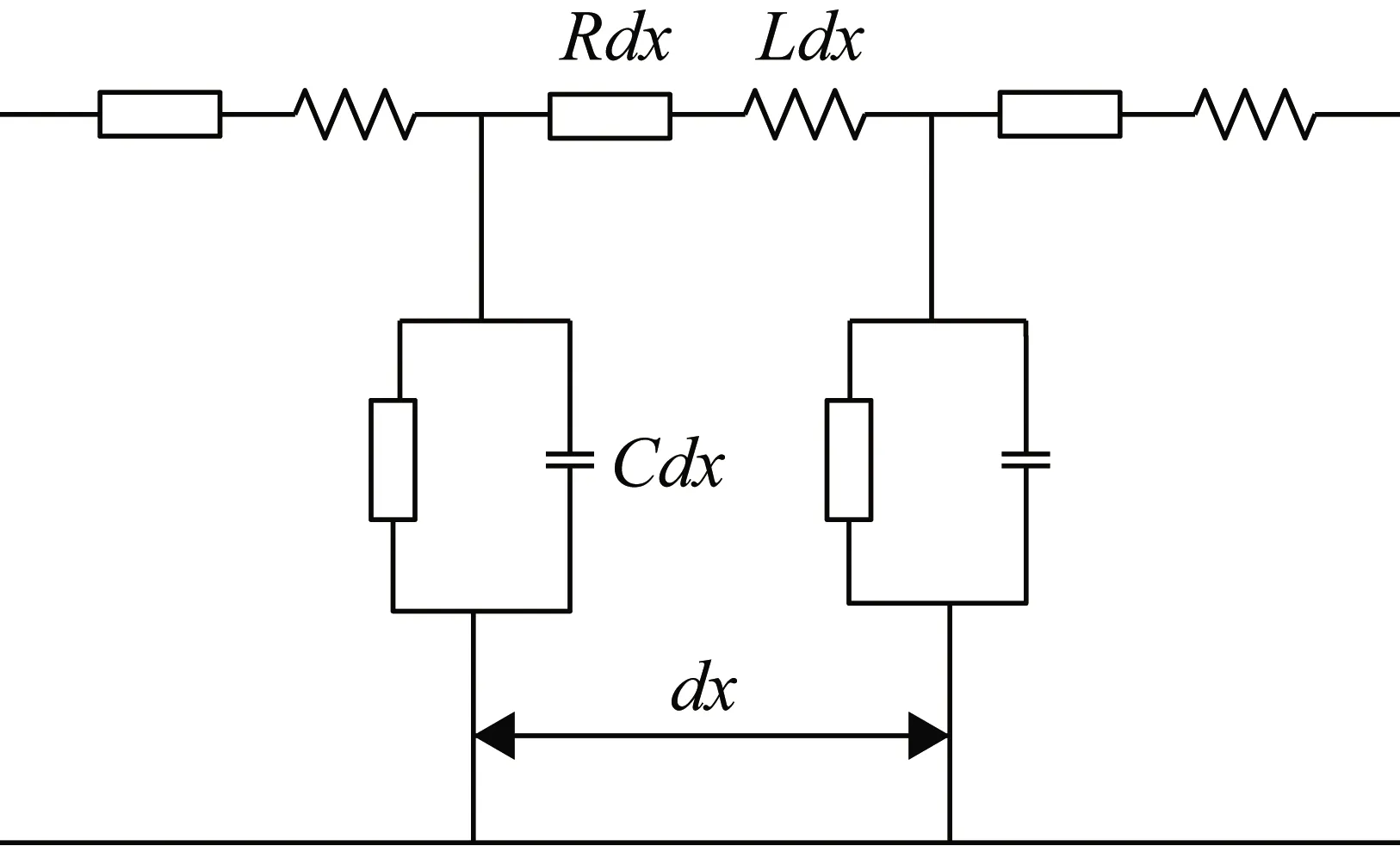

电缆作为传输线的一种,如果按照理想情况处理,能够将其视为均匀传输线,那么按照传输理论,电缆中的低压脉冲会沿着线路进行传输,故在描述电缆模型时,可以采用分布参数。电缆的等效分布参数模型如图1所示[12]。

图1 电缆的等效分布参数模型

图1中,C,R,L分别表示电缆单位长度的分布电容、电阻、电感。由此可以获得其波动方程,如式(1)[13]所示。

(1)

式中,x为脉冲在电缆中传输的距离;i为入射波电流;G为电缆单位长度的分布电导,G=1/R;u为入射波电压。由此得特征阻抗Z0[13]:

(2)

(3)

式中,ZL为负载或故障点对低压脉冲产生的阻抗,由式(3)可以看出:

① 如果ZL=Z0,则反射系数ρ=0,表示电缆无故障,发射脉冲被完全吸收,不会产生反射脉冲。

② 如果ZL→∞,则反射系数ρ=1,表示电缆中发生了断路故障,发射脉冲产生全反射,且反射脉冲与发射脉冲的极性相同。如图2所示。

图2 电缆断路时,入射波与反射波示意图

③ 如果ZL→0,则反射系数ρ=-1,表示电缆中发生短路故障,发射脉冲产生全反射,但反射脉冲与发射脉冲的极性相反。如图3所示。

图3 电缆短路时,入射波与反射波示意图

由上述3条结论可以判断电缆的故障类型,而电缆的故障位置是通过发射脉冲和反射脉冲之间的时间间隔Δt判定的,则故障点与测试点的距离L的计算公式[15]为

(4)

式中,v为低压脉冲在电缆中的传输速度。

由上述TDR技术的基本原理可知,电缆故障的位置和类型是通过反射脉冲与低压发射脉冲的关系判断的,而反射脉冲的极性及与发射脉冲的时间间隔是由低压发射脉冲的特性和被测电缆的属性决定的。故在低压发射脉冲的特性和被测电缆的属性均未发生改变的情况下,反射脉冲的极性及与发射脉冲的时间间隔相同。

2 等效采样法原理

由基于TDR技术的电缆故障检测原理可知,在低压发射脉冲和被测电缆的属性均未发生改变的情况下,反射脉冲基本不变,因此可以在参考时钟的一个周期内,通过多次向被测电缆中发射低压探测脉冲,获取多组采样数据,最后重构检测脉冲的波形,从而达到等效增加ADC采样频率的目的。

图4 等效采样法采样时钟的时序图

在故障检测的过程中,在第1次发射低压脉冲信号的同时启动第1次采样,即以参考时钟作为采样时钟,记录第1组波形数据;第2次发射相同的低压脉冲信号,经过1个延时单元后,启动第2次采样,即以延时1作为采样时钟,记录第2组波形数据;以此类推,记录下第3至第(n+1)组波形数据。

3 等效采样硬件系统的构成

为便于说明多重延时采样法的实现方法,设计了等效采样硬件系统基层构架,主要由数据运算和系统控制单元、FPGA(Field Programmable Gate Array)芯片、高速ADC等构成,具有结构简单、体积小、成本低、编程灵活、功能集成等特点,基层构架如图5所示。

图5 等效采样硬件系统基层构架

在等效采样的硬件系统中,数据运算和系统控制单元、采样和运算数据及相关程序存储单元可以使用树莓派实现。树莓派选用3B+型号,该型号的树莓派支持Python语言编程,降低了功能设计的难度;CPU采用64位1.4 GHz四核处理器,数据处理速度快;内存为1 GB LPDDR2 SDRAM,支持Micro-SD存储,SD卡容量选择64 GB,能够存储大量数据和应用程序;配置40个2.54标准的扩展口,包括总线接口和GPIO,便于数据和控制信号传输;配置一个标准HDMI接口,支持1080P分辨率,配合分辨率为1024像素×600像素的高清显示屏,满足了用户交互和结果显示的界面清晰度要求。

在等效采样的硬件系统中,FPGA芯片、FIFO(First Input First Output)、PLL(Phase Locked Loop)、有源晶振可以集成在FPGA模块中。FPGA模块选用黑金开发平台 AX301型号的FPGA,使用的是ALTERA 公司的 Cyclone IV 系列芯片,芯片型号为 EP4CE6F17C8。该FPGA配置50 M有源晶振,可以通过其内部的锁相环(PLL)对时钟进行倍频、分频或相位偏移。FPGA内置FIFO,是一种先入先出的存储器,能够暂时存储ADC采样数据,再由树莓派按顺序读取。

高速ADC采样模块的核心芯片选用ADI公司的AD9226芯片,此芯片为12位分辨率,最高采样频率为65 M。ADC采样模块不具备有源晶振,需要FPGA模块对其提供采样时钟。

4 等效采样的软件设计

4.1 等效采样时钟的产生

等效采样硬件系统中ADC模块的最大采样频率为65 MHz,低压脉冲在电缆中的传播速度一般为150~200 m/μs,若只以FPGA的50 MHz时钟作为ADC采样时钟对反射脉冲采样,对应的检测精度只有1.5~2 m。若需要检测精度达到0.5 m以内,那么ADC采样的频率需要增加到200 MHz。

为将ADC采样频率等效提高到200 MHz,需要以FPGA的50 MHz时钟作为参考时钟,并使用FPGA内置的PLL将50 MHz时钟分别偏移90°,180°和270°得到3种延时时钟,即延时1、延时2和延时3。以上述4种时钟分别为ADC采样时钟对检测波形进行采样,并在采样结束后,依照采样顺序对采样数据进行排序。

图6为基于PLL的延时时钟的功能仿真波形图,其中InClk为FPGA内置50 M有源时钟,Clk1,Clk2,Clk3分别为通过PLL偏移90°,180°和270°得到的时钟。

图6 基于PLL的延时时钟功能仿真波形图

功能仿真主要是验证和解决逻辑错误,无法验证器件的实际工作状态。时序仿真在布局布线后进行,主要验证和解决波形毛刺和延时即时序错误,这是器件实际工作时的状态。因此为了验证延时时钟能否满足多重采样的精度要求,需要对工程进行时序仿真。

图7为基于PLL的延时时钟的时序仿真波形图,其中InClk为FPGA内置50 M有源时钟,Clk1,Clk2,Clk3,Clk4,Clk5分别为通过PLL偏移0°,360°,90°,180°和270°得到的时钟。

图7 基于PLL的延时时钟时序仿真波形图

如图7中所示,为保证多重采样法的时钟精度要求,在等效采样硬件系统实际工作过程中,延时时钟1,2,3需要分别在参考时钟的基础上偏移90°,180°和270°,故需要以Clk2作为参考时钟,Clk3,Clk4,Clk5分别作为延时时钟1,2,3。

在故障检测的过程中,在第1次发射低压脉冲信号的同时启动第1次采样,以Clk2作为采样时钟,并将第1组采样数据暂时存储;第2次发射相同低压脉冲信号的同时启动第2次采样,即以延时1作为采样时钟,将第2组采样数据暂时存储;以此类推,存储第3和第4组波形数据。ADC采样数据需要先由FPGA内置的FIFO暂时存储,再由树莓派进行读取。每轮ADC采样中,FIFO的输入时钟应与ADC采样时钟保持一致,以保证ADC采样的数据完整且正确地写入到了FIFO中。

在上述ADC采样过程中,ADC采样时钟的选择是通过FPGA控制的。FPGA的工作时钟为InClk,当FPGA在时钟上升沿检测到采样启动信号之后,在启动采样的同时,会向ADC采样模块输送相应的采样时钟。ADC采样是在时钟上升沿进行的,故ADC采样的第一个点是在FPGA检测到采样信号之后采样时钟的第一个上升沿得到的。由图7可以看出,在每一个时钟周期内,Clk2,Clk3,Clk4,Clk5的上升沿依次向后,并且均在InClk之后,保证了每轮采样第一个点的可靠性,符合等效ADC采样的要求。

4.2 采样数据的排序

在每轮采样结束后,树莓派需要将存储在FIFO中的采样数据全部读取出来,针对该过程,在Verilog程序设计中采用状态机的写法。设置一个树莓派读取FIFO存储数据的状态寄存器,共3个状态h0,h1,h2。数据读取前若复位有效,则进入初始状态h0(计数器清0,不读取FIFO存储的采样数据)。h0状态表示若数据读取开始,则立刻进入h1状态,否则继续保持h0状态。h1状态表示树莓派正在依次读取FIFO的存储数据,计数器循环加1,若达到FIFO的数据深度m,则转入h2状态,否则继续h1状态。h2状态表示数据读取结束。状态转换图如图8所示。

图8 树莓派读取FIFO存储数据状态转换图

ADC采样数据传输到树莓派上后,树莓派需要对其进行排序。排序后第1个点是第1次采样的第1个点,第2个点是第2次采样的第一个点,以此类推,第(n+1)个点为第(n+1)次采样的第一个点,如此前(n+1)个点排序完成。同理,排序后的第(n+2),(n+3),…,(2n+2)个点分别为第1到(n+1)次采样的第2个点。按照上述方法将采样数据全部完成排序,其采样频率相当于(n+1)fclk,这就完成了一次等效采样。

上述等效ADC采样法在增加ADC采样频率的同时,会增加树莓派和FPGA的工作线程。如果未使用等效采样,只需进行一轮ADC采样,树莓派也只需读取一次采样数据。在上述的ADC等效采样过程中,需要进行4轮ADC采样,同时树莓派需要读取4次采样数据,在一定程度上增加了硬件系统的工作时间,降低了工作效率。但是树莓派和FPGA的工作速度很快,如果增加一轮ADC采样和一次树莓派读取数据过程,只需增加1~2 s的时间,而ADC采样频率会成倍增加,故障检测精度也会成倍增加,后续故障精确定位时间会极大减少,因此树莓派和FPGA工作线程的增加是符合要求的。

5 实验验证

为了验证等效采样法能否提高基于TDR技术的航空电缆故障检测精度,在同轴电缆的30 m处和双绞线的20 m处分别设置断路和短路故障,然后分别采用等效采样法和单一时钟采样进行故障检测,比较检测结果的精度,其中等效采样法的等效采样频率为200 MHz,单一时钟采样的频率为50 MHz。同轴电缆30 m处断路故障在使用等效采样法时得到的检测波形如图9所示,在使用单一时钟采样时得到的检测波形如图10所示。

图9 同轴电缆30m处断路故障的等效采样检测波形

图10 同轴电缆30m处断路故障的单一时钟采样检测波形

由图9和图10可以看出,使用等效采样法得到的检测波形采样点更为密集,分辨率更高,而使用单一时钟得到的检测波形采样点比较稀疏,分辨率较低。

针对同轴电缆30 m处的断路和短路故障,已知低压脉冲在该同轴电缆中的传播速度为0.16 m/ns,采用等效采样法和单一时钟采样分别进行10次故障检测,并对检测结果取平均值,如表1所示。

表1 同轴电缆305m处的断路和短路故障检测结果

针对双绞线的20 m处的断路和短路故障,已知低压脉冲在该双绞线中的传播速度为0.13 m/ns,采用等效采样法和单一时钟采样分别进行10次故障检测,并对检测结果取平均值,如表2所示。

表2 双绞线20m处的断路和短路故障检测结果

由表1和表2可以看出,相对于单一时钟采样,使用等效采样法能够明显提高同轴电缆和双绞线的故障检测精度。

6 结论

① 等效采样法能够成倍提高ADC模块的采样频率,从而大幅提高了基于TDR技术的航空电缆故障的检测精度。

② 由树莓派、FPGA、ADC采样模块构成的等效采样硬件系统,不仅结构简单,而且编程灵活,功能实现便捷。

③ 在实际的电缆故障检测中,等效采样法会受到一定的噪声干扰,重构的检测波形会产生偏差,故后续需要增加去噪算法,以减小噪声干扰带来的影响。