基于AMCC460GT和VxWorks的千兆网络通信系统设计

2021-09-13

为了适应高速总线通信的快速发展,满足千兆网络的通信技术要求,介绍了在原百兆网络终端通信板的基础上,开发基于VxWorks操作系统和AMCC460GT处理器的千兆网络通信终端板,使其数据处理能力和性能满足规范需求,并为基于VxWorks与AMMCC460GT通信系统架构的设计应用开辟了成功先例。

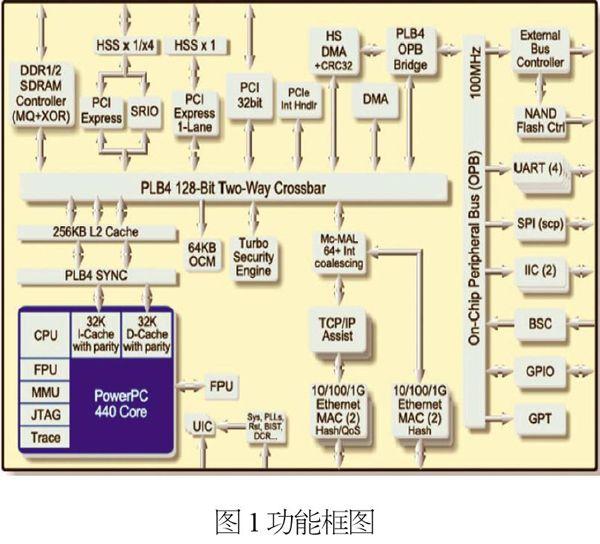

以AMCC公司的460GT通信处理器为核心,设计了一款网络通信系统平台。这个通信系统主要由增强型Power PC440处理内核(32-KB的指令和数据缓存)、256-KB的L2cache、64-KB的片上内存,DDR存储控制器(支持DDR1/DDR2)、PLB总线控制器、可编程中断控制器、PCI控制器、PCIE控制器、DMA控制器、10/100/1000以太网控制单元、安全引擎等众多模块整合而成。可以提供一路PCI总线、两路PCIE总线、一路USB、2个简单串口和4个10/100/1000自适应以太网接口等,工作频率最高可达1GHz,支持最大4G的DDR SDRAM内存,内部集成加密的模块。此外还提供一套扩展接口,包括通用的CPU控制总线(EBC总线时序可编程),可以灵活地挂接各种CPU方式读写的设备,实现控制功能;同时,在基于通信处理器的嵌入式微处理器的应用开发中,嵌入式实时操作系统是构成整个嵌入式通信系统不可或缺的核心软件。设计采用美国WindRiver公司的VxWorks6.7版本嵌入式实时操作系统,研究以太网络设备TCP/IP协议和各种硬件通信接口驱动在VxWorks下如何移植与实现。

AMCC460GT通信处理器

AMCC460GT硬件特性

AMCC460GT是基于440Core片上系统的PowerPC内核,拥有32 KB的指令和数据缓存,片上系统还包括DDR SDRAM存储控制器,4个三速率的以太网控制器。AMCC460GT的高度集成极大的简化了板级设计,图1显示的就是AMCC460GT單板功能框架图,在单板上集成了千兆以太网、和PCI、PCIe通用插槽,可以作为千兆网络系统使用。以下是系统板功能框图:

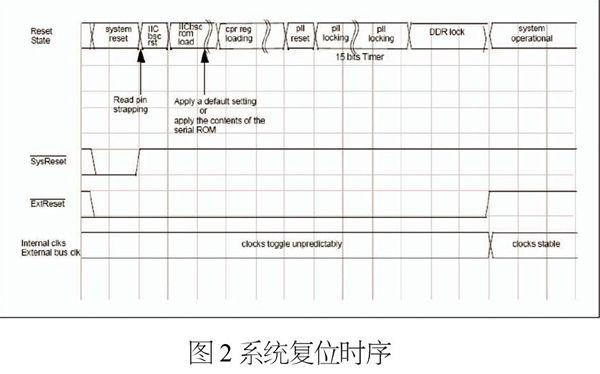

AMCC460GT复位设计

AMCC460GT提供四类复位信号SysReset、HISRRst、PCIORest、ExtReset,其中HISRRst为输入信号,PCIORest、ExtReset为输出信号。这4种信号全部为低电平有效。上电复位过程如图2所示。

AMCC460GT时钟配置

采用66.6667MHz时钟作为CPU的主时钟,用一个Cypress CY22381FX可编程的始终发生器产生如下3种时钟:11.0592 MHz时钟供给Uart串口、48 MHz时钟供给USB2.0,33或66 MHz时钟供给PCI,特别注意的是时钟发生器需要用一个22.1184MHz晶体作为时钟输入,才能输出较稳定的时钟信号。125 MHz时钟供给网口,460GT需要一个125M的参考时钟用于GMAC的发送端,这个时钟采用兼容设计,可以应用1121的125M锁相输出或者用独立晶振。25 MHz时钟供给Phy千兆以太网PHY88E1121R芯片。

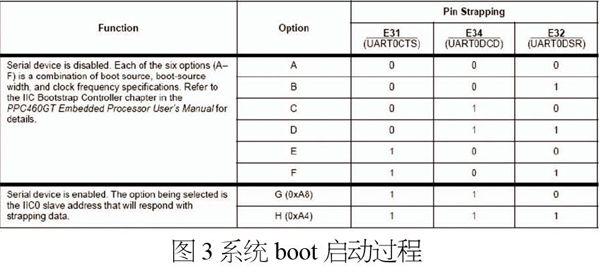

芯片的Boot启动过程

CPU在boot启动时,通过外部引脚的配置,来获得初始化参数,并在SysReset引脚信号由低电平恢复到高电平的时钟上升沿,读取参数配置,具体配置如下:

启动模式为Bootstrap Option B,CPU工作状态为CPU:800 MHz,DDR:400 MHz,PLB:200 MHz,OPB:100 MHz,EBC:100 MHz。所以,在系统板在上电之前一定要将UART0的(CTS:DCD:DSR)设计成0:0:1。否则系统工作不正常。

千兆以太网接口电路设计

AMCC460GT内部集成了2个处理模块:一个高性能嵌入式PowerPC 440内核和一个通信处理模块(MAL)。芯片内部拥有4个三速以太网控制器(Three.Speed Ethemet Con-troller,TSEC),实现了10 Mb/s、100 Mb/s和1 Gb/s三种不同速度的以太网协议接口控制。以下为千兆网硬件设计说明

AMCC460GT与PHY芯片的接口设计

AMCC460GT拥有4个TSEC以太网控制器,对4种不同的接口标准都提供了支持,它是完全符合8023协议规格的2.5V器件。在460GT与88E1121的连接中,GMII接口的发送接收参考时钟GTX CLK、RX CLK都是125 MHz,收发数据位宽度TXD[0:7]、RXD[0:7]为8bitS,还有收发使能信号TX EN、RX RV和收发错误指示TX ER、RX ER等。此外还有2个串行管理信号GMCMDC、GMCMDIO与PHY芯片连接。管理配置接口控制PHY的特性。该接口有32个寄存器地址,每个地址16位。

对TSEC控制器的初始化

460GT对TSEC控制器的初始化过程如下。只要按照顺序逐一完成相应的步骤,即可正确配置网络接口。选择TSECx控制器为GMII模式;设置MACCFG1寄存器,对MAC进行软复位;清除MACCFGl寄存器的软复位;设置MACCFG2寄存器,选择TSEC工作模式(如全双工或半双工、CRC校验是否使能等);设置MAC地址、物理地址;设置MII口的速率,使用MDIO对PHY进行初始化;清除并设置中断相关的寄存器I.EVENT和IMASK;设置Hash表和Hash寄存器:初始化接收控制寄存器RCTRL;设置DMA控制寄存器DMATRL:设置接收缓冲区大小;设置收发缓冲描述符(Buffer Descriptor,BD):设置MACCFG1中的收发使能位,完成TSEC初始化。在初始化TSEC的过程中尤其要注意在设置寄存器后,控制器处于不稳定状态,不能马上执行下一步的操作,需要作一定的延迟等待。因此,需要对嵌入式小系统板上的BCSR寄存器进行配置,使得网络通信处于正常状态。也可以使用某些操作系统提供的定时延迟来完成,如VxWorks中的taskDelay()。

对PHY芯片的设计与配置

为了使芯片工作在相应的物理地址、操作模式下,需要对88E1121芯片设备配置寄存器做出相应的配置,配置寄存器的各个位与芯片的配置管脚信号的对应关系如图4所示:

PHY芯片中的部分配置管脚必须与LED输出管脚相连,对应于各个LED输出管脚都有相对应的编码值,根据配置管脚对应配置寄存器的配置值要求,可以通过将相应的输出管脚与芯片配置管脚相连,实现对PHY芯片配置寄存器的合理配置,具体配置如图5所示。

Vxworks操作系统BSP的实现

在一般系统下使用Linux操作系统即可完成相关的任务功能,但针对任务实时性要求比较高的应用场景,采用了Vxworks操作系统来完成,本设计完成了Vxwork6.7版本在硬件平台的移植,其中关键的是操作系统底层BSP设计,所谓BSP通常是指针对具体的硬件平台,用户所编写的启动代码和部分设备驱动程序的集合,也就是依赖于硬件的那部分代码的总和。他所实现的功能包括初始化、驱动部分设备。本系统研究的BSP包含了处理器复位、初始化、串口驱动程序、网口驱动程序、Flash芯片驱动程序和PCI接口驱动程序以及必要的时钟处理。

在VxWorks系统中,对BSP的简单描述为介于底层硬件环境和VxWorks之间的一个软件接口,图6所示的BSP在系统中的层次清楚地展示了BSP与上层操作系统、应用程序以及底层硬件之间的具体关系。它的主要功能是系统加电后初始化目标机硬件、初始化操作系统以及提供部分硬件的驱动程序,具体功能包括:

Vxworks初始化流程:

所谓初始化是指从系统上电复位开始直到VxWorks开始初始化用户应用时的一段时间内系统所执行的过程。这个过程主要包括3个部分的工作。

CPU初始化:初始化CPU的内部寄存器,如状态寄存器、控制寄存器、高速缓存等。

目标机初始化:初始化控制芯片的寄存器、I/O设备寄存器,为整个软件系统提供底层硬件环境的支持。

系统资源初始化:位操作系统及系统的正常运行做准备,进行资源初始化,如操作系统初始化,存储空间分配等。

VxWorks能够访问的硬件驱动程序:BSP包括部分必要的设备驱动程序和相关设备的初始化操作。

BSP启动流程

经过修改后的BSP来编译启动引导程序bootrom和操作系统VxWorks,在获得bootrom映像后用编程器将映像烧入电路板的ROM,上电后将引导系统启动,过程如下:

①目标板加点之后,程序指针指向reset中断程序入口处,跳到rom入口地址,执行初始化程序romInit.s,设置机器状态字及其他硬件相关寄存器、然后禁止中断,初始化内存,并设置堆栈指针。

②跳到C程序bootInit.C的函数romStart0入口地址,根据堆栈中的参数决定是否清零内存RAM。根据不同的bootrom文件,把ROM中数据段和文本段拷贝到RAM(如果是压缩的,还要解压)。

③程序跳到RAM入口地址(文件bootConfig.c中函数usrlnitO),使cache无效,并清零bss段,初始化异常处理程序,进行板级硬件初始化sysHwlnit0。

④启动多任务内核kemellnitO。

⑤初始化串口,创建console终端设备,最后根据单板设计选择不同方式加载操作系统映像文件,如网口、Flash、PCI等。

实验结果

由于设备对功耗的要求,本系统针对不同状态下的情景进行了详细的功耗测试,以及针对千兆网络传输速度进行了极限测试,各项功能均达到要求。具体测试结果如下2所示:

本课题主要实现了基于Vxworks6.7在AMCC460GT硬件平台上的移植,并完成了千兆网络的通信功能,相比以往百兆网络通信,传输速度得到很大提升,相比之前Linux系统下的功能实现,任务实时效率得到了很大提高,保证了项目运行的安全性及稳定性。本文详细介绍了AMCC460处理器的相关设计方法,以及Vxworks系统底层BSP驱动设计相关方法,并在某通信控制終端上得以应用,该系统具有完善的底层监控与系统管理功能,并通过千兆网络实现数据的传输功能,可以满足多种应用领域与应用场景的需求。