基于0.18 μm CMOS加固工艺的抗辐射单元库开发

2021-08-19左玲玲周晓彬周昕杰

姚 进,左玲玲,周晓彬,刘 谆,周昕杰

(中科芯集成电路有限公司,江苏无锡214072)

1 引言

空间科技在增强国家实力和维护国家安全方面发挥着巨大的作用,目前国内对各种轨道卫星的需求十分迫切,因此对卫星控制系统的性能、可靠性、成本和研发进度等方面提出更高的要求。快速制造出满足各类卫星需要,在电性能、可靠性及抗辐射性能三方面均符合要求的国产抗辐射加固元器件成为关键,而基于抗辐射标准单元库的半定制设计方法能够大大简化设计,缩短设计周期,提高工作效率,因此设计一套能够得到广泛应用的抗辐射单元库是非常必要的。目前基于商用0.18 μm CMOS工艺,国内已有多个抗辐射单元库的设计[1-2],但在抗辐射性能及单元基本性能间未取得良好平衡,且未对单元库设计的全流程进行描述,本文基于0.18 μm加固工艺,采用工艺加固与设计加固结合的方式,完成了抗辐射单元库的全流程设计,成功开发了一套能广泛应用于工程的抗辐射单元库。

2 辐射加固方案

2.1 总剂量加固方案

总剂量加固方法包括设计加固和工艺加固,设计加固优势会降低对工艺的依赖性,缺点是面积大,设计和版图的灵活性不够,有些电路甚至无法设计,如环栅结构无法设计小尺寸MOS器件,造成电路设计困难。工艺加固则是基于常规的条栅MOS器件结构,采用工艺开发方式提升NMOS器件抗总剂量辐射能力,可明显减小版图面积及降低设计难度,本文采用的是工艺加固方式。

深亚微米工艺中,隔离区寄生晶体管的漏电已经成为CMOS器件中总剂量效应的主要问题[3-4]。0.18 μm加固工艺主要对浅槽隔离(Shallow Trench Isolation,STI)场区进行总剂量加固,通过离子注入的方式将STI/衬底界面处的P型硅反型阈值提高,从而抑制隔离区寄生晶体管的漏电通道开启。采用工艺加固后,1.8 V NMOS、3.3 V NMOS抗总剂量辐射能力分别从加固前的100 krad(Si)、50 krad(Si)达到了加固后的500 krad(Si)水平。STI场区注入的加固工艺会对器件的有效沟道长度产生影响,经实测NMOS管宽度W>0.5 μm后阈值电压及饱和电流变化幅度均在10%以内[5],满足电路实际设计需求,针对加固后NMOS管电参数的变化,重新抽取了器件Spice模型,以保证仿真精度。

2.2 单粒子效应加固方案

单粒子效应是指单个高能粒子穿过半导体器件的敏感区,在轨迹上沉积电荷,这些沉积电荷被器件所收集而引起的器件状态改变。单粒子效应主要包括单粒子闩锁效应(Single Event Latch-up,SEL)、单粒子翻转效应(Single Event Upset,SEU)、单粒子瞬态效应(Single Event Transition,SET)等。SEL是指CMOS工艺中固有的寄生可控硅(Silicon Controlled Rectifier,SCR)结构受高能粒子轰击而导通,导致电流不断增大而使器件失效甚至烧坏;SEU是指存储单元受高能粒子轰击而导致器件逻辑状态改变;SET是指组合逻辑受高能粒子轰击而产生的毛刺信号,如被存储单元采集,同样会产生单粒子翻转[6]。

SEL加固通常采用薄外延圆片材料或保护环版图结构的加固方式,机理均是抑制可控硅效应,但保护环加固方法明显增加版图面积,而薄外延在抑制可控硅效应时同样抑制了GGMOS寄生三极管的Snapback特性,对静电放电(Electro Static Discharge,ESD)设计提出了更高的要求,本文通过TCAD仿真确认N管有源区与P管有源区的间距、P管和N管源端到各自体接触的间距[7],保证400 K温度下寄生可控硅结构无法导通,以较小的面积损耗实现了SEL加固;SEU加固采用经典的双互锁存储单元(Double Interlocked Storage Cell,DICE)结构[8];针对SET加固,虽有各类延迟、C单元等滤除毛刺的加固方式[9],但对时序单元性能有明显影响,且加固后仍很难保证电路满足37 MeV·cm2/mg翻转指标,为实现关键控制逻辑的37 MeV·cm2/mg翻转指标,同时考虑到高可靠性电路设计需求,直接采用了内部自刷新的三模单元(Triple Module Redundant,TMR)进行全局三模冗余设计。

3 抗辐射单元库开发

确认抗辐射加固方案后,抗辐射单元库的设计流程与商用单元库基本一致[10],具体开发流程如图1所示,主要包括单元规格制定、单元逻辑及版图设计、单元特征化及布局布线文件抽取、单元库设计套件质量保证(Quality Assurance,QA)、硅验证。

图1 抗辐射单元库开发流程

3.1 单元库规格制定

单元库规格制定主要按照设计需求确定标准单元的数目、单元的高度、P/N管尺寸的比例、驱动能力等。由于SEL加固中增加了N管与P管有源区的间距,同时考虑到加固时序单元的布线空间,单元库高度采用了高性能单元库常用的12 Track。P/N管尺寸比例,常规单元库以速度为主要考虑因素,时钟单元以延迟及转换时间的平衡为主要考虑因素。单元种类以尽量满足各类数字电路设计需求为主,内核普通单元提供X1/X2/X4 3种驱动能力,反向器及缓冲器类器件提供X1/X2/X4/X8/X12/X16/X24 7种驱动以提升综合效率;I/O单元包括输入、输出、双向、电源、晶振、模拟等种类,输出包含2 mA/4 mA/8 mA/12 mA/16 mA/24 mA 6种驱动能力,具体单元种类及数量如表1所示,针对单粒子效应的加固单元加粗显示。

表1 抗辐射单元库种类及数量

3.2 单元逻辑及版图设计

抗辐射单元逻辑及版图的设计验证流程与商用单元库区别在于逻辑设计上时序单元为DICE及TMR结构,结构分布如图2(a)(b)所示,通过TCAD仿真确认在LET阈值为37 MeV·cm2/mg时的敏感节点间距,以保证时序单元的抗辐射性能,加固前后时序单元(1倍驱动上升沿双输出触发器,dfnrb1)常规参数仿真对比如表2所示,增加了内核及端口的加固时钟单元用于全局信号加固,组合逻辑加固以增加驱动能力、提升翻转临界电荷为主。

表2 时序单元加固前后基本参数仿真对比(TT/1.8 V/25℃)

图2 加固时序单元结构示意图

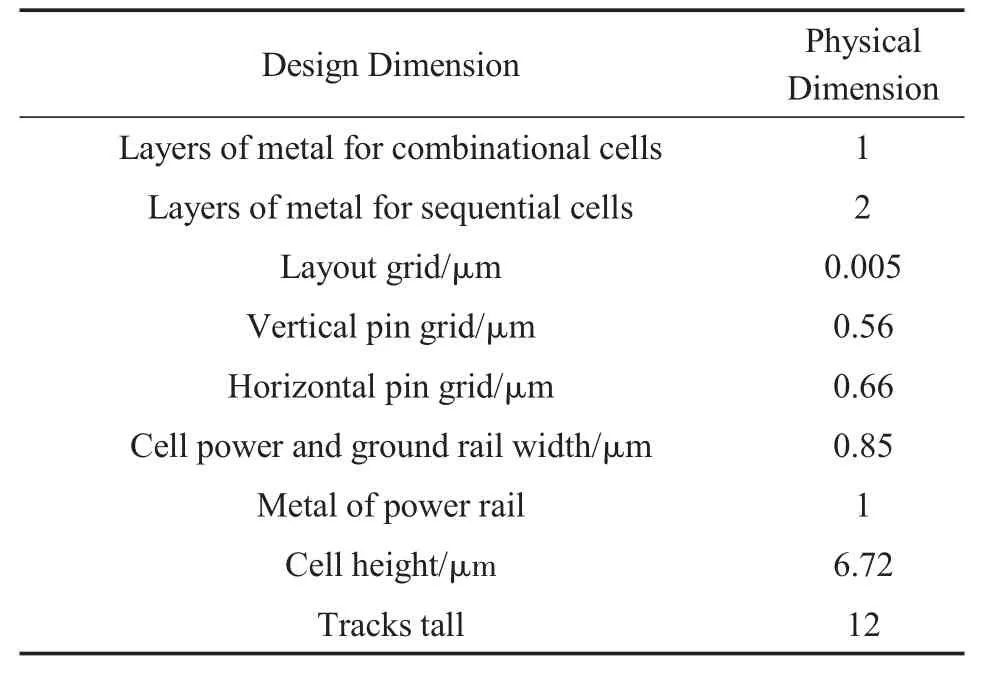

版图设计上主要增加了抗单粒子效应的规则检查,内核单元版图相关信息如表3所示。

表3 抗辐射内核单元版图基本信息

3.3 单元特征化及布局布线文件抽取

单元特征化是连接工艺与数字电路设计的桥梁,交付文件通过Synopsys Siliconsmart生成。单元特征化流程如图3所示,其原理就是以Spice仿真为内核,基于后仿网表,选取一定范围内的激励和负载进行仿真,提取时序和功耗信息。时序信息包括延迟类信息(Rise/Fall Delay,Rise/Fall Transition)和建立保持类时间(Setup/Hold,Recovery/Removal,Minimum Pulse Width),功耗信息包括静态功耗(Leakage Power)和动态功耗信息(Internal Power,Switching Power)。在抽取完相关信息后将其转换成lib和verilog格式作为单元库设计套件中的重要组成部分,最后将特征化信息以Datasheet形式供用户参考。

图3 单元特征化流程

布局布线文件通过Cadence Abstract Generator生成,基于单元版图gds文件及包含布线规则的tf文件,按照Core、IO、Corner3个类别进行配置,通过设置Pins、Extract和Abstract菜单,完成Technology lef及单元lef的生成。

3.4 单元库设计套件质量保证

最终生成的完整单元库设计套件如表4所示,设计套件至少需包含网表文件cdl、版图文件gds、时序功耗文件lib、功能仿真文件verilog、布局布线文件lef,这些文件覆盖了正向设计全流程,任何一个文件问题均会对设计过程产生不良影响,因此必须对单元库设计套件进行完整QA验证。

表4 单元库设计套件列表

完整QA验证至少需包括设计数据一致性检查、功能一致性检查、时序一致性检查以及后端设计检查。设计数据一致性检查主要确认cdl、lib、verilog、lef文件内单元数目、单元名称、端口名称是否一致;功能一致性检查主要确认cdl、lib、verilog文件内单元功能是否一致;时序一致性检查主要确认lib文件时序精度,确认lib、verilog时序条件描述是否一致,避免时序反标问题;后端设计检查主要确认lef文件是否适配自动布局布线工具,确认基于所有单元随机连接的网表不会产生错误,并完成布线后的整体版图DRC及LVS检查。

3.5 硅验证

抗辐射单元库硅验证主要进行功能、性能及抗辐射能力的流片验证。功能模块应包含所有内核功能单元,每个单元输出通过选择器进行选择,并提供功能全覆盖的测试向量组合,功能模块结构如图4(a)所示;性能模块通过链路测量基本单元性能,完成与晶体管级Spice仿真结果、门级静态时序分析结果的对比,组合逻辑通过环振测试基本组合逻辑单元在不同负载下的性能,反向器环振结构如图4(b)所示;时序逻辑通过链路测试锁存器时钟、数据到输出的延迟,测试触发器时钟到输出的延迟,结构如图4(c)所示;移位寄存器模块用于评价加固时序单元的抗辐射能力,单粒子试验时通过输出采样确认翻转次数,结构如图4(d)所示;通过整个测试芯片确认IO单元输入电平、输出驱动、ESD能力等。

图4 测试芯片模块

最终完成硅验证后的抗辐射单元库基本信息如表5所示,在实现抗辐射指标的前提下,与同工艺节点的普通商用单元库相比[10],对应的速度、面积、功耗增加的损耗在30%以内。

表5 抗辐射单元库基本信息

4 结论

本文基于0.18 μm CMOS加固工艺的辐射加固方案,提出了完整的0.18 μm抗辐射单元库的设计流程并完成测试芯片硅验证,目前抗辐射单元库已成功支撑多款抗辐射产品的开发,为后续大规模抗辐射数字电路设计奠定了基础。