基于超低电压的片上分组交换路由器设计

2021-08-07丁一欢何卫锋

丁一欢,何卫锋

(上海交通大学微纳电子学系,上海 200240)

0 引言

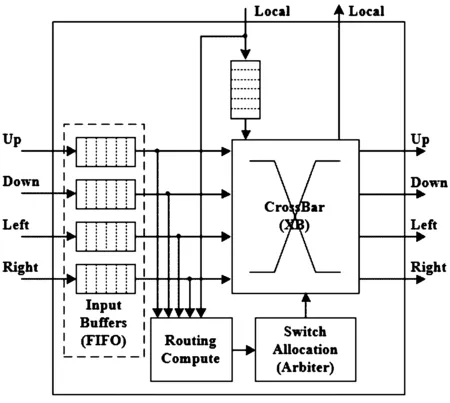

随着多核、众核技术的发展,越来越多的处理器核被集成到一起,因此也对片上多个处理器核的互连机制提出了更高的要求。NOC通过多个路由器组成特定的拓扑结构,实现了并行化处理数据通信,因此具有高带宽、高利用率和良好的扩展性[1]。目前NOC中最常用的数据交换方式是分组交换方式,即数据从源节点以分组的形式在路由器间进行存储、转发,直至到达目的节点,面向这种分组交换方式的路由器即分组交换路由器。图1展示了一个应用于2D Mesh网络的分组交换路由器,可以同时处理来自四个方向和本地处理器核心的数据包,并通过路由计算、仲裁等操作,将数据发往各自目标方向的输出端口。

图1 2D Mesh结构NOC中的Router

在NOC中,路由器是构成整个网络的核心部件,也占据了整个网络大部分的功耗开销。从硬件层面来说,为了降低电路的功耗,最常见的做法是将电路电压降低到晶体管近阈值或亚阈值区域,以显著减小动态翻转功耗[2]。

低电压电路的功耗比正常电压电路小很多,但会对PVT波动(Process,Voltage,Temperature variations)更加敏感。当发生制造工艺偏差、电压波动和外界温度变化时,电路的延时会受到严重的影响,甚至会导致功能错误。因此相较于正常电压电路,低电压下的电路设计需要有更多的时间裕度,这限制了低电压电路的最高工作频率。

在此背景下,错误检测与纠正(EDAC:Error Detection and Correction)技术[3-4]能够有效减小PVT variations的影响,放松对电路设计裕度的要求。EDAC技术通过在部分电路节点插入EDAC单元,来对电路中出现的时序错误进行检测和纠正,使得电路可以在较高的频率下保持功能正确。由于EDAC技术可以提高低电压电路的最高运行频率,因此也可以得到能耗的收益。

因此本文设计了一种可以工作在超低电压下的片上分组交换路由器,首先完成路由器的6级流水线结构后,将传统的REG时序单元替换为LATCH单元,并在部分关键路径终点插入了EDAC单元进行检错和纠错,最后基于一个4×4的2D Mesh NOC系统验证了此路由器的性能。

1 Router结构设计1.1 路由器基本结构

路由器的基本结构包括输入缓冲区、路由计算、端口仲裁和交叉开关模块,如图2。设计中的数据包设定为32比特,其中有8比特代表了此数据的源地址和目的地址(见表1)。因此输入缓冲区采用了位宽为32比特的异步FIFO。本文选择的路由算法为二维XY路由,Switch Allocation模块根据优先级轮询的结果对前级的输入端口申请进行仲裁,仲裁失败或下级已满时,会暂停部分流水线恢复数据。

表1 数据包格式

图2 Router基本结构

考虑到仲裁失败时数据恢复的需要,在计算路由前增加了一级流水线FO。由于FIFO读取和写入为2级,因此一共为6级流水线。Router的6级流水线结构如图3。

图3 Router流水线结构图

在以上描述的路由器流水线结构基础上,采用正沿触发LATCH(即PLATCH)作为主要时序单元实现了6级流水线。相较于传统的REG单元来说,由于LATCH对电平敏感,具有时间借用的特性,因此具有更强的容错性,也非常适合结合EDAC技术进一步提高电路的性能。

完成RTL代码后,将TSMC28nmHPC标准单元库在0.4V下重新特征化提取,并用于Design Compiler综合,然后在Prime Time中分析综合后网表的关键路径分布。根据路径分布结果,Router中的关键路径都集中于少数的Endpoints,因此可以运用EDAC技术进行优化,即在这些关键Endpoints处插入EDAC单元进行检错,从而提高电路的运行频率。由于关键Endpoints数量适中,因此不会导致EDAC单元插入开销过大。

1.2 路由器中的EDAC设计

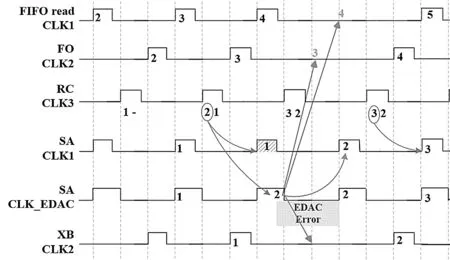

在本设计中采用的EDAC单元结构如图4a),由一个CLK_edac控制的Shadow LATCH和一个异或门来实现检错。CLK_edac频率和CLK相同,但高电平时间比CLK更长一些。EDAC单元的检错过程的波形示意图见图4 b)。在图4 b)最后一个周期,正确数据D在CLK的下降沿到来后才翻转,发生了时序错误,导致Error信号为高,此时的Q_edac的值才是正确值。EDAC单元的检测窗口大小约为CLK_edac与CLK的高电平时间之差。

图4 a)EDAC单元结构图;b)EDAC单元纠错过程波形示意图

在Router电路中,根据Primer Time分析的路径分布,最易发生时序错误的关键路径集中在计算arbiterfail信号和仲裁结果arbiter信号的路径上。因此在这两类信号后插入EDAC单元进行检错,具体的方法是将图4 a)中的EDAC CELL接到相应的数据端,通过相应的Error信号判断是否发生时序错误。所插入EDAC单元的数量为20个。

插入EDAC单元进行检错后,纠错机制可以有两种:

(1)若后级路径为短路径,通过Error信号选择 Q_edac 作为正确的输出,送到后级运算即可。

(2)若后级路径也为长路径,则必须立即将前后级的流水线暂停,同时通过Error选择Q_edac作为本级输入,下一个周期就可以正确运算。

图5 EDAC纠错机制图解

其中第1种方式可以进一步简化为直接将Q_edac作为正确的输出。如图6所示,在本设计中,当检测到SA级出现时序错误,会立即暂停FIFO、FO、XB级流水线,并将EDAC CELL中的正确值恢复到SA级相应的输入端。

图6 EDAC纠错波形图

插入EDAC单元后的Router流水线结构图如图7所示。

图7 插入EDAC单元后的Router流水线结构图

1.3 时钟设计

由于所提出的Router设计采用了LATCH为时序单元,采用的时钟会与传统REG单元有所差别,此处简单介绍本设计中采用的时钟和时钟产生模块。基于PLATCH结构的流水线一般采用两相时钟控制,相邻两级的时钟高电平不会重叠。但与此同时,如果采用PLATCH设计,两相时钟的周期需要变成REG电路时钟周期的两倍,才能确保功能正确。

针对这一点,本文创新性地采用了三相时钟控制,时钟周期理论上只需要变成REG电路的3/2倍,既保持了不需要进行短路径填充的优点,也减小了对运行频率的影响。需要注意的是,采用三相时钟控制后,各级数据不再是同步更新。因此当STALL信号触发时,也不需要立即暂停前级流水线。可以将相关控制信号传到前级打拍再处理,这也进一步简化了数据恢复的控制逻辑。

在本文提出的Router设计中,由CLK1控制FIFO级读数据操作和SA级,由CLK2控制FO级和XB级,由CLK3控制RC级和FIFO级写数据操作。设计中的三相时钟和clk_edac的产生电路[5]如图8。设计中采用的CLK_edac占空比为1/3。

图8 a)时钟产生模块电路图 b)时钟产生模块波形图

2 版图实现与仿真分析2.1 版图实现

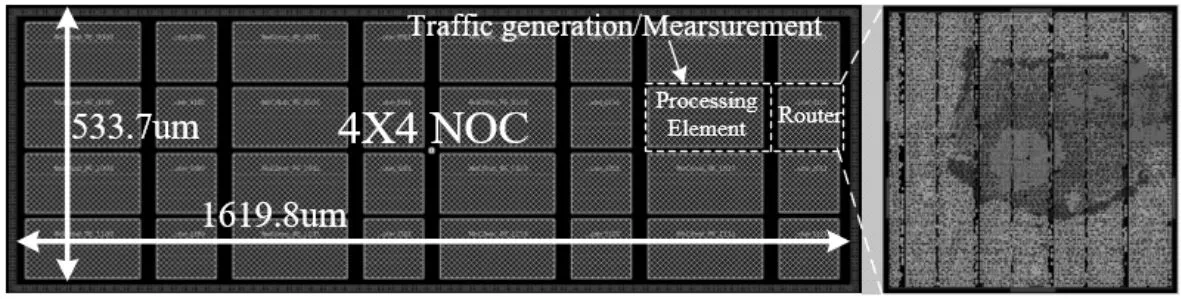

将前文描述的综合网表基于IC Compiler布局布线,得到了最终的4×4 2D Mesh NOC版图,如图9所示。版图面积为1619.8um×533.74um,包含16个路由节点。每个节点包括一个面积为114.1um×113.4um的Router和一个等高的数据处理单元。

图9 4×4 2D Mesh NOC版图

2.2 仿真设置

为了验证所设计的路由器的性能,搭建了一个4×4的2D Mesh NOC作为testbench。此网络中含有16个按照设定的数据包格式收发数据的处理单元,16个所设计的路由器,以及前文所描述的时钟产生模块。数据处理单元具有收发数据和计数的功能。数据处理单元发送数据可以有两种模式:轮询模式和用户配置模式。我们采用的是轮询模式,即按照0000~1111的顺序依次向其他地址发送数据。另外为了比较EDAC设计的优势,将不具备检错纠错功能的Router作为Baseline电路,在同样的testbench和输入激励下也进行仿真。

2.3 性能分析

仿真关注的性能指标包括NOC网络的最高工作频率、丢包率、吞吐率以及Router模块的功耗开销等。

本文设计的Router在测试中得到的正常运行最小时钟周期为16.2ns,即整个NOC网络最高工作频率为61.73MHz。在时钟周期小于16.2ns时,发生时序错误,导致出现丢包,对不同周期下同样时间内的丢包数和接收数进行统计,得到曲线如图。图10的横坐标为仿真设置的时钟周期大小,纵坐标为丢包数与接收数,由图可见,随着时钟周期减小,丢包越来越频繁,接收到的数据包越来越少。由于每次丢包后会请求重传一次数据,因此这会导致网络的总运行时间迅速增加。

图10 网络丢包数与接收数随周期变化曲线

由丢包数和接收数可以计算得到丢包率随周期变化曲线,对不具有检错纠错功能的Router也进行了同样的仿真后,将两者丢包率曲线进行对比。由图11所示,可以看到采用EDAC设计的Router丢包率始终小于Baseline电路,且在16.2ns时丢包率已经降为0,而Baseline电路直到17.4ns时才不再丢包。因此采用EDAC设计可以提高Router对时序错误的容忍能力,并使Router的工作频率提高了7.4%。

图11 网络丢包率随周期变化曲线

此外随时钟周期减小,电路丢包率的增长趋势也有所不同。在图11的A区域,两种Router的丢包率都随周期减小而保持缓慢的增长,且丢包率数值接近,基本在10%以内。当时钟周期继续减小时,如B区域所示,Baseline电路的丢包率开始迅速增大,此时采用EDAC设计的Router丢包率曲线仍维持A区域的趋势不变,曲线斜率明显更小。注意到在时钟周期为13.2ns时,Baseline电路的丢包率达45%,此时采用EDAC设计的丢包率仅为15%。当时钟周期小于13.2ns时,即为图11的C区域,Baseline电路丢包率的增长趋势又趋于平缓,而采用EDAC设计的电路丢包率随周期减小开始迅速增大。因此整体而言在图11的B区域内,采用EDAC设计的优势最明显。

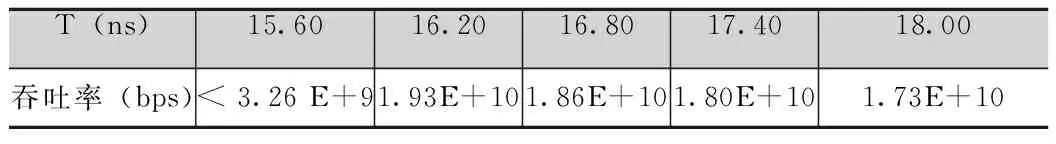

当以最小周期16.2ns运行时,整个NOC网络吞吐率为1.93E+10 bps。由于不出错时发送完所有数据需要的周期数固定,当运行周期大于16.2ns时,运行时间会变长,网络吞吐率随之下降;当运行周期小于16.2ns,由于出现大量丢包,需要大量的重传数据导致时钟周期数增大,吞吐率也会迅速下降。因此网络最大吞吐率为1.93E+10bps,而Baseline电路的最大吞吐率在17.4ns处得到,为1.80E+10bps。

表2 网络吞吐率与时钟周期

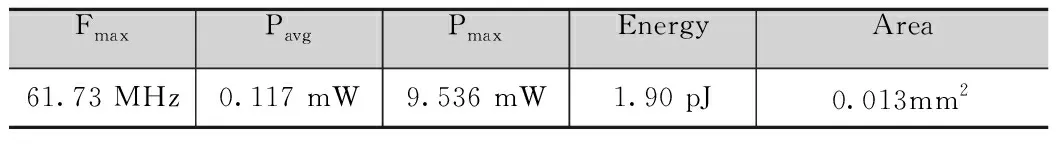

除了网络运行频率和吞吐率有所提升以外,由于采用了超低电压设计,NOC中路由器的整体功耗也很小。对于单个路由器设计,以Router_0000的各指标为例。

表3 Router_0000性能指标

根据PrimeTime中的功耗报告得到Router_0000中各类型功耗分布图和各个子模块的功耗分布图,分别为图12 a)和图12 b)。由图12 a)可以看到时钟网络造成的功耗开销占了50%左右,同时所有单元的静态功耗也占了约50%。这一点也符合最小能量点(MEP)的特征。

图12 a)Router_0000中各类型功耗分布图;b)Router_0000子模块功耗分布图

由图12 b)可以看到在子模块中,输入缓冲区的FIFO功耗开销最大,RC模块和SA模块次之。显然频繁的数据读写会导致FIFO相对于其他模块消耗更多的能量,此外由于RC模块进行了优化设计,添加了备份数据的存储,SA模块增加了EDAC单元和更多的控制逻辑,因此也会有较多的功耗开销。

Router_0000的峰值功耗为9.54mW,电路功耗随时间的变化曲线呈现周期性的规律。

图13 Router_0000瞬时功耗变化曲线

对NOC网络中16个Router的功耗信息进行了统计,结果如图14,图中每个点代表一个Router的Pavg。

图14 16个Router的平均功耗

由图14可见,在4×4的NOC网络中,功耗最低的是处于4个角处的Router(即Router 6、7、10、11),其次是边缘上的Router(即Router 2、3、5、8、9、12、14、15),功耗最大的是网络中心位置的Router(即Router 1、4、13、16)。这是由于处于中心位置的Router需要处理更多方向的数据,因此中心位置的Router也是最容易发生堵塞的。将这16个Router的Pavg结果取平均后,可以得到:所设计的Router采用TSMC 28nmHPC工艺实现,在0.4V,61.73 MHz下运行时,平均每周期能耗仅为2.07 pJ。

3 结语

本文结合低电压EDAC(Error Detection and Correction)技术和三相时钟流水线设计的优点,提出了一种面向低电压的片上分组交换路由器,并在一个4×4的2D Mesh网络中验证了性能。基于TSMC28HPC工艺的后仿结果表明,在0.4V下该路由器最高工作频率达到61.73MHz,比Baseline电路相比提高了7.4%,且每个路由器一个周期的平均能耗仅为2.07 pJ。