基于FPGA+ARM的多路光栅数据采集系统设计

2021-06-26张立李少康李高益

张立,李少康,李高益

(西安工业大学,陕西西安,710021)

0 引言

光栅编码器作为一种重要的高精度位移测量器件,常用于运动伺服系统中,实现对运动位置的精确反馈[1]。随着光栅编码器研制技术的发展,其测量精度、速度以及输出信号带宽也越来越高,因此,相应的对光栅信号采集及传输系统提出了更高的要求,要求采集系统具备采集速率高,传输速度快,抗干扰能力强等特点[2]。

传统的光栅数据采集系统多采用单片机或者专用的采集芯片作为处理器,存在采集速率低和灵活性较差的缺点[3]。在信号传输上多采用RS232、RS485或CAN等传输方式,存在传输速度低的缺点,并且目前电脑已经逐步淘汰这些接口,给测控系统设计及使用带来较大障碍[4]。随着“工业4.0”及“互联网+”的发展,对数据的通信传输要求智能化和远程化[5]。本文提出了一种基于FPGA+ARM的光栅信号采集及传输系统,充分发挥了FPGA的并行逻辑控制能力和ARM的数据处理能力,以TCP/IP协议完成了对数据的高速稳定传输,使得测控系统接口统一化,实现对数据的远端测控,具有采集速度快、带宽高、传输速度快和稳定等优点,可以完成对光栅数据高速的采集、处理和传输。

1 系统整体结构

基于FPGA+ARM的多路光栅数据采集系统的整体结构如图1所示。多路光栅的输出信号经过差分转换及隔离电路后进入FPGA中,FPGA对多路光栅数据进行数字滤波、同步采集以及数据存储后通过FSMC总线与ARM端进行数据通信,ARM端再以TCP/IP协议以网口的形式将数据发送至上位机。

图1 系统的整体结构

2 系统硬件电路设计

2.1 光栅信号预处理电路

光栅信号输出为RS422差分信号,输出高电平为5V,FPGA为低电压逻辑电平,高电平为3.3V,为了便于FPGA对信号进行采集,需要设计相应的信号调理转换电路将5V的RS422差分信号转化为LVTTL电平信号。本次设计采用AM26LS32差分接收芯片,实现对测头差分信号到单端信号的转换,对信号采用了TLP2362型高速光电耦合器,降低了信号的噪声干扰的同时实现了逻辑电平的兼容。

2.2 FPGA+ARM设计

FPGA具有高度并行数据处理能力,可以很好的保证对多路光栅数据采集的并行性和实时性,ARM具有强大的数据处理以及灵活的进程运行能力[6]。结合FPGA和ARM的优势,设计FPGA+ARM的数据采集系统结构,ARM作为主处理器,读取FPGA采集到的多路光栅数据,通过对LwIP协议栈移植,控制以太网实现数据到PC端上位机的传输[7]。FPGA主要负责多路数据的实时采集,将采集数据进行临时存储,与ARM进行数据传输。

FPGA芯片选用Altera公司的EP4CE22C8芯片,其拥有6272个逻辑单元完全满足本系统的设计。ARM处理器选用ST公司生产的高性能ARMCortex-M4,其拥有1MB Flash,最高主频可达到168MHz,并且支持以太网通信。

FPGA和ARM之间通过FSMC总线连接,如图2所示。FSMC总线接口由16位数据总线、16位地址总线及其它FSMC总线端口。

图2 STM32与FPGA接口模块

2.3 网络接口设计

STM32F407自带以太网模块,只需外界PHY芯片即可完成以太网通信实现10M/100Mbit/s的数据传输速率,STM32与外部PHY芯片使用RMII接口进行连接,本次设计使用LAN8720A作为PHY芯片。以太网连接器采用HR911105A,其内部集成网络变压器,以太网通信电路原理图如图3所示。

图3 以太网通信电路

3 系统的软件设计

系统的软件设计主要包括FPGA端对光栅信号采集程序、ARM端数据处理、以太网通信程序以及PC端上位机软件部分的设计。

3.1 滤波程序设计

光栅的输出信号可能存在噪声干扰,需要对毛刺进行滤除,基本思想是在系统时钟的上升沿对光栅信号进行采样,稳定的光栅信号在几个系统时钟信号边沿采样时都维持电平稳定,否则为毛刺信号[8]。图4所示为两路光栅信号滤波模块的RTL图,A、B信号经过w个触发器后,如果w个触发器的每一位输出均为1时才输出1,每一位都为0时才输出0,否则维持上一时钟信号的采样值。这样小于w个时钟周期宽度的毛刺信号将被滤除。

图4 光栅信号滤波RTL图

3.2 光栅信号计数处理程序

光栅在移动过程中,输出相位相差90°的两路方波信号A和B,若正方向移动,A超前B信号90°相位,若反方向移动,A滞后B信号90°相位,因此,根据两信号的相位关系即可确定出光栅尺的位移方向[9]。根据对A、B信号的相位关系进行分析,得出如图5所示的状态变化及计数操作关系,当A、B两信号的电平状态相对变化为00→10→11→01→00中的一种时,计数器执行加1操作,当电平状态相对变化为00→01→11→10→00中的一种时,计数器执行减1操作[10]。以此便可实现对光栅信号的四倍频辨向计数。

图5 计数操作图

3.3 以太网通信设计

针对于STM32F407微处理器,选择轻量级的LwIP作为以太网协议栈,将LwIPTCP/IP协议栈移植在STM32F407上,在应用层实现网络双向传输的数据传输系统。以太网通信函数图如图6所示,调用ETH_BSP_Config()和LwIP_Init()用于PHY芯片配置和初始化LwIP协议栈,设置完IP地址、子网掩码和网关后使用TCP_Client_Init()初始化TCP客户端,之后便可以进行数据发送与接收。

图6 以太网通信函数框图

3.4 上位机软件设计

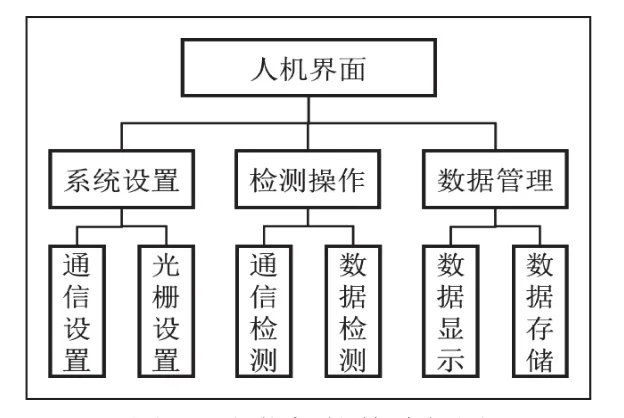

光栅数据采集系统的上位机软件使用VS2019进行软件编程,整个上位机功能主要由系统设置、检测操作和数据管理组成,上位机软件功能图如图7所示。

图7 上位机软件功能图

所设计程序程序界面如图8所示,在系统设置区对通信以及光栅参数进行设置,上位机与下位机连接成功后在数据接收区即可对各光栅进行置数,并采样到光栅当前的位移及速度,消息区显示工作状态及相应警告。

图8 上位机系统界面图

4 实验验证

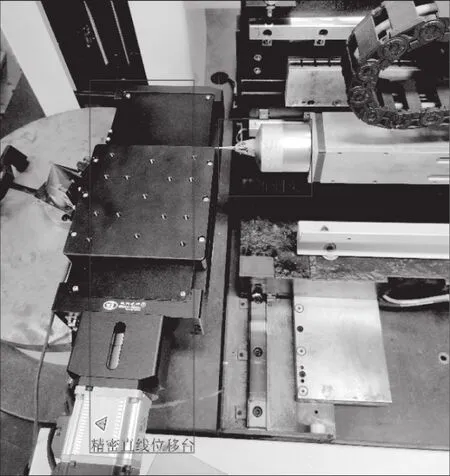

本次设计以安装有RSF公司生产的AKMS15TTL×100型号光栅的直线位移台为实验对象,其脉冲当量为0.1,采用设计的光栅信号采集系统进行数据采集传输,搭建如图9所示实验平台,将位移台固定在C40测量机平台上,使用C40测量机对位移台的实际位移进行测量,在上位机中监测所设计的多路光栅数据采集系统采集到的位移台的光栅数据。

图9 光栅采集系统实验图

通过对比上位机数据与C40测量机采集到的位移数据,二者差值如图10所示。

图10 测量数据差值

由图中可得,二者误差最大值发生在第10个点,差值为0.5,由于测量机存在一定的测量误差,可以认为设计的光栅数据采集系统测量结果准确无误。

5 结论

本文设计了一种基于FPGA+ARM的光栅数据采集系统,实现对多路光栅数据的高速采集与传输,具有采样速率高,传输速度快,抗干扰性强等优点。通过ARM端对以太网协议栈的移植,实现了高速稳定的以太网通信,实现了整个系统的以太网远程控制,解决了以往光栅采集系统通信速度以及与PC端互联通用性方面的不足。