循环码编解码电路分析与实现

2021-06-16刘新红

刘新红

(北京信息职业技术学院,北京,100018)

0 引言

循环码编解码电路结构简单,易于实现。有广泛应用。

根据纠错位数的多少,解码器复杂程度不同,纠多位错的解码器电路实现复杂一般用查表法实现[1-3],纠1位错一般用电路实现[4-5],当然纠1位错也可用查表法[6-7]。

纠1位错的电路实现方法文献[4-5]给出了实现电路但并未分析电路结构。本文以(7,3)循环码为例基于Simulink仿真对编解码电路工作过程进行详细分析,得出基于移位寄存器的循环码编解码电路的设计方法。

1 编码器

(7,3)循环码生成多项式如式(1)所示。

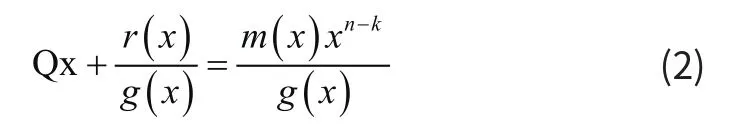

信息多项式m(x)、生成多项式g(x)、监督多项式(余数多项式)r(x)满足式(2)。其中Qx是商多项式。

以m(x)=x2+ 1即输入信息位101为例列竖式计算余数r(x)的过程如式(3)所示。

编码器仿真电路图如图1所示。

由移位寄存器实现。4位循环移位寄存器,输入编码信号101,附加4位监督位0000,故输入信号设为1010000。3个时钟周期输入的3位信息位产生4位监督位,4位移位寄存器中的值就是余数,也就是监督位的值。

反馈控制信号取值1110000,也保证前3位真正的信息位反馈进入移位寄存器。

输出控制信号取值0001111,保证输出信号前3位为信号后4位为移位寄存器中产生的监督位。

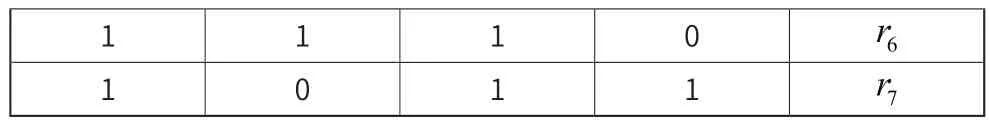

仿真波形图如图2所示。

波形图的下波形为输入的被编码信号,上波形为输出的产生了监督位的编码后信号。

从仿真波形看,输入的编码信号为1010000,输出1011100,产生的监督位正确。

前3个时钟周期信息位101送入4位移位寄存器产生4位监督位。每个时钟周期低位向高位循环移1位,第一个时钟周期信息位1和D4中的0模2加后得1和 D2、 D1的值模2加后移入高位,移位后得 D4D3D2D1=0111,同理,第2个时钟周期信息位0和D4中的0模2加后得1和 D2、 D1的值模2加后移入高位,移位后得 D4D3D2D1=1110,第3个时钟周期信息位1和D4中的1模2加后得0和 D2、 D1的值模2加后移入高位,移位后得 D4D3D2D1=1100,这时的寄存器中的值便是最终的余数也是编码时的4位监督位。说明循环移位寄存器这种电路结构能够实现编码功能。编码输出电路控制信号取值0001111,使输出7位码字1011100前3位为信息位101,后4位为监督位1100。

根据上面分析,可以得出,移位寄存器电路仿真除法过程,移位寄存器位数为余数(监督位)位数,组合逻辑部分由生成多项式决定,移位寄存器最高位和生成多项式中系数为1的位对应的寄存器位输出模2加作为高位寄存器输入。实现如果最高位为1,模2加上生成多项式对应的2进制序列并移位1位,如果最高位为0直接移1位即可。

2 解码器

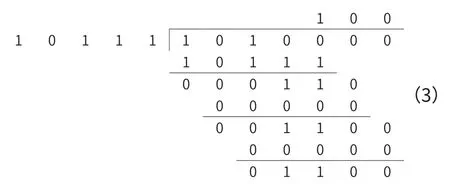

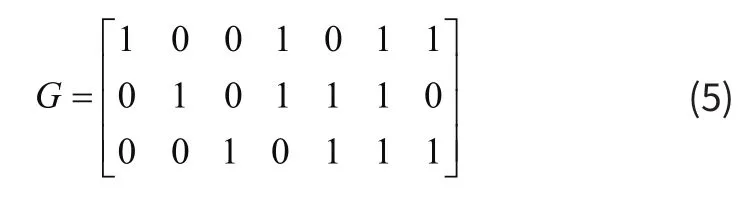

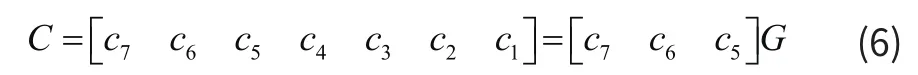

接收码字在不出错时除法余数为0,也就是除法器4位移位寄存器最后结果为 D4D3D2D1=0000,(7,3)循环码生成矩阵如式(4)所示。

其系统码形式如式(5)所示。

图2 编码器仿真波形图

由生成矩阵得到发送码字C如式(6)所示。

由此可得监督位 c4c3c2c1和信息位 c7c6c5的关系如下。

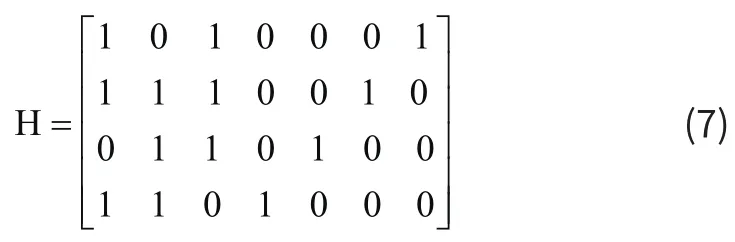

可写出监督矩阵如式(7)所示。

监督矩阵和发送码字存在式(8)的关系。

接收码字R和监督矩阵H、校正子S关系如式(9)所示。

由此得出校正子各位和接收码字各位之间的关系如下。

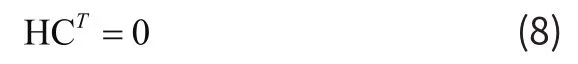

可得出如表1所示校正子和错误位置关系。

表1

1 1 1 0 6 r 1 0 1 1 7 r

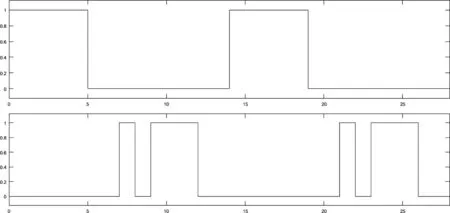

解码仿真电路如图3所示,仿真波形如图4所示。

解码包括校正子产生电路和错误图样产生电路。输入码字1111100,正确码字1011100,输出1011100,由此看出解码电路正确识别并纠正了错误。

输入码字1111100一方面进入循环移位寄存器产生校正子,一方面进入7位寄存器,7个时钟周期码字全部进入后产生校正子,在后7个时钟周期输入码字依次从寄存器输出并逐位和错误位模2加纠错后输出。

纠错的起始状态为纠r7,如果r7有错则S=1011,将s2取反相与输出为1表明有错模2加到r7上即可纠正该位错误。如果r7无错,S≠1011,与门输出0,r7值无改变。如果r6有错则S=1110,先在4位移位寄存器中循环移位1位得 D4D3D2D1=1011将D2取反相与输出为1表明有错模2加到r6上即可纠正该位错误。如果r6无错,S≠1011,与门输出0,r6值无改变。分析一下r1有错的情况。如果r1有错则S=0001,经过6个时钟周期r1才移出,D4D3D2D1=0001依次变为 D4D3D2D1=0010、D4D3D2D1=0100、 D4D3D2D1=1000、 D4D3D2D1=0111、D4D3D2D1=1110、 D4D3D2D1=1011将D2取反相与输出为1表明有错模2加到r1上即可纠正该位错误。如果r1无错,S≠0001,与门输出0,r1值无改变。对每位错误的情况进行一一分析后得出结论纠错电路能够纠正各位错误。纠错电路的逻辑结构基于r7有错的情况分析得出,适用于各位有错的情况。

因此,纠错组合逻辑电路根据接收码字最高位有错时的校正子取值确定。把最高位有错时校正子各位相与(如某位为0则取反)后作为错误位模2加到接收码字相应位上纠正错误。

每个码字检错纠错需14个时钟周期,移位寄存器反馈控制信号取00001111111111,前4个时钟周期接收码字的前4位移入4位移位寄存器,此过程反馈不起作用避免寄存器中原数据的影响。输出控制信号取00000001111111,保证后7个时钟周期输出纠错后的码字。

图3 解码器仿真电路图

图4 解码器仿真波形图

3 结束语

基于移位寄存器的循环码编解码电路结构简单,易于实现。通过分析电路工作过程得出,编码电路结构由生成多项式决定,移位寄存器最高位和生成多项式中系数为1的位对应的寄存器位输出模2加作为高位寄存器输入;解码器校正子产生电路由生成多项式决定,纠错电路的逻辑结构由接收码字最高位有错时的校正子决定。