基于Simulink的对偶序列跳频通信链路及门限设计仿真*

2021-06-15孟庆斌全厚德朱世磊

孟庆斌,全厚德,朱世磊

(陆军工程大学石家庄校区,河北石家庄 050003)

当前无线通信无处不在,每时每刻都在丰富着人们的生活和习惯,传输速率不断提高,但是系统抗干扰能力不足,严重限制了其在军事领域中应用[1]。为此,国内外学者展开深入而广泛的研究。跳频系统可以通过频率变化来躲避干扰,相比定频系统生存性能更强,然而面对跟踪跳速高和信道监视宽的特定干扰,跳频通信系统变得犹如定频一样脆弱[2]。因此,一些学者对常规跳频原理做出改进,文献[3-4]提出一种“信道即消息”的传输方式,文献[5]给出了双信道联合跳频的数学模型,即对偶序列跳频(Dual Sequence Frequency Hopping,DSFH)。它具备抗噪声、抗截获和抗摧毁等特点,在一定条件下,较常规、差分跳频具有较好的综合抗干扰能力。

为了达到对偶序列跳频通信链路设计、波形观察及误码率分析的效果,本文应用Simulink平台在原始对偶序列跳频通信仿真链路[6]的基础上,改进设计了双门限结构链路模型。通过时域信号波形接收及误码率分析,验证双门限结构链路具有较好通信效果。

1 对偶序列跳频通信的组成及工作原理

DSFH是以常规跳频通信系统为基础,通过其跳频图案的随机变化来反映信道频率跳变的规律,由两个跳频图案形成一个频率集且以彼此之间的差异来直接表达消息。两个各自独立的跳频图案分别表示数据频率与对偶频率,即形成数据信道与对偶信道,且由于对偶信道在工作中保持静默,不易截获,实现了在截获数据信道后难以推测隐藏信道[7]的频率。因此,称为对偶序列跳频通信。

在对偶序列跳频通信系统中,整个跳频频带WB范围内包含N个正交的跳频频点。发送方和接收方之间存在2个信道,即信道0和信道1,分别表示伯努利信源产生的数据消息0和1。在一次频率的跳变时隙下两个信道各自占据一个频点,此频点由信道对应的跳频序列决定,即跳频序列FS0决定发送码元0的子信道0所占据的频点,而跳频序列FS1则决定发送码元1的子信道1所占据的频点。

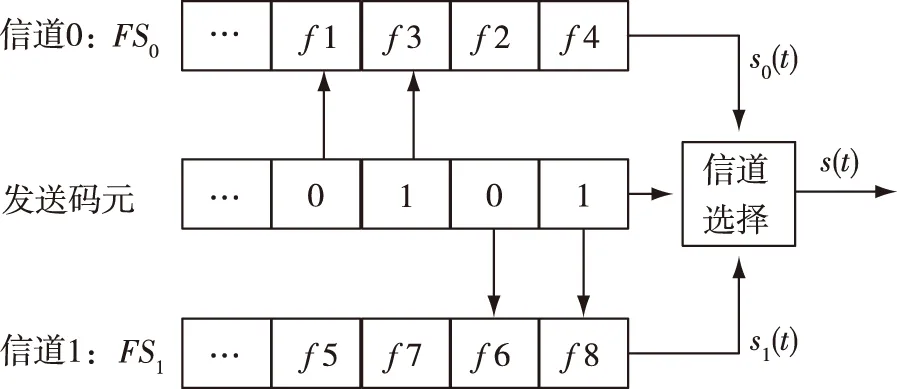

如图1所示,DSFH通过发送码元0、1选择子信道0、1,并确定一次频率跳变对应哪个跳频序列来控制跳频载波。在t时刻,如果发送码元0,则使用信道0发送,即在FS0的当前频率f(0,t)上发送单频信号s0(t);反之如果发送码元1,则由信道1发送,即在FS1的当前频率f(1,t)上发送单频信号s1(t)。在经过信道选择后,最终发射信号s(t)为s0(t)和s1(t)。假设跳频序列FS0的频率为(…,f1,f3,f2,f4,…),跳频序列FS1的频率为(…,f5,f7,f6,f8,…),当发送码元数据为(…,0,1,0,1,…)时,频率合成器依次合成频率为(…,f1,f3,f6,f8,…)的信号。

图1 对偶序列跳频发射结构示意图

(1)

s(t)要经过带通滤波器并上变频后才能发射到空中,由于空中信道存在噪声、衰落和干扰,所以接收结构中收到的信号等效表达式为

r(t)=αsejθs(t)+n(t)+nJ(t)

(2)

其中,αs和θ分别表示等效低通信道中的信号衰落和传输过程中的相位差值,n(t)表示单边功率谱密度为Ν0的加性高斯白噪声,nJ(t)表示经过信道接收到的干扰信号。

如图2所示,接收机在频率间隔跳变的两个窄带接收通道上并行接收,与常规跳频同步模块原理相同,DSFH在接收端产生与发端跳频序列FS0和FS1保持同步的本地跳频序列。r(t)分别与信道0、1的当前频率进行混频,并通过低通滤波器后采用非相干平方律检测。在一次频率跳变期间,信道i的检测判决量ri可表示为

图2 对偶序列跳频接收结构示意图

(3)

由检测判决量ri可得到Y=r0-r1,采用最简单的硬判决方法,即当Y≥0时,判定发送码元信息为0。反之,判定为1。

本文研究了一种最常见的AWGN信道模型,信道中不存在有无敌意干扰。因此,对于AWGN信道,则有αS=1,nJ(t)=0。则式(2)可表达为

r(t)=ejθs(t)+n(t)

(4)

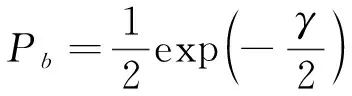

由于未考虑信道干扰,则DSFH可等效为常规FH/BFSK[8]。于是常规跳频非相干检测接收机的两路信号形式和检测判决方式完全可用于DSFH且误码率一致,即得误码率表达式为

(5)

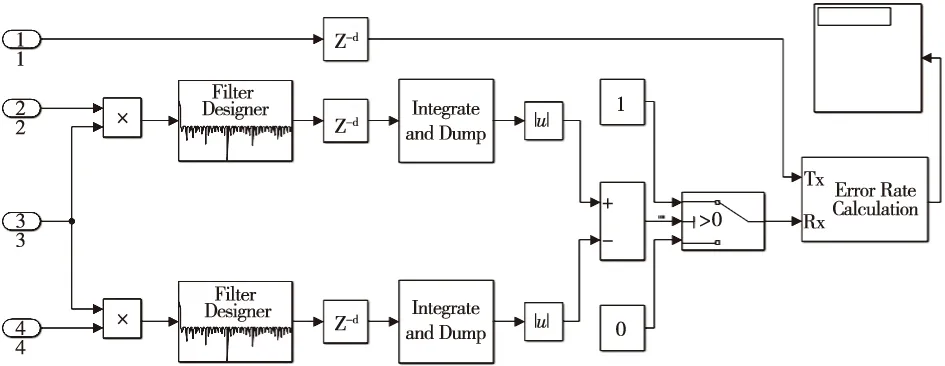

2 仿真链路模型

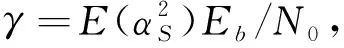

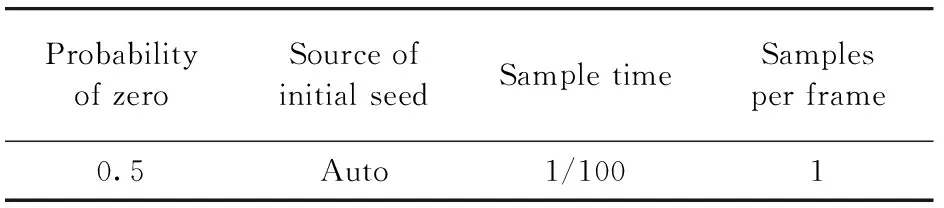

本文考虑在AWGN信道下对偶序列跳频通信系统无干扰时的Simulink仿真模型[9]。如图3所示,该DSFH系统按功能可分为三个部分:信号产生部分、信道部分、信号接收部分。高斯白噪声信道参数如表1所示。

图3 对偶序列跳频通信系统仿真结构模型框图

表1 高斯白噪声信道主要参数

2.1 发送端主要模块设计

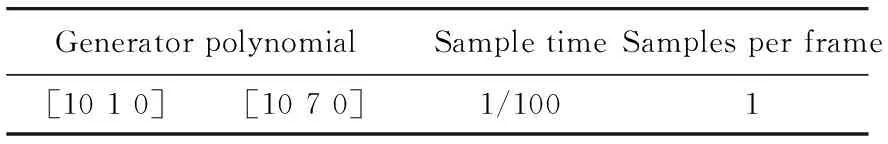

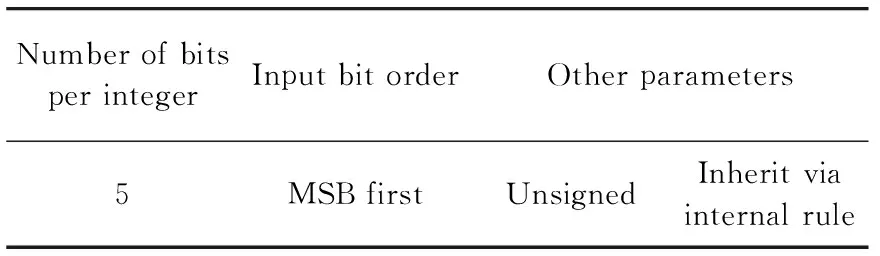

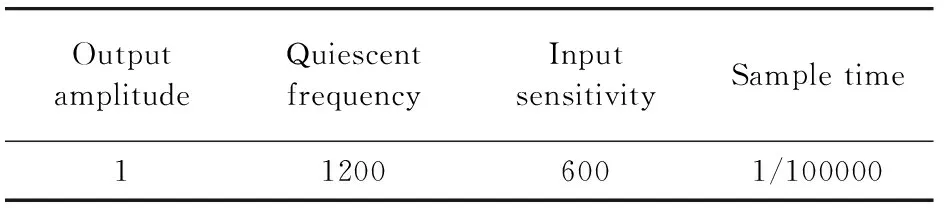

如图4所示,在发射端,伯努利信源以1/100 s的时间间隔产生发送码元即用户消息0、1,且数据信息出现的先验概率相等。在上下两条链路,PN序列以1/100 s的采样周期形成随机跳变的二进制数并由比特到符号转换模块生成整数控制字,经过离散时间压控振荡器(VCO)后得到跳频所需的载频信号,即形成由信息直接选择数据信道和对偶信道的发送端。发射端相关模块的参数设计如表2至表5所示。

图4 DSFH发射端子系统内部结构模型示意图

表2 二进制伯努利信源主要参数

表3 PN序列产生器主要参数

表4 比特到符号转换模块主要参数

表5 频率合成器VCO 主要参数

其中,如图5所示的模块,其设计目的在于避免两个伪随机跳频序列出现相同的控制字整数,导致无法判断区分数据信道和对偶信道。将由PN序列经过Bit to integer模块转换成0~25-1范围内的两路控制字输入if判断模块,若相同则将In1输入端口的PN序列加1,不同则保持原始序列输出。

图5 序列判别模块内部结构框图

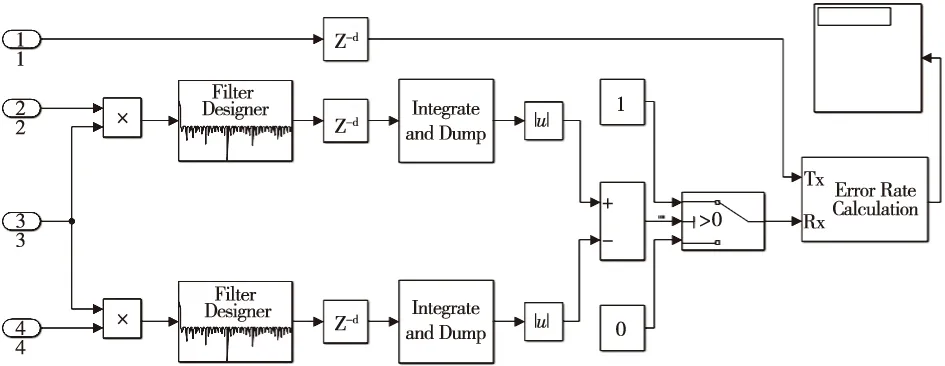

2.2 接收端主要模块设计

如图6所示,在接收端,收到的是发送信号与加性高斯白噪声叠加信号。仿真模型简化了接收端产生本地跳频同步的过程[10],将带有噪声干扰的接收信号作解跳处理,然后经过数字低通滤波器后并对有用信号分量作积分,最后比较两路能量作抽样判决恢复原始信号。

图6 DSFH接收端子系统内部结构模型示意图

接收端相关模块的参数设计如表6所示。其中,延时模块的计算数值依据当前滤波器模块的阶数进行卷积求取;积分清除模块的积分点数依据发送码元的采样周期与合成频率的采样频率确定,本文设置积分点数为1000;判决模块采用门限设置零的硬判决依据二进制双极性基带系统的最佳门限电平理论[11];最后,将接收信号与一定延时的原始信号送入误码率模块由Display模块分析波形数据。

表6 数字滤波器设计主要参数

2.3 改进仿真链路模型

如图7所示为改进后对偶序列跳频链路门限设计仿真示意图。

图7 对偶序列跳频结构门限设计仿真示意图

为实现对偶序列跳频通信中信号有无的发射状态,贴合实际中语音通断情况,本文研究了在信号源发射端模型中加入基于通断键控原理[11]的模块。

3 仿真结果

本文使用Simulink仿真,其中两路序列采用基于m序列的一般模型,并用线性反馈移位寄存器式结构生成周期为210的跳频序列,频点数目为32个,跳频速率为100 hop/s。

1) 在AWGN信道环境下,设置信道参数SNR为0 dB 时,仿真得到链路模型的时域信号波形如图8所示。观察发送端的信号源控制达到了有无信号发射的目的,通过对比发送信号波形与接收信号恢复波形,验证了链路模型的效果,也通过对比双门限结构与单门限结构对信号的恢复情况,体现了双门限结构的判决效果较好。

图8 改进链路模型仿真中的时域波形图

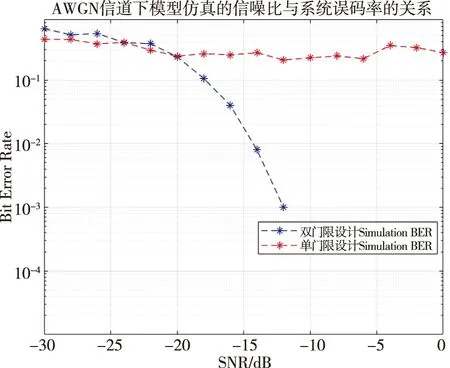

2) 设置信噪比参数SNR从-30 dB~0 dB范围变化,在高斯白噪声信道下系统误码率随信噪比变化关系如图9所示,由图可以看出在信噪比小于-12 dB时,双门限链路结构判决的误码率大小随信噪比的增大而减小,在SNR小于-20 dB情况下,两者通信效果及可靠性均较差。

图9 链路模型的信噪比与误码率关系图

4 结束语

本文设计了基于对偶序列跳频通信系统的一种双门限接收判决的链路模型。该链路结构在AWGN信道下就对偶序列跳频通信双门限设计的链路进行了仿真,达到预期仿真效果;通过仿真实验结果对比分析:1)双门限结构对接收信号的判决波形恢复比单门限结构接收效果较好。2)当信噪比在-20 dB~0 dB范围变化时,双门限结构判决产生的误码率大小较单门限结构降低了2~3个数量级;当信噪比大于-12 dB时,对偶序列跳频双门限链路的通信可靠性较好。但是本文门限设计结构背景单一,仅在有无信号的高斯白噪声背景下展开,简化仿真中跳频同步过程且仿真实验验证对系统的性能和工程应用价值有待提高,对进一步深入研究对偶序列跳频系统提供了参考。