一种宽带扩频信号数字调制器的设计与实现

2021-04-09王丽韫

王丽韫

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

0 引言

无人机下行数据传输系统通常采用QPSK等调制方式,信号的隐蔽性和抗截获能力不足,易受各种干扰,为了提高信号的抗干扰性和抗截获能力,可以采用扩频通信[1]。而对于下行数兆的数据速率,直接序列扩频占用带宽太大,为了解决既能达到一定的扩频增益而又不占用过大带宽,采用多进制正交扩频技术。数兆速率的数据扩频后,扩频码速率达到数百兆,传递前需对信号进行成形滤波,以改善其频谱特性,使得在消除码间干扰与达到最佳检测接收的前提下,提高信道的频带利用率[2]。

对于数百兆速率扩频码的成形滤波,采样率是码速率的4倍,受硬件工作速度的限制,直接进行如此高速率的信号处理是不可能的,需采用并行处理算法降低对器件工作速度的要求,本文采用多相结构实现高速数据成形滤波。

对于高速基带数据调制,通常的实现方法是用IQ调制器进行模拟调制。正交调制会带来信号的非严格正交、幅相不一致和载波泄露等问题[3]。直接数字频率合成(Direct Digital Synthesis,DDS)方法因其电路简单信号严格正交、频率分辨率高和幅相一致性好等优点而逐渐成为宽带信号调制技术的主流发展方向。但DDS输出信号频率和带宽受其工作时钟频率的限制,导致其无法直接合成高载频、大带宽信号。本文设计了一种基于并行DDS技术的宽带扩频信号数字调制器,使FPGA能在较低工作频率下实现较高的采样率,从而实现宽带数据高中频调制的直接输出。

1 宽带扩频信号调制器总体结构

宽带多进制正交扩频系统的调制端将要传输的信息经串并转换成m路的并行数据,然后利用m个信息比特从M路正交码选出一路作为扩频信号传输(M=2m)[4]。宽带多进制正交扩频系统的调制端结构框图如图1所示。

图1 宽带多进制正交扩频系统的调制端结构Fig.1 Modulator framework of broadband M-ary orthogonal code spread spectrum system

设信号幅度为1,则发送的信号s(t)为:

式中,ci(t)为正交扩频码集中的某个扩频码。

2 成形滤波器设计

2.1 成形滤波器原理

实际系统中,广义信道传递函数H(f)由发送滤波器HT(f)、信道HC(f)、接收滤波器HR(f)三部分共同构成,即[5]:

H(f)=HT(f)·HC(f)·HR(f)。

(1)

根据奈奎斯特第一准则,当H(f)幅频特性满足滚降系数为α的升余弦滤波器特征时,即发送端成形滤波器具有平方根升余弦滚降特性,与接收端的匹配滤波器级联后具有升余弦滚降特性时,可以实现无码间干扰传输。其平方根升余弦滚降的频率响应特性如下[6-8]:

(2)

式中,T为输入码元的周期;α为滚降系数,0≤α≤1。平方根升余弦冲击响应为:

(3)

2.2 多相滤波

本文研究的扩频基带速率约为180 Mb/s,然后对180 Mb/s的基带信号进行成形滤波,滤波器的采样速率为4×180=720 MHz,就目前的数字集成电路技术,FPGA中直接进行720 MHz这么高速率的滤波运算是不可能的。由信号处理知识可知[9],在4倍采样条件下,FIR成形滤波器相当于一个4倍的内插滤波器。其实现结构可以采用多相结构,一方面可以减少运算负担,提高运算速度,另一方面也可减小滤波运算的累积误差,提高计算精度,降低滤波器的运算速率。

在FIR滤波器中,转移函数:

(4)

式中,N为滤波器长度。将冲激响应h(n)分成D个组,并设N为D的整数倍,即N/D=Q,Q为整数,则[10-12]:

H(z)=h(0)z0+h(D)z-D+…+h[(Q-1)D]z-(Q-1)D+

h(1)z-1+h(D+1)z-(D+1)+…+h[(Q-1)D+1]z-(Q-1)D-1+

h(2)z-2+h(D+2)z-(D+2)+…+h[(Q-1)D+2]z-(Q-1)D-2+

⋮ ⋮

h(D-1)z-(D-1)+h(2D-1)z-(2D-1)+…+

h[(Q-1)D+D-1]z-(Q-1)D-(D-1)=

(5)

令:

(6)

(7)

则Ek(zD)称为H(z)的多相分量。

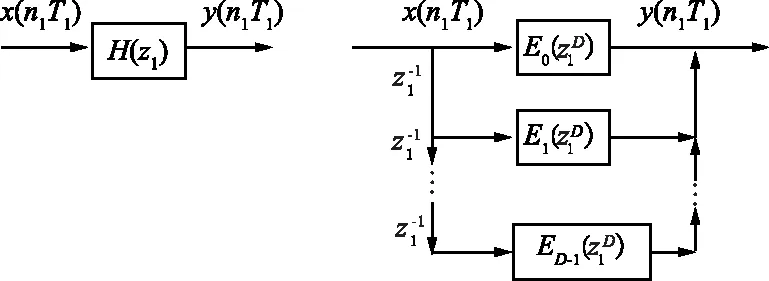

FIR滤波器的多相结构如图2所示。

图2 FIR滤波器的多相结构Fig.2 Polyphase-structure of FIR filter

通过Matlab仿真软件设计发射端波形成形FIR滤波器的参数为:α=0.5,滤波器取每符号4个采样点,FIR滤波器有限长度N为33,即截取峰值点前后各4个符号。可得出系数h(0),h(1),h(2),…h(31),h(32)的数值[13],如表1所示。

表1 平方根升余弦滤波器的h(n)

在数字化波形成形时,为确保h(t)采样后的h(n)保持第一类线性相位,可舍去h(t)|t=0样点,同时对N-1(偶数)点h(n)右移N-1/2[2]。

采样率720 MHz的成形滤波器在FPGA中分成4路并行,处理速率180 MHz,采用多相成形滤波器,将设计出的系数分成4组,分别为[6,14]:

H0:h(1),h(5),h(9),h(13),h(17),h(21),h(25),h(29);

H1:h(2),h(6),h(10),h(14),h(18),h(22),h(26),h(30);

H2:h(3),h(7),h(11),h(15),h(19),h(23),h(27),h(31);

H3:h(4),h(8),h(12),h(16),h(20),h(24),h(28),h(32)。

由一个33阶的滤波器变成4个并行的8阶子滤波器构成。4路并行输出为:

(8)

发端基带数据进行多相成形后的时域波形如图3所示。这样就将滤波器的工作频率从720 MHz降到了180 MHz,同时将一个滤波器变为4个滤波器并行运行,由于FPGA集成度高、资源丰富,上述多相分布式的滤波器结构在FPGA中较易实现。

图3 发端数据多相成形后时域波形Fig.3 Waveform in time domain of data processed by polyphase shaping filter

3 高速数据调制并行处理算法与实现

成形滤波后的基带数据要进行数字中频调制[15]。扩频基带速率为180 Mb/s,中频载波采用720 MHz。对于宽带高中频信号调制,通常的实现方法是将FPGA产生的成形数据通过DA变成模拟基带信号,用一片IQ调制器进行模拟调制。基于模拟调制的缺点,本文采用数字DDS技术及高速DA实现高中频数字调制。DDS的原理是根据参考时钟和输出频率计算出一个频率控制字,在每一个参考时钟沿将该频率控制字进行累加以生成实时的相位信息,用相位字选择正弦幅度ROM表中对应的幅度值,生成正弦载波。

对于低中频DDS,可以采用一个高倍输出频率的采样时钟做参考,每个时钟计算出一个相位字,串行生成中频载波。对于720 MHz中频,采样时钟选2.88 GHz,在FPGA内实现数字DDS,受处理时钟的限制无法直接产生DDS,采用多路并行DDS技术[3],分成16路并行,每路采样率180 MHz。因此需要将16路的频率控制字累加结果同时计算出来,如式(9)所示[16]:

(9)

各路分别用各自的相位字同时选择ROM表相应位置的正弦波幅度值,得到16路并行的DDS输出,将并行的基带成形数据与生成的并行正弦载波采样值相乘进行调制。基带成形数据的采样率为720 MHz,在FPGA中分成4路并行,而DDS的采样率为2.88 GHz,16路并行,调制时基带成形数据要进行4倍插值,提高采样率到2.88 GHz,才能与并行DDS的相应采样点相乘进行调制。16路并行调制输出为:

(10)

并行调制数据要进行并串转换,经过高速DA可以实现宽带数据中频调制的直接输出。高速DA芯片内部集成了一个4∶1的并串转换器,采样率2.88 GHz,并行支路采样率720 MHz,而FPGA中的调制数据分16路并行,每路180 MHz处理速率。需要利用FPGA软件的LVDS模块进行并串转换,把16路180 MHz并行数据转换成4路720 MHz并行数据,分别连接高速DA的4路输入口,完成数模转换,输出中频模拟调制信号。实现宽带数据高中频调制的直接输出,省掉了调制器,使硬件简单、节约成本。

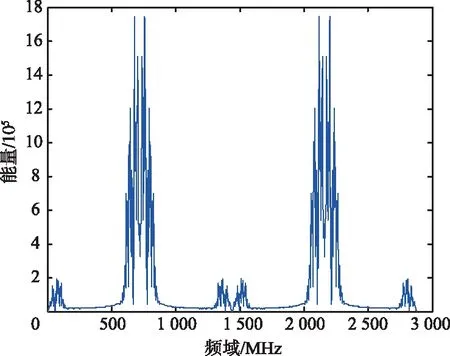

成形滤波后数据调制到中频的波形如图4所示。中频调制信号频谱如图5所示。

图4 数据调制到中频波形Fig.4 Data modulated to mid-frequency waveform

图5 中频调制信号频谱Fig.5 Frequency spectrum of mid-frequency modulated signal

4 结束语

本文研究了一种宽带扩频信号数字调制器的设计与实现技术,对于宽带扩频数据,传递前需对信号进行成形滤波,以改善其频谱特性,使得在消除码间干扰与达到最佳检测接收的前提下,提高信道的频带利用率。阐述了成形滤波的基本原理,高速数据FIR成形滤波器的多相结构,运用Matlab和Quartus II建模与仿真软件设计和实现了宽带信号的成形滤波器,并且提出了采用并行DDS技术和高速DA实现宽带数据高中频数字调制。最后通过硬件平台验证了设计的有效性和可行性。实验结果表明,采用多相结构实现高速数据的成形滤波,打破了硬件限制,实现了数据的高速处理。采用数字中频直接合成方法结合多路并行DDS技术,能产生具有良好频谱特性的宽带调制信号,并且硬件简单。该技术中涉及到的并行处理思想可扩展到其他波形信号发生器,故本设计具有一定的可扩展性。