FPGA在双通道信号采集与传输系统设计中的应用

2021-02-28中国兵器装备集团自动化研究所有限公司李坤贺

中国兵器装备集团自动化研究所有限公司 李坤贺 陈 刚 卢 峥

文章针对高精度、高速信号采集需求,以FPGA为处理核心设计了一款双通道高速信号采集与传输系统,该系统具备双通道高速AD采样,经过FPGA处理后,将数据打包通过1路千兆以太网络上传给远程控制终端。该系统具有采样精度高、适用范围广、功耗低等特点。

在宽带通信、基站及图像处理领域经常遇到高精度、高速信号采集需求,同时还需要将采集数据进行远距离上传,针对该应用需求,本文设计了一款双通道信号采集与传输系统,不仅能够对2路模拟信号进行高速采集,还能通过千兆以太网接口将采集数据实时传输给远程控制终端。该系统具有采样精度高、采样速度快、适用范围广、传输距离远等特点。

1 系统方案设计

本文设计的双通道信号采集与传输系统主要包括硬件设备和系统软件。

硬件设备主要包括:模拟信号调理电路、A/D采集电路、FPGA处理模块、网络传输模块;系统软件主要包括:FPGA逻辑程序和远程控制终端绘图显示软件。

系统结构框图如图1所示。

图1 系统结构框图

2 系统硬件设计

本文设计的信号采集与传输系统主要由模拟信号调理电路、A/D采集电路、FPGA处理模块、网络传输模块等几部分组成。

2.1 模拟信号调理电路

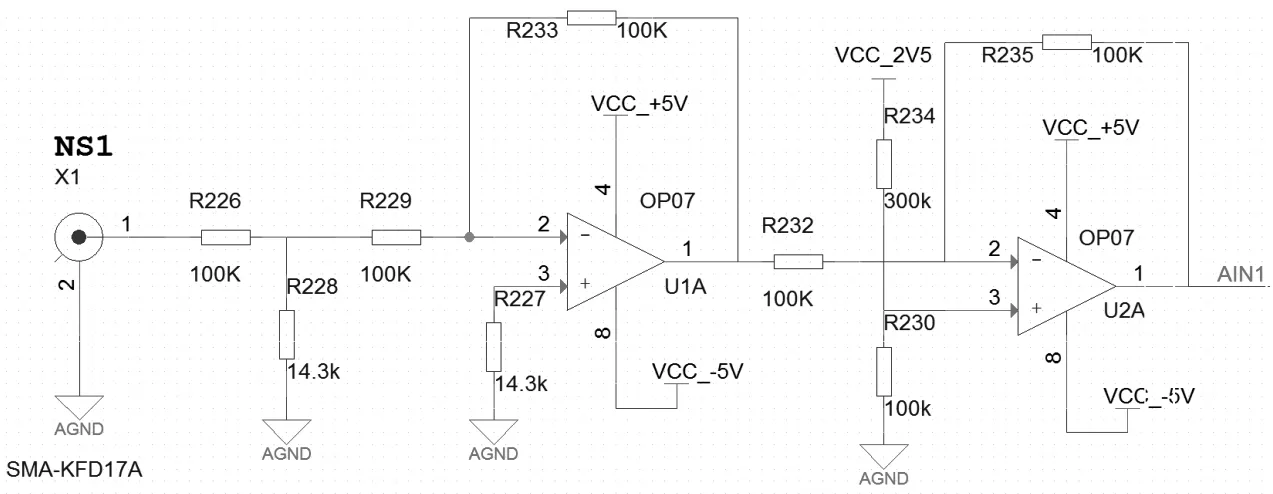

为了满足采集信号的宽范围输入,本文设计了模拟信号调理电路(如图2所示),通过两级精密运算放大器组成模拟信号调理电路,能够对不大于±10V的模拟信号进行调理,使其满足A/D采样芯片的输入要求。

图2 模拟信号调理电路

2.2 A/D采集电路

本文设计中选用2片AD9224作为A/D转换芯片,该芯片具有最高40MSPS采样能力,采样精度12位,可适应2V/4V 输入电压范围,模拟输入共模电压为2.5V,只需提供单端+5V模拟电源和+3V/+5V 数字电源。

该芯片数字端接口为12位并行数据接口,本文设计中将该并行接口连接至FPGA,FPGA接收到2路AD9224发送来的采集数据后,进行组帧、打包发送。为了防止数字地层产生的干扰,保证电路较高的采样精度,在设计中将模拟地(AGND)和数字地(GND)分离开,并且在布线时也避免数字线布于模拟线旁边或ADC下方。A/D采样电路如图3所示。

图3 A/D采样电路

2.3 FPGA处理模块

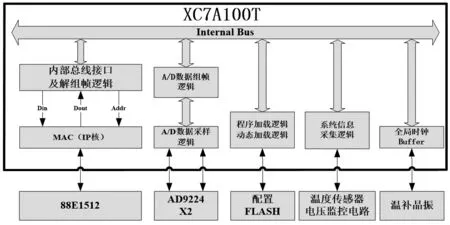

本文设计中选用Xilinx公司的XC7A100T作为数据采集及处理核心,该FPGA具有101K逻辑单元、4Mb Block RAM、285只GPIO,逻辑资源和GPIO接口丰富。

FPGA处理模块程序加载电路:本文设计中选择256Mb QSPI FLASH作为FPGA的程序存储器,通过对M[0:2]配置方式引脚的设置,选择QSPI主动配置模式,配置时钟最高可为50MHz,程序加载时间约为500ms,保证了FPGA程序的快速加载和启动。

FPGA处理模块电源系统:为了保证FPGA能正常工作,选用了Linear的LTM4644作为其电源系统解决方案,该电源模块具有4路4A DC/DC电源输出能力,输入电压范围为:4~14V,输出电压为0.6~5.5V,输出电源纹波电压为:20mVpp,满足FPGA核电源、接口电源、辅助电源的要求;同时,选用了两种LDO芯片:CW78D25和CW78D18产生模拟电路所需的更高质量要求的2.5V和1.8V电源。FPGA有严格的上电时序,所选电源芯片具有EN、PG引脚,可以通过级联的方式有效控制电源的上电时序,满足FPGA对上电时序的要求。

FPGA处理模块时钟网络:为了保证高精度、高速采样及FPGA内部逻辑的稳定性,选用了高精度、高稳定性的40MHz温补晶振作为FPGA全局时钟输入,40MHz全局时钟输入FPGA内部后,经过DCM时钟、复位逻辑模块产生内部逻辑使用的100MHz、66.667MHz等时钟网络和复位信号;40MHz温补晶振的频率温度稳定度为±1ppm,从时钟源头上保证了FPGA内部逻辑采样的精准度。

FPGA处理模块内存系统:为了保证高精度、高速采样数据缓存需要,FPGA处理模块还设计了1333MHz、32位宽、512MB容量的DDR3内存系统,内存颗粒选用MICRON公司的MT41J128M16JT-125IT。内存颗粒挂载在XC7A100T的HP Bank,能充分发挥DDR3的高速缓存特性。

FPGA处理模块系统信息采集电路:为了保证系统的稳定工作,设计了温度传感器、电源电压检测等系统信息采集电路,能够实现对系统主要电源电压、温度信息的监控,并通过网络接口上报至远程控制终端。

2.4 网络传输模块

为了能将采集的数据有效、快速的传输给远程控制终端,本文设计中实现了1路千兆以太网络接口,由FPGA内部逻辑调用IP Core实现MAC层协议,选用Marvell公司的88E1512作为外接PHY芯片。

FPGA MAC与88E1512之间通过RGMII接口互联,FPGA通过MDIO、MDC接口实现对88E1512的内部寄存器配置;选用1片25MHz晶体谐振器作为88E1512的外部时钟源;88E1512所需要的1.0V、1.8V、3.3V电源要求与FPGA各电源系统相同,本文设计中将88E1512所需要各电源系统与FPGA各电源系统共用,既满足了系统应用,也减少了单独电源设计,降低功耗和成本。

3 系统软件实现

本文设计的信号采集与传输系统软件部分主要包括FPGA逻辑程序和远程控制终端采集绘图显示软件两部分组成。

3.1 FPGA逻辑程序

FPGA主要实现A/D采集数据的预处理、组帧、发送功能,主要由时钟及复位逻辑、A/D接口逻辑、网络接口逻辑、程序加载及动态加载逻辑、系统信息采集及上报逻辑。

时钟及复位逻辑实现对输入时钟和复位信号的处理,并通过DCM模块产生其他内部逻辑模块所需要的不同时钟和复位信号;A/D接口逻辑实现对2片AD9224采集芯片采集数据的预处理功能,组帧后传给上层组帧逻辑,和系统信息一起上传给远程控制终端;系统信息采集逻辑实现对温度传感器、电压监控电路信号的采集处理功能,将温度、电压等信息随A/D采样数据帧一起上传给远程控制终端;网络接口控制逻辑实现对PHY芯片的配置、MAC IP核的例化和数据的解组帧功能。FPGA逻辑结构框图如图4所示。

图4 FPGA逻辑结构框图

3.2 远程控制终端采集绘图显示软件

为了更加形象的观察采集的结果,本文设计了远程控制终端采集绘图软件,远程控制终端通过千兆以太网接口接收数据后,首先对数据进行解帧处理,然后将数据分别显示在采集绘图显示软件上。采集绘图软件包括AD采样波形绘图界面、系统信息显示界面。采集绘图显示软件的处理流程如图5所示。

图5 远程控制终端绘图显示软件流程

4 功能测试及实现情况

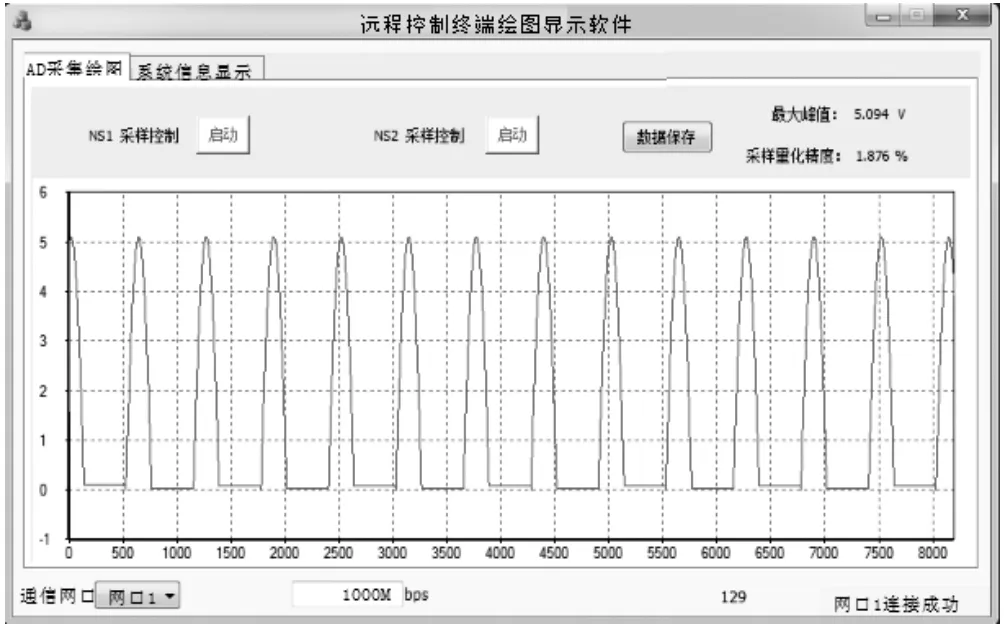

在对本文设计的信号采集与传输系统进行测试时,选择+5V半波正弦信号作为激励信号源,通过远程控制终端采集绘图显示软件将采集到的数据进行绘图显示(如图6所示),采样数据精度误差不大于2%,系统典型总功耗为3.5W。

图6 信号采集与传输系统采集结果绘图显示

结束语:本文详细介绍了基于FPGA的双通道信号采集与传输系统设计,首先介绍了系统功能结构,然后分模块介绍了各部分硬件电路设计,其次又介绍了FPGA逻辑和远程控制终端采集绘图显示软件的设计流程,最后对整个系统进行了信号采集测试,测试结果证明该系统采集指标满足设计及应用需求。

综上所述,本文设计的基于FPGA的双通道信号采集与传输系统结构简单、采样精度高、采样速度快、传输距离远、性能稳定可靠,能很好地满足宽带通信、基站及图像处理领域的应用需求。