浅谈PCB串扰及抑制措施

2021-02-23孙宝来王海刚杜尚勇

孙宝来 王海刚 杜尚勇

摘 要:目的:分析引起串扰的各种因素,提出相应的抑制措施,实现印制电路板(PCB)串扰的最小化。方法:通过探讨PCB中串扰的产生机理及影响,并结合实例分析。结果:得到了抑制PCB串扰的有效措施,如选择合适元器件、合理布局布线、使用屏蔽层、实施阻抗匹配以及进行串扰分析和仿真。结论:通过有效的抑制措施,PCB串扰可以最小化,本文可以为工程师设计PCB时提供参考。

关键词:串扰;抑制措施;印制电路板;PCB;机理最小化

1引言

在PCB板级和系统级的分析和设计方法中,信号完整性(Signal Integrity,简称SI)分析与设计是尤为重要的,且在硬件电路设计中的作用愈来愈明显。 信号完整性通常是指信号线上的信号质量,反射、振铃、地弹和串扰,均属于信号完整性问题范畴。其中,信号串扰最为复杂,涉及许多因素,难以计算和控制。本文重点分析信号串扰问题以及如何抑制。

2串扰的产生机理

串扰是指当信号在传输线上传输时,由于电磁耦合,它会对相邻的传输线产生不良影响,一定的耦合电压和耦合电流注入到了受干扰信号中。除了时钟信号和周期信号,其它的关键信号,如数据、地址、控制和I / O走线等,都会受到这种非期望的电磁耦合的影响,这就是串扰。尤其需要关注的是呈现周期性的一些信号,如时钟等。串扰超过某个阈值可能会引起电路故障并导致系统无法正常工作。

串扰发生的要素有两个,即噪声源线和噪声源接收线。其中,噪声源线是指产生耦合信号的传输线,而噪声源接收线是指信号被耦合到的传输线。如图1所示,传输线A的快速电平变化,会导致传输线B受到干扰,在传输线B上会产生干扰电压或干扰电流。

串扰按照耦合方式分为容性串扰和感性串扰两种。

2.1 容性串扰

容性串扰指的是两条信号线之间通过耦合电容产生的干扰,如图2所示。

因为走线之间存在耦合电容Cm,当噪声源线的电压变化时,噪声就会从噪声源线耦合到噪声接收线上。引发的耦合电流就会在传输线的两个方向传输,并在源端和负载端的阻抗处产生电压,直到它被源和负载消耗掉。而在源端和负载端存在阻抗不匹配的情况时,就会发生反射,最终导致负载端出现较大的电压尖峰。噪声电压的大小与噪声源线的电压变换率成正比,通常可以由公式(1)计算:

由于两条传输线之间的耦合电容与传输线之间的距离有关,两信号之间的距离越近,耦合电容越大,容性串扰越严重。所以,为了减少容性串扰,应尽可能加大传输线之间的距离。也可以在两条传输线之间放置地线,作为隔离措施,消除耦合电容,从而消除容性串扰。

2.2 感性串扰

感性串扰指的是两条信号线有电流流过时,通过它们之间的变压器效应产生互感耦合,最终在噪声接收线处产生干扰,如图3所示。

当噪声源线和噪声接收线之间的距离足够近,以致噪声接收线被噪声源线产生的磁场所包围时,会在噪声接收线上产生感应电流,这个感应电流由磁场产生。在电路模型中,该电流可以通过互感参数来表征。互感系数Lm表示驱动传输线通过磁场将电流感应到另一传输线的程度。受害线上产生的噪声,则与驱动线的电流变化率有关,噪声电压的大小与电流变换率成正比,通常可以由公式(2)计算:

同样的,由于感性串扰的大小与终端负载阻抗有关,负载阻抗越大,产生的干扰电压越大,因此为了减少感性串扰,可以减小负载阻抗,或者通过终端阻抗匹配来抑制反射。

3串扰的影响

串扰一般是在噪声接收线上产生耦合电压和耦合电流,从而引起接收端处的电平变化。接收端的噪声容限决定这种电平变化是否会使接收端产生误触发。这里的噪声容限是指门电路的抗干扰能力,包括低电平噪声容限VNL和高电平噪声容限VNH,如图4所示。

其中高、低电平噪声容限可由公式(3)(4)计算:

式中:

VOH(min)——输出的高电平的最小电压值;

VIH(min)——输入的高电平的最小电压值;

VIL(max)——输入的低电平的最大电压值;

VOL(max)——输出的低電平的最大电压值。

对于驱动器端,输出的高电平不低于VOH(min),输出的低电平不高于VOL(max)。而对于接收端输入来说,只要高于VIH(min)即可以保证接收到逻辑1,只要低于VIL(max)即可保证接受到逻辑0。而如果输入电压值位于VIH(min)和VIL(max)之间的区域时,可能被接收电路判为1,也可能判为0。因此对于接收电路来说,输入的电压值不能处于这个不定态区域中。

高、低电平噪声容限越大,表示电路的抗干扰能力越强。当串扰引起接收端的电平变化超过其噪声容限时,就会引起接收端的误动作,可能直接导致整个系统无法正常工作。

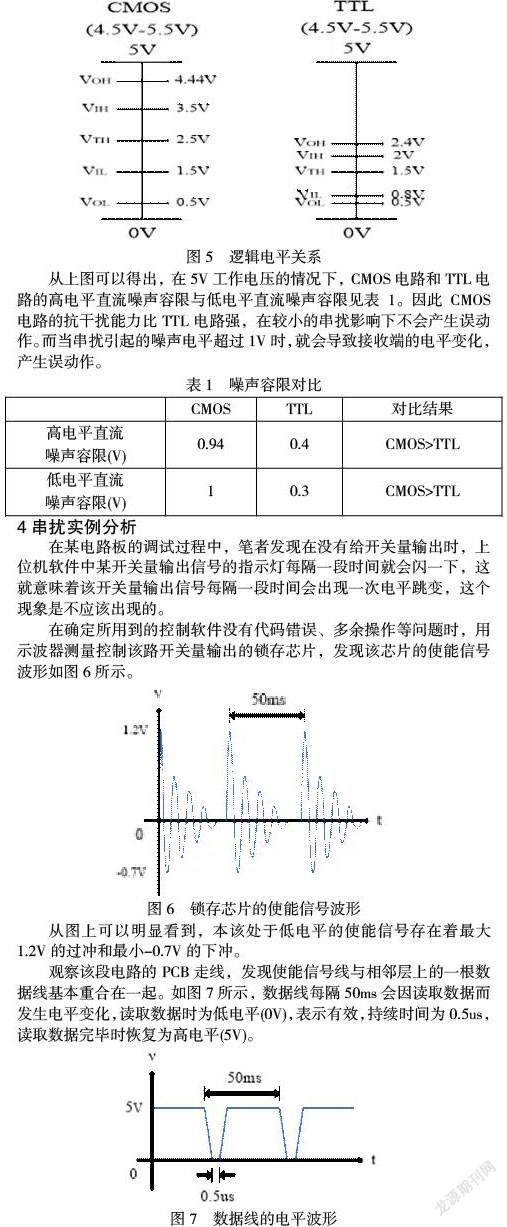

各种类型的集成电路中,以最常见的CMOS和TTL为例,它们的逻辑电平关系如图5所示。

从上图可以得出,在5V工作电压的情况下,CMOS电路和TTL电路的高电平直流噪声容限与低电平直流噪声容限见表1。因此CMOS电路的抗干扰能力比TTL电路强,在较小的串扰影响下不会产生误动作。而当串扰引起的噪声电平超过1V时,就会导致接收端的电平变化,产生误动作。

4串扰实例分析

在某电路板的调试过程中,笔者发现在没有给开关量输出时,上位机软件中某开关量输出信号的指示灯每隔一段时间就会闪一下,这就意味着该开关量输出信号每隔一段时间会出现一次电平跳变,这个现象是不应该出现的。

在确定所用到的控制软件没有代码错误、多余操作等问题时,用示波器测量控制该路开关量输出的锁存芯片,发现该芯片的使能信号波形如图6所示。

从图上可以明显看到,本该处于低电平的使能信号存在着最大1.2V的过冲和最小-0.7V的下冲。

观察该段电路的PCB走线,发现使能信号线与相邻层上的一根数据线基本重合在一起。如图7所示,数据线每隔50ms会因读取数据而发生电平变化,读取数据时为低电平(0V),表示有效,持续时间为0.5us,读取数据完毕时恢复为高电平(5V)。

分析后,可以确定该数据线为噪声源。在读取数据的时候,数据线上快速的沿的变化,通过容性耦合在使能信号线上产生串扰,致使使能信号线上的电平每隔50ms出现一次振铃现象。当使能信号线上的干扰电压过大(大于锁存芯片的噪声容限,约为0.8V)时,会使得锁存芯片误动作,从而导致开关量输出信号的电平发生跳变,造成指示灯闪烁。

原因查明后,通过更改走线的方式,将使能信号线稍微远离数据线后,故障现象消失。再用示波器观察使能信号线上的波形,发现干扰电压依然存在,但幅值降低了许多(最大过冲为0.5V,最小下冲为-0.2V)。若要进一步减小串扰,可以通过继续加大使能信号线和数据线的距离,在使能信号线旁增加地保护走线,或者在它们之间增加地线层等方法来达到目的。

5串扰抑制措施

设计PCB时,减少干扰源网络与被干扰网络之间的耦合,可以达到减小对系统具有负面影响的串扰现象的目的,但在复杂的PCB设计中不可能完全避免串扰。设计人员应考虑选择适当的方法以最小化串扰而不影响系统的其它性能。结合以上分析,主要从以下几个方面考虑解决串扰问题的方法:

(1)采用降低信号沿的变换速率的方法。由于高速信号易于对低速信号引起串扰,所以在满足PCB设计的前提下,可尝试选择慢速器件以减慢电场和磁场的变化速率,并避免混合使用不同类型的信号。

(2)在布局PCB时应遵循的原则见表2。

(4)使用屏蔽方法。提供用于高速信号的数字接地是解决串扰问题的有效方法。但是,包地会增加布线量,使原来有限的布线区域更加拥挤。另外,为了实现接地线屏蔽以达到期望,接地线上的接地点之间的距离至关重要,通常小于信号变化沿长度的两倍。同时,地线还将增加信号的分布电容,这将增加传输线的阻抗并减慢信号沿。由于表面层仅具有一个参考平面,因此表面层布线的电场耦合要强于中间层,因此对串扰更敏感的信号线应尽可能放置在内层中。

(5)实施传输线阻抗匹配。串扰的幅度跟终端阻抗与传输线阻抗是否匹配息息相关,因此可以通过端接,大大降低串扰的影响。如应用串联终端、并联终端、戴维南终端、AC并联终端和二极管终端等传输线端接方式确保最优的信号完整性和最小化射频能量。其中比较常采用的是串联终端匹配方式,简单且低功耗,但减慢了负载端的信号上升沿时间。

(6)进行串扰分析和仿真。串扰分析的目的是为了在 PCB 实现中迅速地发现、定位和解决串扰问题。在仿真工具中可以设定电气规则和物理规则,对可能的串扰进行仿真分析,并在布线时自动计算信号完整性要素,例如过冲和串扰。确定串扰是否會出现超出噪声容限,可根据计算的结果自动修正布线再继续分析修正,最终形成一个最小化串扰的解决方案。

6结论

本文通过探讨PCB中串扰的产生机理及影响,并结合实例分析了引起串扰的各种因素,提出了选择合适元器件、合理布局布线、使用屏蔽层、实施阻抗匹配以及进行串扰分析和仿真等措施,有效抑制PCB的串扰。随着PCB日益高速和高密度,受限于设计面积和制造成本,串扰最小化变得尤为重要。本文可以为工程师设计PCB时提供参考,在成本和性能之间达到最好的平衡。

参考文献:

[1]汪思敏,唐广芝.PCB和电磁兼容设计(第2版)[M].机械工业出版社,2008,6.

[2]乔洪.高速PCB串扰分析及其最小化[J].中国集成电路,2007.

[3]周萍.高速PCB板的信号完整性设计[J].电子质量,2009.

[4]邵震洪,赵杭生.高速数字电路的PCB设计.[J].现代军事通信,2005.

作者简介:

孙宝来(1986-),男,工程师,主要从事电子对抗技术方面的研究工作。