MPSoC在多轴伺服电机驱动器上的应用

2021-02-22王邦继王东许睿张文轩刘庆想

王邦继, 王东, 许睿, 张文轩, 刘庆想

(西南交通大学 物理科学与技术学院,成都 610031)

0 引 言

永磁同步电机(permanent magnet synchronous motor,PMSM)省去了转子励磁装置,无需励磁电流,具有结构简单、体积小等优点,尤其在空间有限且需要多轴伺服精确控制的应用场合具有广泛的前景,如工业机器人、数控机床、导弹舵机和相控阵列天线等[1-2]。

目前,多轴伺服控制系统主要包括数字信号处理器(digital signal processor,DSP)的软件方案以及现场可编程逻辑门阵列(field programmable gate array,FPGA)的硬件方案。DSP的软件方案,价格低廉、灵活性强,可以实现多种控制算法,得到广泛的应用。近些年,TI等公司推出了电机专用的DSP控制芯片,计算性能十分强大,还添加了很多电机实际控制需要的外设单元,已成为市场主流伺服控制产品。但软件串行中断的执行方式限制了处理器的性能,不适合运算复杂且实时性要求非常高的应用场景,单个DSP难以满足高精度多轴伺服控制的需求。而采用多个DSP互联的设计方式,就会使得设计难度增加,成本上升,系统集成度降低,同时各轴之间易出现不同步的问题。因此DSP的软件方案难以实现多轴伺服电机的高性能控制[3-6]。

FPGA具有高速、低功耗、并行处理和模块化等特点,允许单一芯片控制多台电机,部分学者对其开展了深入探索[7-10]。国内李铁才等人[11-12]对基于FPGA 的高性能多轴伺服系统进行了研究,实现了四轴电机伺服控制 ASIC 芯片等一系列的成果。国外的Hsin-Hung Chou、B-M L等人[13-14]在单片FPGA上集成了多轴控制算法,设计了多轴伺服电机控制平台。伺服控制系统的位置环、速度环、电流环闭环算法以及相应的信号采集与处理算法由纯硬件逻辑实现,实现单FPGA芯片的全数字化多轴控制。这种技术方案由于位置环、速度环需求灵活,纯硬件的设计方式很难满足通用性的要求,而且很难根据外部参数和实时状态配置参数,存在软件与硬件功能规划不合理的问题。

随着多处理器片上系统(multi-processor system on chip,MPSoC)的发展,Ben Othman等学者[15-18]将其引入电机驱动等实时控制领域,提出了基于FPGA的MPSoC架构,用于实现高实时性、高精度运行的系统。本文提出一种基于MPSoC的多轴伺服驱动方案,该方案采用FPGA作为处理器。在单轴电机控制上,电流环控制IP核实现电流环算法,速度环算法在软核中实现,通过软硬件协作的方式完成单轴电机的精确控制。结合MPSoC构建了多轴伺服控制系统,集成了核间通讯和上电自启动等功能。最后搭建了两路实验系统,并通过实验验证了方案的有效性。

1 永磁同步电机矢量控制

1.1 永磁同步电机数学模型

表贴式PMSM在d-q轴两相旋转坐标系下的电压方程为:

(1)

式中:ud、uq分别为d、q轴电压;id、iq分别为d、q轴电流;Ld、Lq分别为d、q轴电感;Rs为定子电阻;ψf为永磁体磁链;ωe为转子电角速度;p为极对数。

在d-q轴两相旋转坐标系下的转矩方程为

(2)

式中Te为输出转矩。

忽略摩擦的情况下,在d-q轴两相旋转坐标系下的运动方程为

(3)

式中:TL为负载转矩;B为摩擦系数;J为轴的转动惯量;ωr为机械角速度。

1.2 矢量控制

矢量控制又称磁场定向控制,关键在于坐标变换,对PMSM主要采用转子磁链定向控制,其控制方式适合伺服控制等小驱量控制场合。目前PMSM的电流环控制策略主要包括:id=0控制方法、cosφ=1控制方法、转矩电流最大比控制方法以及弱磁控制方法等。对表贴式永磁同步电机而言,为达到伺服系统输出的全部电流均生成转矩分量,提高转矩输出效率的目的,采用id=0的电流环控制策略是较好的选择。在此基础上添加位置环、速度环实现电机的位置伺服控制,其控制框图如图1所示。

图1 位置伺服控制系统结构框图Fig.1 Block diagram of the position servo control system

2 系统整体方案

图2给出了这种基于MPSoC的多轴伺服控制方案的整体结构框图。

为实现单轴电机的高精度控制,结合软硬件协同设计方法,设计了单轴电机控制模块。具有高实时性和算法相对单一等特点的电流矢量控制算法以及信号采集、处理算法由纯硬件逻辑设计的电流环控制IP核实现,具有强灵活性的速度环算法在嵌入式软核中以软件方式实现。单轴电机控制模块内部包含以下模块:电流环控制IP核模块,用于实现对应轴的电流环矢量控制算法以及信号采集和处理算法,将计算的位置、速度信息反馈给从处理器用于闭环控制。从处理器,首先读取片上共享内存上的数据完成与主处理器之间的核间通讯;其次接收同一模块内部的电流环控制IP核反馈的速度信息,执行对应轴的速度环算法,根据计算结果输出电流指令;此外还包括闭环参数配置、多种对外接口等软件功能。片上RAM,用于存储从处理器的程序,提供从处理器程序的运行空间。

图2 多处理器片上系统结构Fig.2 Multi-processor system on chip structure

为实现多轴电机独立、同步驱动,对单轴电机控制模块进行多路拓展,设计了多处理器片上系统结构,添加了多个模块完善片上功能。在主处理器与从处理器间采用MUTEX核与片上共享内存结合的通讯方式实现多处理器间的数据通讯。添加MUTEX核,用于实现多个处理器对片上共享存储资源的互斥访问;添加片上共享RAM,用于实现多个处理器通讯时的数据交互以及存储。

多处理器片上系统还添加了以下模块:上位机通讯模块,连接上位机,接受上位机的指令并将其传输给主处理器,同时将控制器实时状态发送给上位机;主处理器,处理上位机的命令,发送任务,控制从处理器及其他模块完成任务;EPCS控制器对接外部的串行存贮器,通过搬运串行存贮器中的代码实现FPGA的数据配置;片上RAM模块存储主处理器的程序,提供主处理器程序的运行空间。

多处理器片上系统在单片FPGA芯片内部设计完成,FPGA通过外部接口与驱动板连接,获取位置、速度和电流相关信号用于处理计算,输出PWM波信号用于电机控制。每一路的电机控制模块对应一路功率驱动及信号采集电路,彼此无干扰、并行驱动。功率驱动及信号采集电路集成在一块驱动板上,由功率驱动电路、电流信号采集电路、位置速度反馈电路三部分组成。

3 单电机控制模块设计

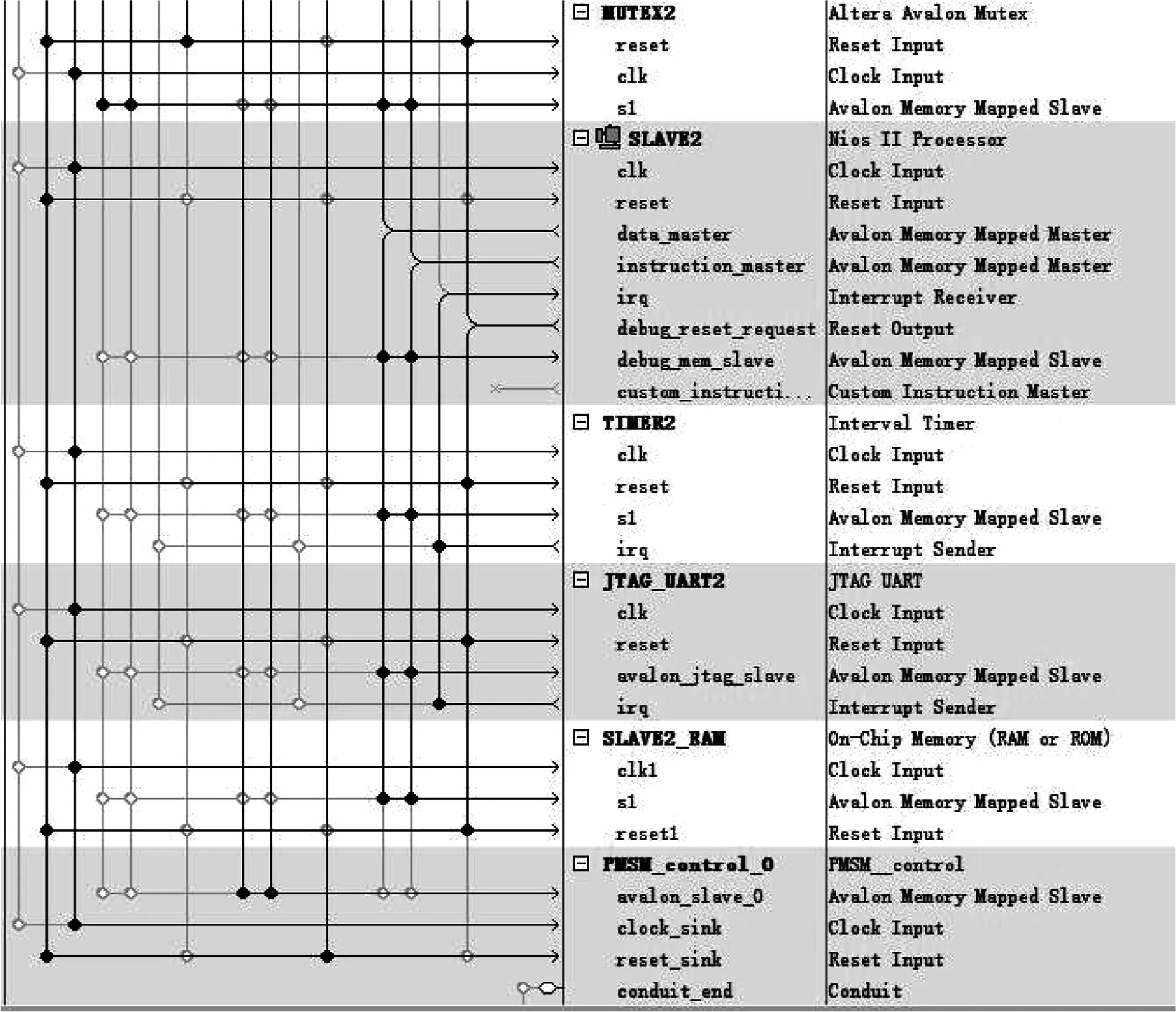

单轴电机的驱动及控制完全由电机驱动控制模块完成,其具体结构如图3所示,每一路电机驱动控制模块内部包括MUTEX核、从处理器、片上RAM以及电流环控制IP核等。下面将对电机控制模块内两个重点部分进行介绍。

图3 电机控制模块结构Fig.3 Motor control module structure

3.1 电流环控制IP核

电流环矢量控制算法以及信号采集检测和处理算法部分运算复杂,实时性要求高,选用纯硬件逻辑实现,可以提高电流环的频率响应。综合考虑速度与资源消耗的情况下,采用时分复用的方式提高系统整体的资源利用率,采用模块化的设计方式,增强系统的可利用性。电流环控制IP核具体结构如图4所示。

图4 电流环控制IP核结构Fig.4 Current loop control IP core structure

时序控制模块利用各模块的开启、关闭端口,控制时序,保证数据流向的正确性,最大程度的利用FPGA的并行处理能力。IP核内部时序关系如图5所示。

图5 电流环控制IP核各模块时序流程图Fig.5 Timing flow chart of each module of the current loop control IP core chart

电流环控制IP核中clark模块、park模块、pid_iq模块、pid_id模块、ipark模块以及SVPWM模块用于实现电流环的矢量控制算法,采用增量式PID算法实现控制;相电流采集及处理模块产生ADC接口所需的SPI信号和时序,根据通信协议进行信号采集,对信号处理、计算后得到三相静止坐标系下a轴、b轴和c轴的相电流;转速、位置计算模块接收位置、速度反馈元件的信号,对反馈信号进行处理、计算后输出电角度值、机械角度值、电角速度值以及机械速度值;CORDIC模块计算电角度值的正余弦值并将其输出;总线接口模块,通过Avalon总线与从处理器进行数据交互,接收从处理器发送的电流控制指令,并将机械角度值与机械转速值反馈给从处理器。

为提高控制系统的实时性,电流环控制IP核中所有模块均以硬件语言Verilog实现,在代码通过编译后,在Modelsim中进行功能仿真、时序仿真,再综合生成网表级文件,进行布局、布线、时序分析,将各个模块组合设计为自定义IP核。

3.2 从处理器

从处理器负责与主处理器数据交互、运行速度环算法和配置参数等功能,采用C语言编写软件程序实现功能。从处理器的软件控制程序由主程序及中断程序两个部分组成,主程序部分主要负责NIOS II程序初始化、参数初始化等功能,中断程序由实时中断以及定时器中断两部分程序组成。NIOS II处理器主程序流程图如图6所示。

图6 NIOS II处理器主程序流程图Fig.6 NIOS II processor program flow chart

主程序关闭全局中断,避免初始化被打断,然后对电机参数、控制器参数等进行初始化,进入实时中断程序,实时中断程序流程图如图7所示。

图7 中断程序流程图Fig.7 Interrupt program flow chart

外部信号触发进入实时中断程序后,NIOS II处理器读取IP核反馈的机械速度值,然后进行速度环计算,再将计算后得到的q轴电流给定值输出给对应轴的IP核进行电流环运算。

从处理器与主处理器的数据交互等功能由定时器中断周期性触发,保证伺服控制系统运行的正确性,方便设置整体系统参数。

4 两路实验系统的构建

为验证基于MPSoC的多轴伺服控制技术方案的可行性与有效性,对已构建的单轴电机控制模块进行两路拓展,在单片FPGA芯片内搭建两路实验系统,用于后续实验验证。

所使用的开发平台采用Cyclone V 5CEBA4F23C7N作为主控芯片,包含49K逻辑资源,Altera开发软件(Quartus II)提供了设计环境与库,NIOS II软核、Avalon总线以及可定制IP核,用于设计多处理器片上系统的体系结构。两路实验系统利用了FPGA内部32%的逻辑资源,5 476个自适应逻辑单元。FPGA时钟频率为50 MHz,电流环控制频率为100 kHz,速度环控制频率为25 kHz。

不仅可实现多轴电机驱动控制、上位机通讯等功能,也提高了控制平台的集成度。系统性的对软硬件功能进行规划,实现各功能模块在硬件和软件两方面的合理分配,系统灵活性得到提高,也有利于硬件、软件的设计,减少设计周期。

4.1 多处理器片上系统的搭建

在开发软件(Quartus II)中,利用其组件QSYS搭建三核处理器片上系统,为了构建片上系统,除技术方案中已有的主处理器、上位机通讯模块等功能模块外,还需添加JTAG UART核、Timer核、PLL核等功能模块完善片上系统的结构。

JTAG UART核能够实现PC机与处理器之间的串口通信,实现下载与程序调试功能;System ID核包含两个32位寄存器,可以将系统ID和生成时间写入相应寄存器;Timer核带有Avalon-MM从端口,常被配置为计时器测定时间,也可配置为周期性时钟源;PLL核用于产生稳定的系统时钟。

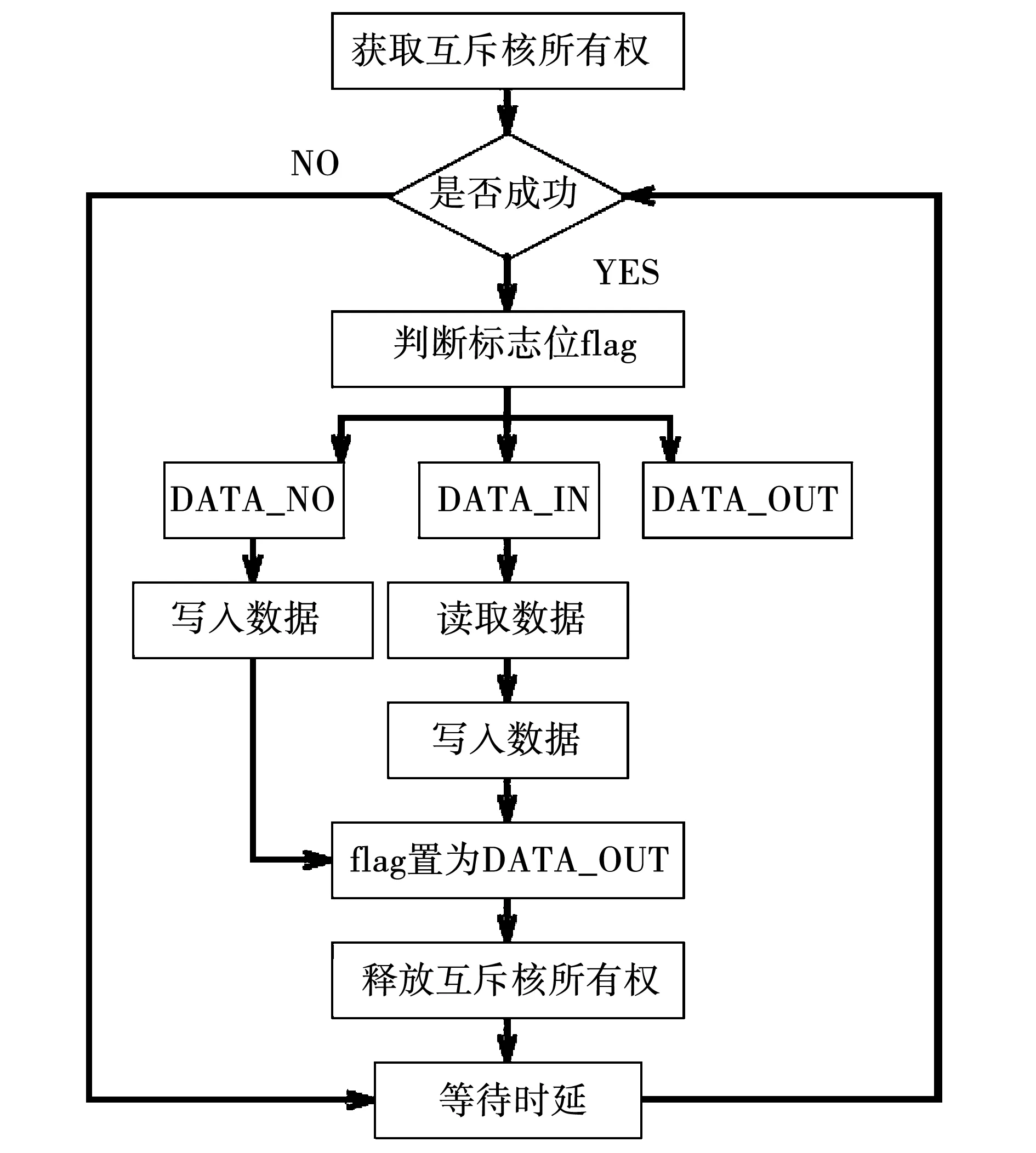

4.2 多处理器片上系统的通讯及上电自启动

处理器间采用Mutex核与片上共享内存结合的通讯方式,Mutex核是QSYS集成工具中一个基于Avalon总线接口的IP核,在一个时间段内,仅允许一个处理器访问特定的硬件外设。加入等待时延可避免多个NIOS II处理器对互斥核的争用。图8展示了基于Mutex核的通讯流程。

图8 基于MUTEX核的通讯流程图Fig.8 Communication flow chart based on MUTEX core

实际应用中,为避免大规模烧录,多处理器片上系统需实现上电自启动功能。在系统上电后通过Releasecp等Boot Loader引导程序启动加载功能,将存储在串行存储器中的主处理器软件程序转移至片上RAM中,主处理器将每个从处理器的启动映象复制到对应从处理器的程序存储片上RAM中,通过软重置(软件复位)控制从处理器从各自的程序存储器中顺序启动。

5 实验及验证

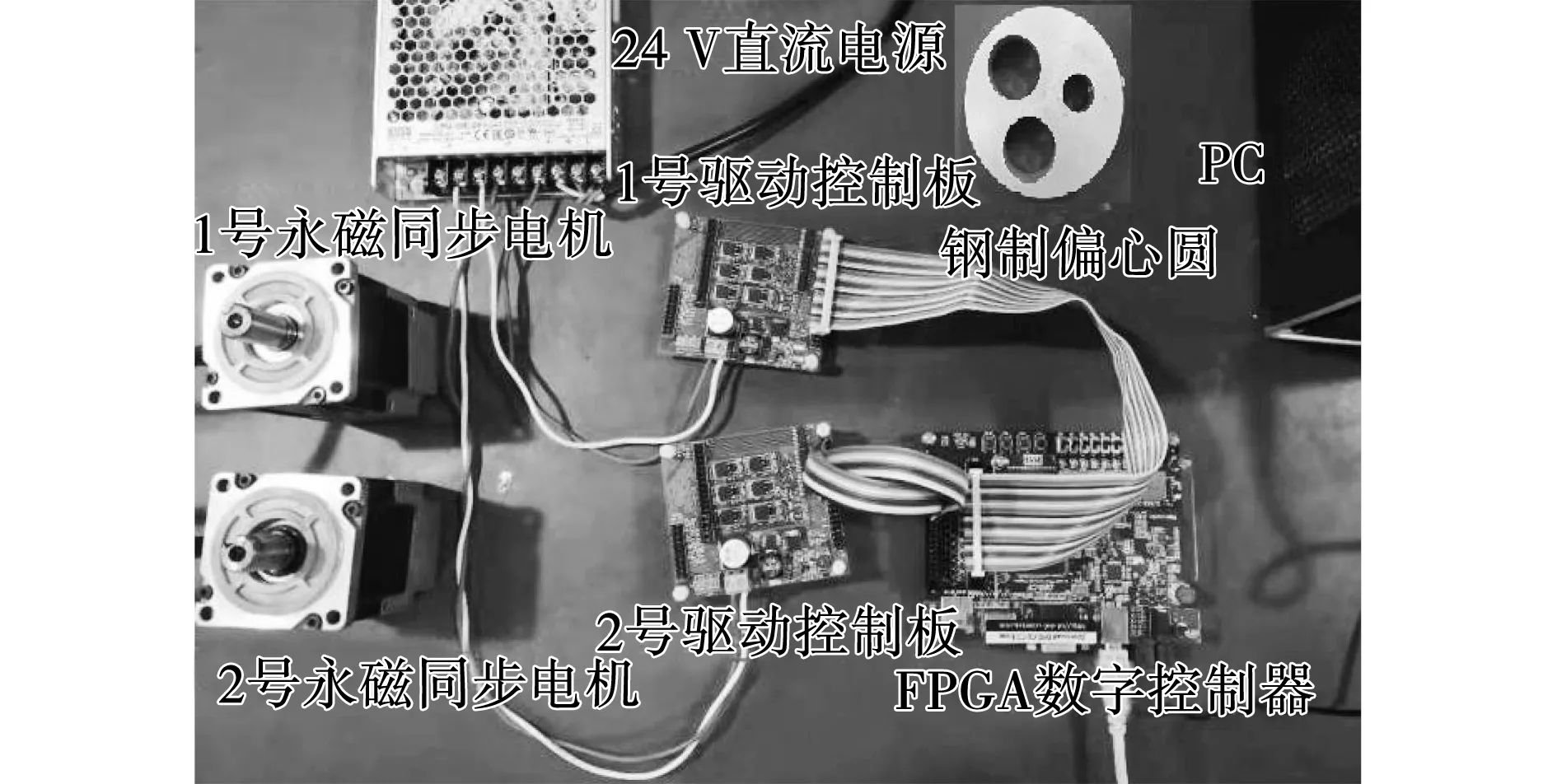

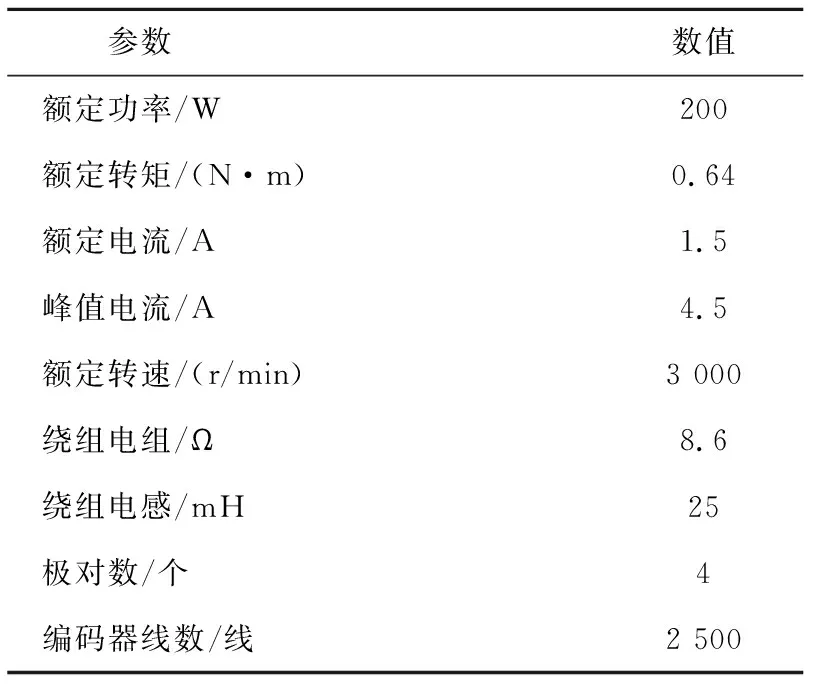

在永磁同步电机控制实验平台上,对搭建的两路实验系统进行实验验证,以Cyclone V 5CEBA4F23C7N作为主控芯片,采用增量式光电编码器与霍尔位置传感器作为电机位置、速度反馈元件,选用鸣志公司编号为SM0601EE2的永磁同步电机作为实验电机。验证平台如图9所示,主要包括两台永磁同步电机、24 V直流电源、两块驱动控制板、钢制偏心圆、FPGA数字控制器以及PC,PC负责调试程序以及充当上位机。实验电机参数如表1所示。

图9 永磁同步电机控制平台Fig.9 Permanent magnet synchronous motor control platform

表1 实验电机参数

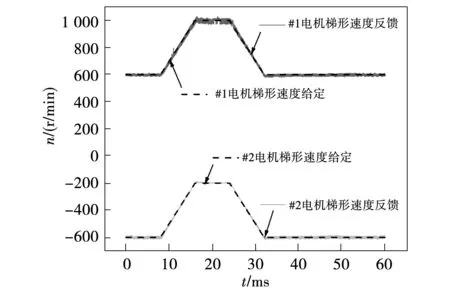

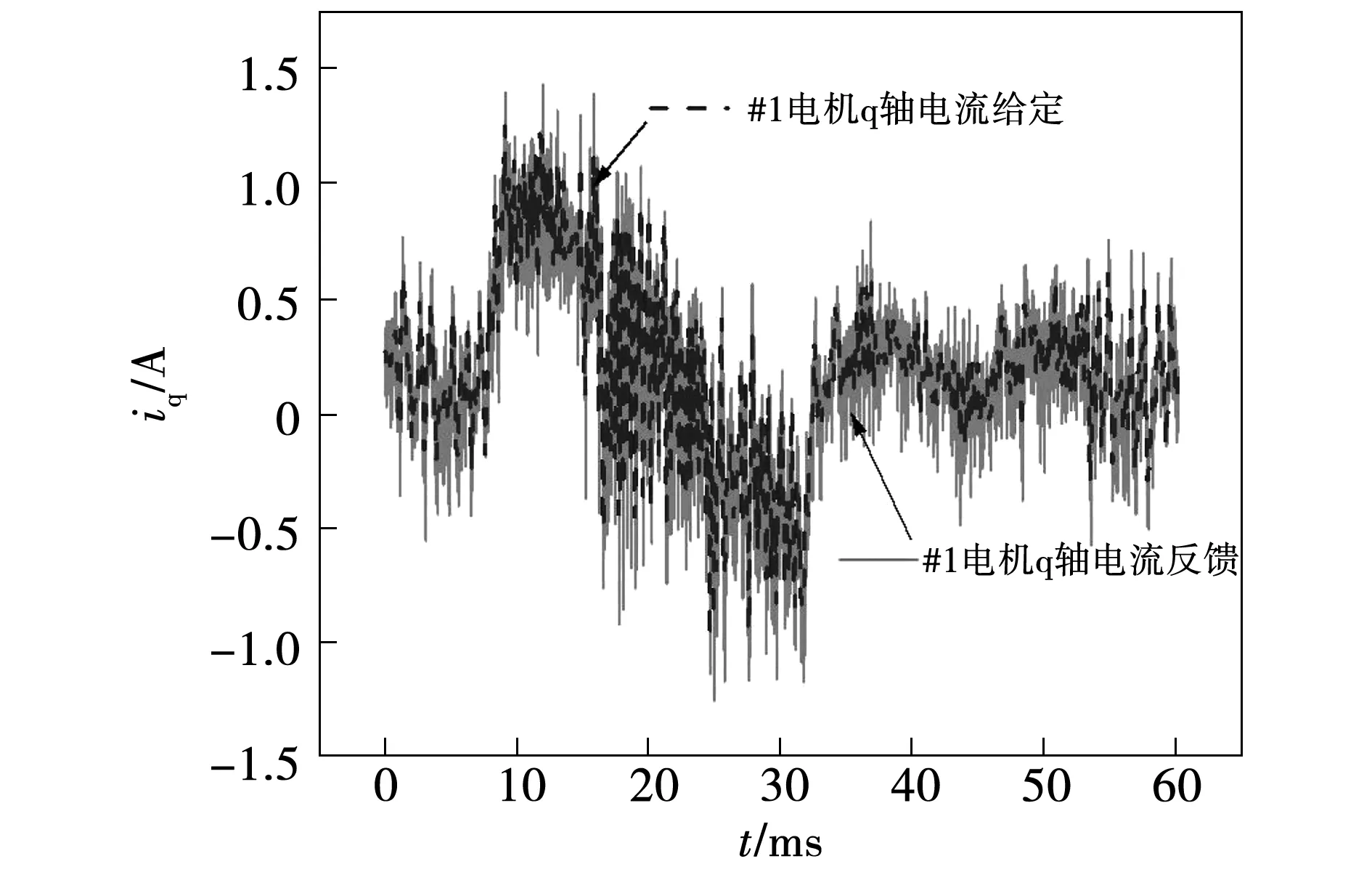

给定1号轴电机速度剖面为600 r/min到1 000 r/min的梯形波速度曲线,给定2号轴电机速度剖面为-600 r/min到-200 r/min的梯形波速度曲线。图10是两台电机在空载情况下的速度响应曲线。图11和图12分别是两台电机在给定梯形速度曲线下的q轴电流响应曲线。

图10 双轴速度剖面响应曲线Fig.10 Response curve of biaxial speed planing surface

图11 速度剖面1号轴q轴电流响应曲线Fig.11 Q-axis current response curve of the 1st axis of the speed planer

图12 速度剖面2号轴q轴电流响应曲线Fig.12 Q-axis current response curve of the 2st axis of the speed plane

由图可知,速度跟随情况良好,稳态误差小。在给定梯形波速度曲线的情况下,1号轴、2号轴的速度滞后小,跟随过程中速度误差分别为0.25%、0.32%。两台电机可以并行、互不干扰的完成指令,运行期间,电流环控制延时小,响应快。

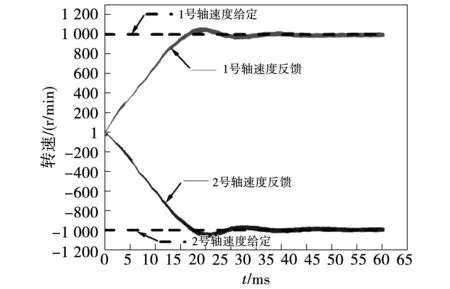

给定1号轴电机转速1 000 r/min,给定2号轴电机转速-1 000 r/min。图13是两台电机在负载情况下的速度响应曲线,其负载为钢制偏心圆,具体形状如图9中所示。

图13 双轴带负载给定速度响应曲线Fig.13 Two-axis load given speed response curve

从上述各图曲线可以看出,该控制系统速度环响应快,在带负载情况下会出现少量超调现象,稳态误差小,在给定转速的情况下,1号轴、2号轴的动态响应时间分别为17.3 ms与18.5 ms,稳态误差分别为1.13%、1.35%。

实验结果表明,基于MPSoC多轴伺服控制技术方案构建的两路实验系统,可使用单片FPGA芯片独立、同步的驱动两台电机,各轴之间并行控制、互不干扰,且控制精度高,速度跟随滞后小,电流环延时小,资源利用率高。

6 结 论

本文提出了一种基于MPSoC的多轴伺服控制方案,在单轴控制上,采用软硬件协作的方式实现伺服电机的闭环控制,使软硬件划分达到最佳平衡。结合MPSoC设计方法,构建了多轴伺服控制片上系统。实验结果表明,本文提出的基于MPSoC的多轴电机控制方案可以实现多轴电机的并行、同步驱动,调速响应快、滞后小,具有良好的动态响应与稳态特性,证实了本方案的可行性与有效性。