基于FPGA的高清HD-SDI视频采集系统设计与实现

2021-01-21钱宏文刘会付强王毅

钱宏文,刘会,付强,王毅

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

数字串行接口(Serial Digital Interface,SDI)是由美国电影与电视工程学会(the Society of Motion Picture and Television Engineers,SMPTE)制定的一系列由同轴电缆传输的非压缩数字视频接口标准[1]。目前,按照分辨率和传输速率的不同可分为标清SDSDI、高清HD-SDI以及3G-SDI 3种[2]。其中,HD-SDI接口遵循 SMPTE292标准制定,传送YCrCb(4∶2∶2)串行数字分量,采用720 P或1 080 P的格式,因其具有分辨率高,动态范围广以及在白平衡、亮度、对比度等方面的优异性,是当前广播电视行业高清成像及显示设备的主要接口形式,应用范围越来越广。

与此同时,高分辨率意味着高的数据带宽。因此,在采集HD-SDI高清视频信号,要求采用具有更高传输速率的通信方式。传统的USB2.0在实际应用中的最大传输速率仅为30~40 Mb/s,无法满足HD-SDI 1.485 Gb/s的传输需求。常用的CameraLink[3]图像采集接口虽然具有传输速度快和易于编程实现等优势,但因其需要额外的PCIe等采集设备才能在台式计算机上使用,因此存在通用性差,应用不便等缺陷。

USB3.0引入全双工数据传输[4],5根线中有2根用来发送数据,有2根用来接收数据,也就是说USB3.0可以全速进行数据读写,因此较USB2.0性能上具有很大的提升,其理论最大传输带宽在5.0 Gb/s(即640MB/s)[5],实际应用中可达1.7Gb/s(即220MB/s),完全满足HD-SDI 1.485 Gbps的传输需求。除此之外,采用USB3.0,在通用笔记本上即可完成视频数据的高速采集[6]。因此,基于USB3.0实现HD-SDI高清视频信号采集,可集合USB2.0和CameraLink两种接口的优点,具有应用方便、适用性广等优势。

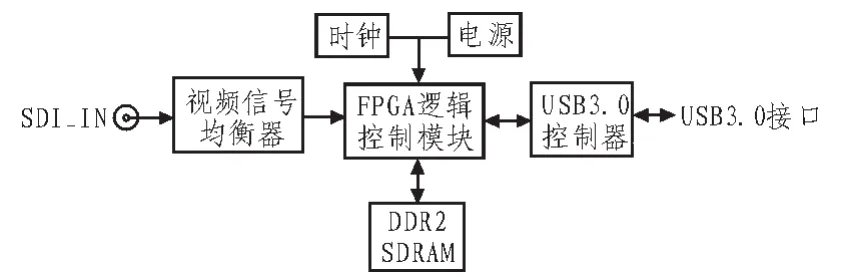

1 系统总体设计

高清视频采集系统(如图1所示)主要由视频信号均衡器、FPGA控制器、内部缓存DDR2 SDRAM、USB3.0接口以及时钟和电源组成。

HD-SDI高清视频信号由于速率比较高,经过同轴线缆长距离的传输会导致其高频成分衰减过大[7],因此,需要增加均衡器来减少高频信号的衰减,改善接收视频信号的传输质量。采用TI公司的SDI均衡器,不但能够自适应地调整高频增益,而且还能实现由LVPECL电平转化为LVDS标准电平,实现电平和阻抗匹配,从而能够使FPGA获得质量较高的SDI差分输入信号。

图1 采集系统设计框图

FPGA选用Xilinx的Virtex-5器件,其配置的Rocket I/O GTP收发器,可编程实现100 Mb/s到3.75 Gb/s的传输速率,能够满足HD-SDI 1.485 Gb/s的接收要求。

DDR2 SDRAM选用镁光(Micron)的128 M×16 bit器件,核心频率和工作时钟均为267 MHz,双边沿采样,数据时钟为534 MHz。因此,计算数据速率为:534 MHz(数据时钟)×16(数据位宽)×2(DDR2数量)×80%(读写效率)=13 Gb/s;系统DDR2的速写数据吞吐量为3.4 Gb/s,因此,该文采用的DDR2帧缓存方案可满足HD-SDI系统传输带宽需求。

USB3.0控制器选用CYPRESS的EZ-USB FX3,内部集成了512K的SRAM、ARM9内核以及丰富的IO接口(如GPIF、UART等),满足文中方案的设计需求。

时钟模块主要为FPGA提供所需的参考时钟,主要包括以下内容:

1)系统时钟(时钟频率为100 MHz);

2)Rocket I/O GTP收发器的参考时钟(时钟频率为148.5 MHz);

3)DDR2控制器IP核的输入参考时钟(时钟频率为 267 MHz)。

电源模块为系统上所有子模块供电。

2 FPGA程序设计

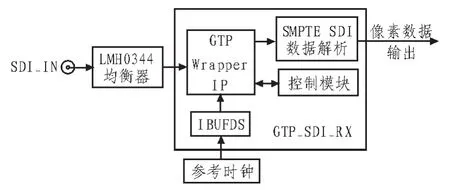

2.1 基于GTP的SDI接收模块

当前,利用FPGA接收SDI信号主流有两种处理方案:一是利用解串芯片将从同轴电缆传输并均衡后的串行视频信号转为并行信号,然后将并行信号发送给FPGA进行处理;另一种是利用FPGA的高速收发器即将同轴电缆传输并均衡后的HD-SDI信号直接输出到高速BANK的差分端,利用高速收发器进行解串。与前者相比,后者设计简单、成本低、配置灵活且有成熟的高速IP(GTP_DUAL)支持,因此,采集系统选用第二种方案,模块框图如图2所示。

图2 GTP SDI接收模块框图

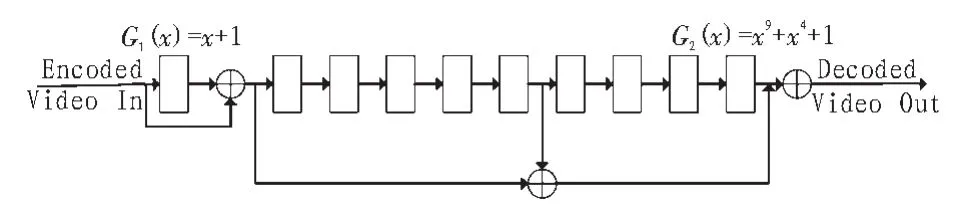

具体实现流程:首先GTP利用时钟恢复电路(CDR)将输入的HD-SDI信号的时钟和数据恢复出来;然后对接收到的HD-SDI数据解码,解码流程如图3所示包括将不归零倒置码(NRZI)转为归零倒置码以及对NRZ解扰[8]。

图3 HD-SDI信号解码流程

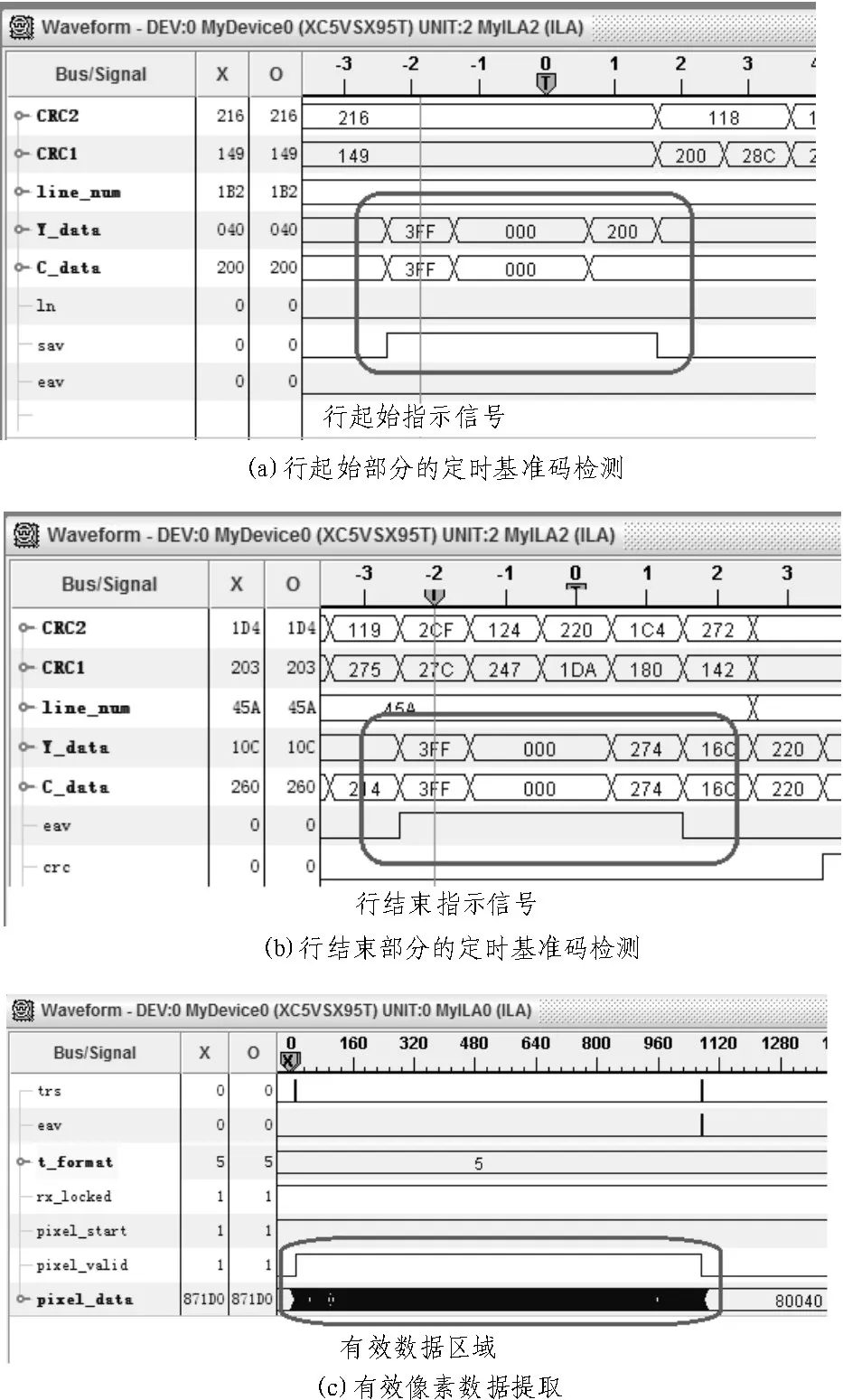

在调整图像采样后可输出Y分量和C分量(Cr或Cb)。接着对两个分量进行序列检测,即提取分量中的定时基准码(TRS)[9],如图 4(a)、(b)所示。最后,利用提取的TRS判断视频格式、分辨率及帧频以及数据的稳定性(在图4中判断mode_locked和rx_locke是否锁定即是否为高,锁定后可分别判断模式是HD-SDI、SD-SDI还是3G-SDI以及传输的数据格式即分辨率和帧频)。在稳定后,可从中提取有效的像素数据,如图4(c)中椭圆区域标识所示。

图4 HD-SDI信号接收时序

控制模块的主要功能包括GTP收发器的主复位(包括GTP_DUAL内部的PLL复位)、发送器复位、接收器复位以及速率检测。

2.2 DDR2帧存储

系统中视频流以逐行扫描1 080 P格式持续输入,图像的分辨率为1 920*1 080,帧频是25 f/s,图像像素时钟是74.25 MHz,每帧图像的包含2 640*1 125个像素时钟,即行消隐720个像素,场消隐45个行周期,传输一帧视频数据用时40 ms[10]。

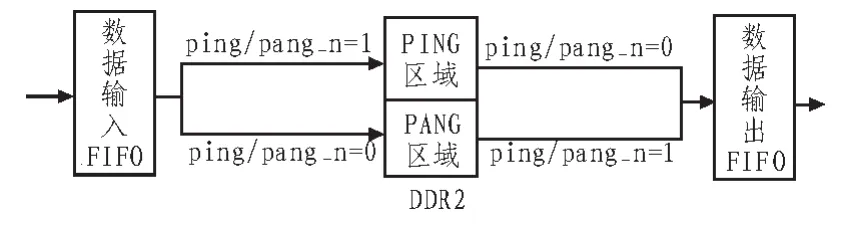

有效图像数据提出后,经FIFO作跨时钟域处理后,输入至DDR2进行缓存后按要求的输出格式经输出FIFO读出。在流水线处理的过程中,为防止读写冲突,采用乒乓处理,即对PING区域进行写操作时,对PANG区域进行读,反之亦然。DDR2帧存储模块框图如图5所示。

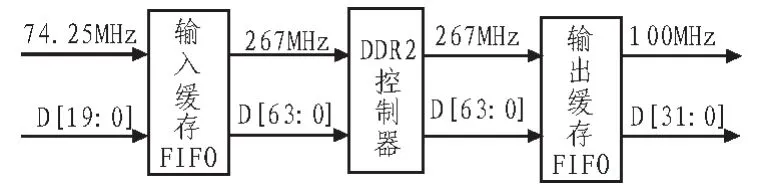

2.3 跨时钟域处理

HD_SDI信号在经过解码、缓存至USB接口输出,共跨过3个时钟域:

图5 DDR2帧存储模块框图

1)GTP经CDR模块恢复出的时钟,频率为74.25 MHz,数据位宽为20位(Y分量与C分量各10位);

2)Xilinx IP核输出的同步时钟,频率为267 MHz,数据位宽为64位(双边沿采样,数据位宽为DDR2 SDRAM位宽的2倍);

3)USB3.0控制器的Slave FIFO输入时钟,频率为100 MHz,数据位宽为Slave FIFO位宽即32位。

跨时钟域处理如图6所示。

图6 跨时钟域处理

为解决以上3个时钟域不同步给系统所带来的亚稳态问题,该文利用异步FIFO,通过空满、近空近满等标志信号控制读写速率[11],实现不同速率不同位宽接口的无缝连接。

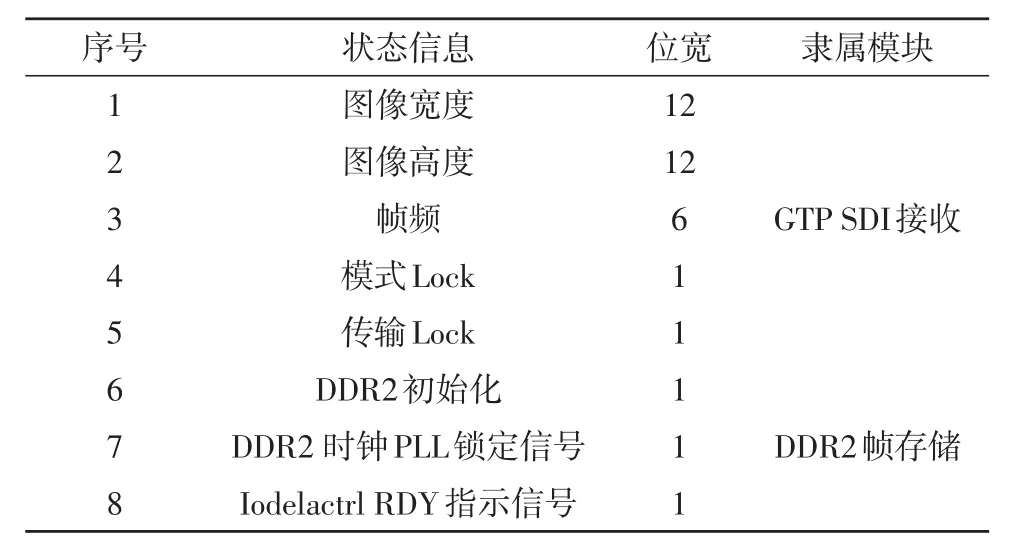

2.4 USB3.0接口控制模块

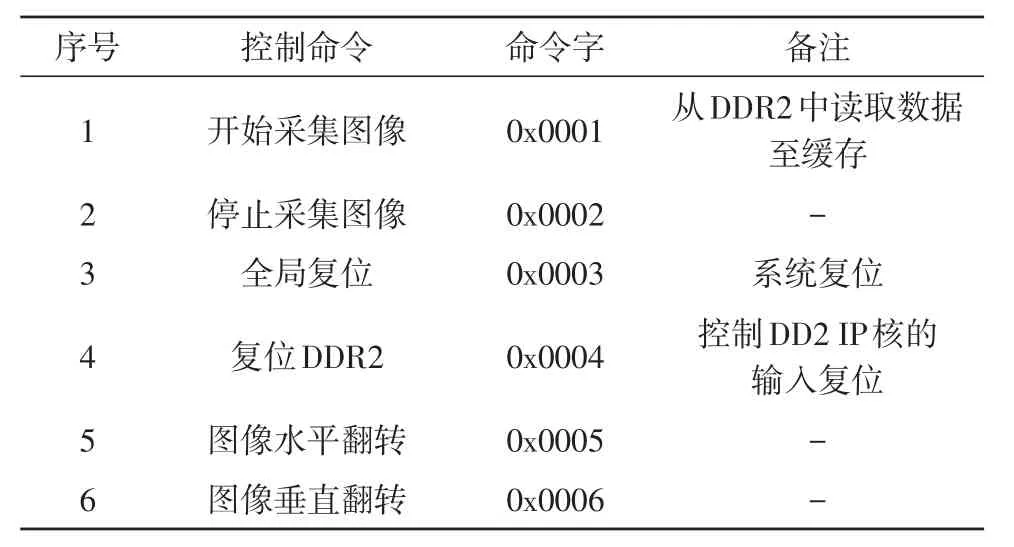

USB3.0控制接口模块通过控制FX3与FPGA的GPIF II接口,实现FPGA与FX3之间的数据交互。在该方案中,FPGA每秒定时将1 920×1 080的25帧HD-SDI图像数据以及信号的连接状态和各个模块的工作状态(系统监测信号如表1所示)[12]上传给FX3,同时FX3将上位机控制指令(如表2所示)下发给FPGA以同步和控制各个模块的运行。

表1 状态监控

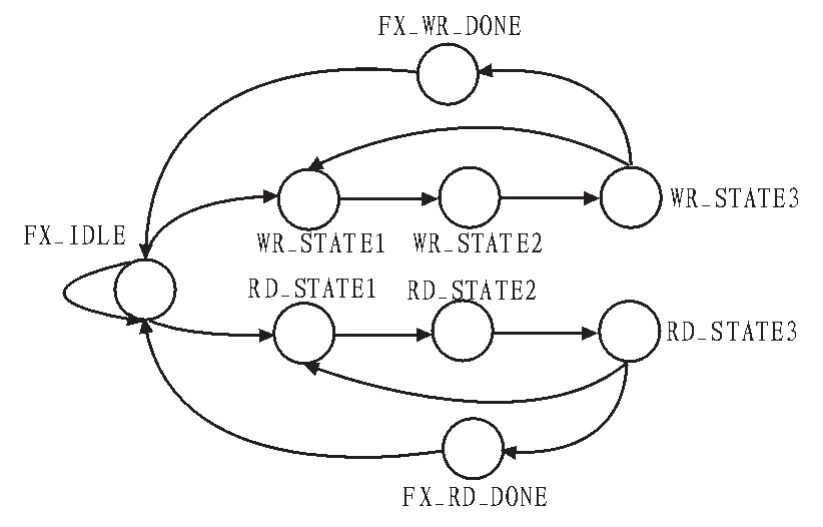

如图7所示,为USB3.0控制模块的状态转移图[13]。系统上电复位,状态机处于空闲态(FX_IDLE),当检测到图7中输出缓存FIFO不空时,状态切换至WR_STATE1,开始向Slave FIFO中写入数据,写状态定义如下。

表2 控制指令

WR_STATE1:写入指定的FIFO地址;

WR_STATE2:将写命令使能(低有效);

WR_STATE3:把写入的数据送到数据总线;

在完成1次写操作后即在WR_STATE3状态时判断数据是否写完(即输出FIFO是否为空),未写完则进行下一次写操作(即WR_STATE1状态),写完则跳转至FX_WR_DONE状态,最后回到FX_IDLE状态。

当检测到Slave FIFO的读状态为高即不空时,状态机由FX_IDLE切换至RD_STATE1,开始从Slave FIFO中读取数据。读状态定义如下:

RD_STATE1:写入需要读取的FIFO地址;

RD_STATE2:数据输出使能(低有效);

RD_STATE3:将读指令使能(低有效)。

在完成1次读操作后即在RD_STATE3状态时判断数据Slave FIFO的读状态是否有效,有效则进行下一次读操作(即RD_STATE1状态),无效则跳转至FX_RD_DONE状态,最后回到FX_IDLE状态。

USB3.0接口控制状态机如图7所示。

3 USB3.0控制器

3.1 固件程序设计

在固件程序设计中,为缩短设计开发周期,该系统使用CYPRESS提供的SDK开发包[14]。

固件的设计分为两部分,一部分是利用GPIF II Designer工具完成GPIF II接口设计,编译生成与接口配置相关的C头文件;另一部分是把头文件添加到固件工程中,使用Eclipse编译,利用SDK开发包中的API接口调用固件程序[15]。

3.2 接口速率测试

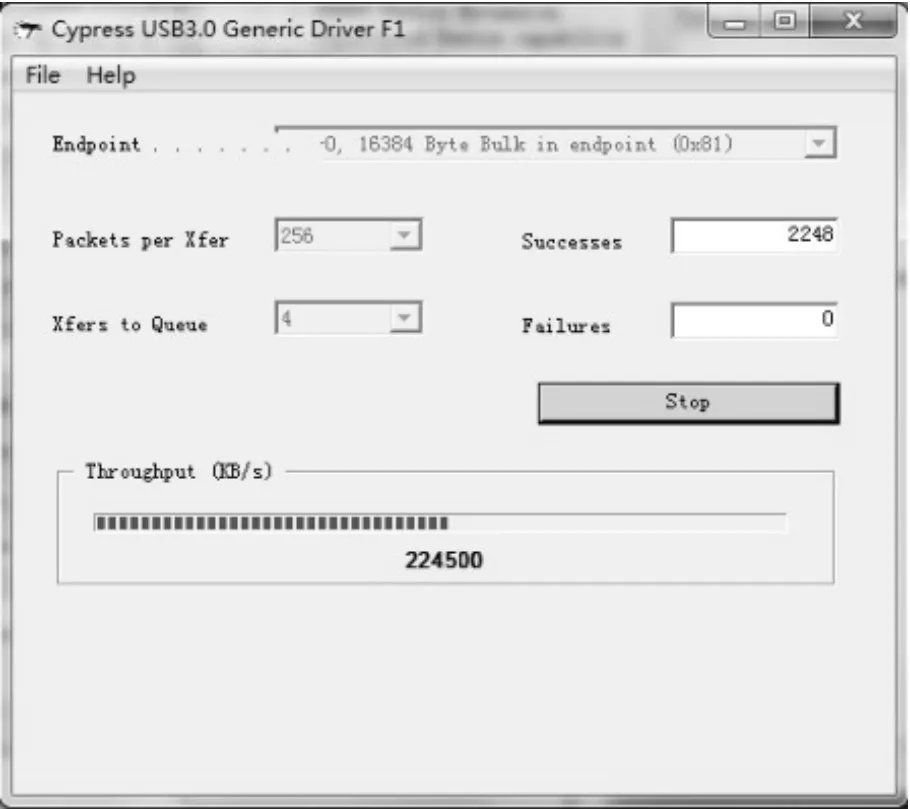

利用CYPRESS的Streamer软件对USB3.0接口进行最大速度测试。内部产生0~255的循环测试数据,向输出缓存FIFO写入,并将数据读出发送给Slave FIFO[16]。

图7 USB3.0接口控制状态机

如图8所示,该系统USB3.0的数据最大读取速率可达到224.5 MB/s,能够满足HD-SDI高清图像采集系统的传输速率要求。

图8 USB3.0数据速率测试结果

4 结束语

文中利用FPGA和USB3.0控制器实现了高清HD-SDI视频信号的采集及高速传输。充分利用FPGA内部的Rocket IO资源,既提升系统性能又降低了硬件成本,具有使用方便、适用性广等优势。除此之外,系统性能留有较大余量,FPGA软件调整后,可灵活兼容HD-SDI及3G-SDI接口标准[17],为其他种类SDI接口的应用拓展提供了参考和指导,具有实际应用价值。