基于FPGA的DDR2_SDRAM控制器用户接口设计

2021-01-21闫永立李勇彬马嘉莉

韩 笑 ,闫永立 ,2,李勇彬 ,马嘉莉 ,2,吴 斌 ,2

(1.中国科学院大学,北京 100049;2.中国科学院微电子研究所,北京 100029;3.湖南大学,湖南 长沙 410082)

随着现代社会数字化的高速发展,大容量数据存储系统作为各个系统中的核心子部分,其重要性不言而喻,对数据处理的速度、实时性、稳定性以及功耗等要求也越来越重要。市面上可供选的主流存储器有FLASH,DRAM,SRAM等,而由于JEDEC标准的DDR SRAM系列存储器相较于FLASH、DRAM,可以在时钟双沿工作,数据传输速率高,带宽大,并且存储相同数据量信息消耗更少晶体管,因此也有容量大、功耗低等优点,特别适合对海量数据存储的场景。鉴于DDR接口读写时序不是特别容易简单实现,这就推动了商家研发对用户使用友好的存储器控制器。控制器可以完成自动刷新、存储器掉电重启、读写时序控制等底层基本功能,使用者基于简单控制器接口进行二次开发,就可以向存储器正确读写数据。这样可以缩短开发周期,减少设计人员的工作量,简化系统设计。考虑到DDR系列存储器性价比等实际因素,设计选用DDR2作为缓存存储器,使用Synopysy公司设计的DDR2 Controller商用IP[1]。在验证硬件平台方面,选用Altera公司StraixIII开发板外接DDR2 SDRAM内存条。此外,因为产品接口标准不统一,为了在信号时序方面将Synopysy与Altera两家厂商的存储器控制器模块与PHY模块匹配,设计了专门接口转换模块。

综合上述分析,文中在Stratix系列FPGA开发板上借助硬件描述语言设计了一套控制器用户接口设计方案。

1 整体架构

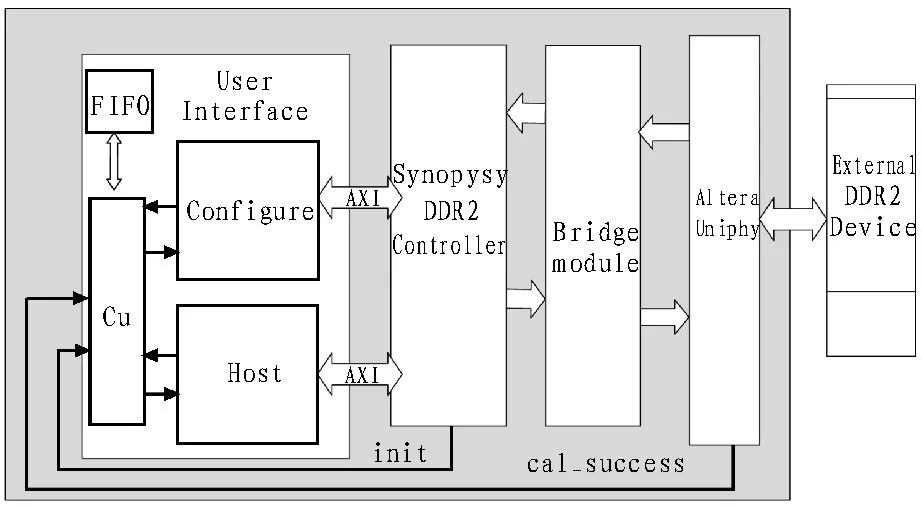

系统使用Altera公司开发的EDA软件Quartus II例化的Uniphy IP[2]模块作为PHY(Physical Layer Interface,物理层接口)层,整体架构如图1所示。

图1 整体架构图

整体模块一共包括四大模块:

1)用户接口模块:上位机数据的接收、缓存,通过AXI 3.0协议[3]接口将配置信息、待存数据及相关控制命令发送给DDR2控制器模块。

2)DDR2控制器模块:上电后对存储器进行一系列配置,完成初始化操作;在使用者进行数据读写任务时,将用户单沿操作的数据链路通过电路转换成符合存储器双沿数据的传输要求。在写操作时将用户发送过来的待发送数据以及数据写传输控制信息,编码成符合存储器接口标准制定的写操作指令,在读操作时先将用户侧发来的读地址、读数据长度编码成读指令发送给存储器,控制存储器读出相应数据,然后从存储器反馈回的信息中解析出读出的数据发送给用户端。控制器每隔一段时间都会启动自动刷新命令,用于保证存储器内数据不丢失。

3)桥接模块:主要负责Synopysy控制器IP与Altera Uniphy硬核IP接口信号转换,实现不同时序要求的IP间信号正常交互。

4)PHY:使用Quartus II软件提供Uniphy硬核IP作为PHY层,发送控制器信号和接收来自物理通路的信号[5-6]。

2 模块介绍

2.1 用户接口模块

作为数据缓存系统的核心模块之一,用户接口模块细分成控制逻辑模块Cu、配置模块、数据发送接收模块等3个小模块。

通过异步FIFO进行时钟域隔离并将上位机指令信息缓存,控制逻辑模块Cu负责协调配置模块Configure和数据发送接收模块Host的工作,分别启动两个模块通过AXI 3.0协议接口与控制器模块交互,交互内容包括上位机提供的配置、控制命令及缓存数据等。

cal_success为Uniphy IP发出的校准信号[7],为高电平时表示已完成PHY层校准,可以与存储器进行数据传输。init为控制器IP模块反馈的信号,为低电平时指DDR2 SDRAM与控制器已经完成初始化操作。在控制器上电初始化期间根据用户端配置指令安排,完成控制器工作模式设置、存储器时序参数设定等任务[8]。

在完成PHY校准和初始化操作以后,数据发送接收模块Host就可以根据用户端读写指令,在需要存入数据时发出写操作指令,同时将要写入存储器的地址与待写数据一并发出,与之类似,需要读取数据时发送给控制器读操作指令并将要读取存储器的地址信息一并发出。

2.2 DDR2控制器模块

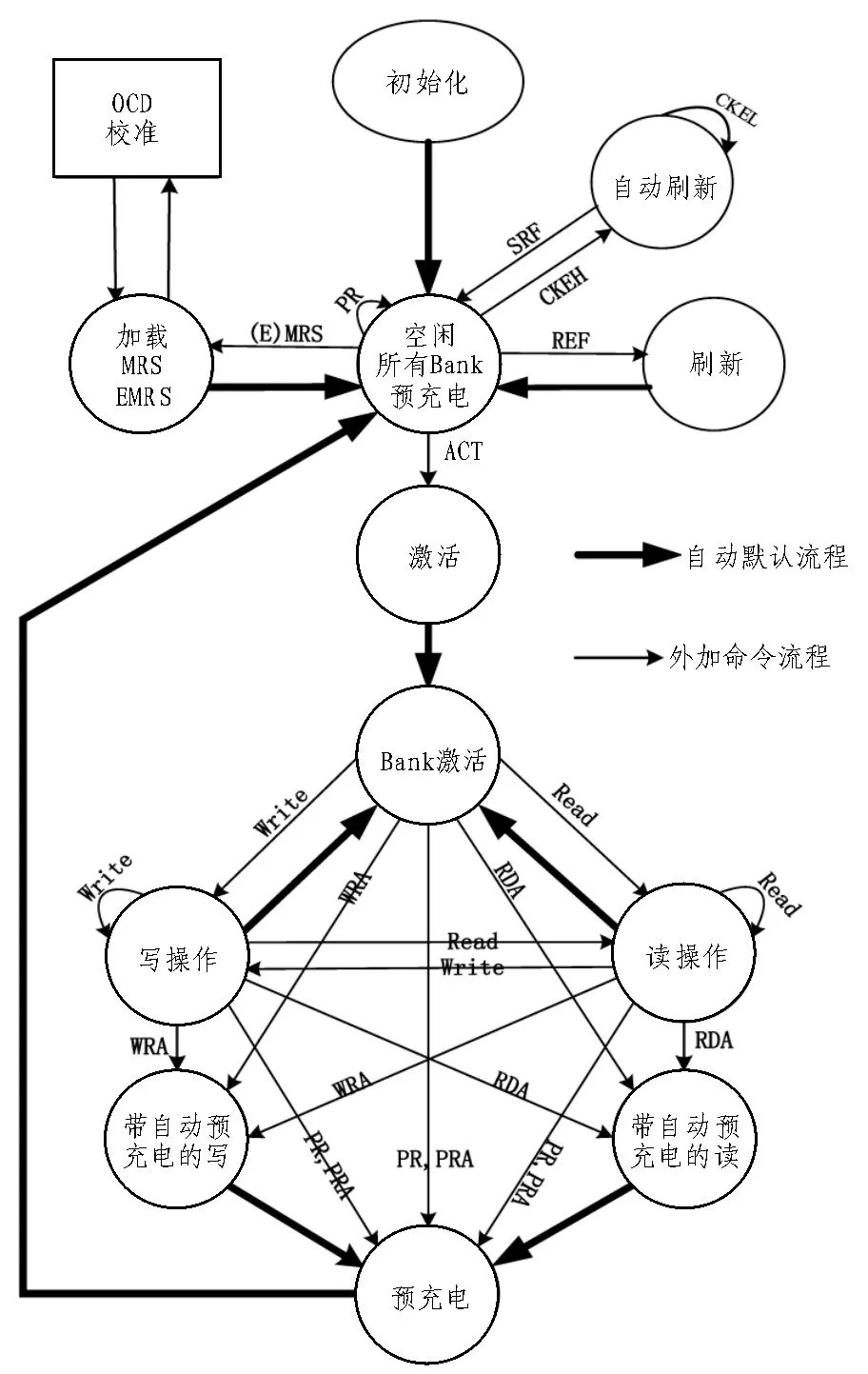

由于DDR2操作流程复杂,因此要想正确地读写数据,就需要遵循相应JEDEC标准设计存储器工作流程,图2介绍了DDR2存储器在工作时完整的状态转换[9-10],由该图可以清楚地看到各状态跳转所需要的命令或者需满足的条件。

状态机描述了DDR2各个状态的转换以及转换时所涉及的一些命令。DDR2控制器的设计实质上是围绕着该状态机的设计进行的,以确保进行正常工作。

正如图2所示,在用户端发起读写操作前,需要存储器在上电状态下进行校准和若干初始化过程。在这期间,根据用户端配置要求,将控制器中对工作模式寄存器(MR)等多个配置寄存器进行设定。为了配置这些寄存器,用户端需要提供CAS指令延迟、DRAM大小、DRAM数量、自刷新的周期等配置信息。只有在控制器初始化完成后,用户端才可以对DDR2存储器进行正式的读写任务,并且由于DDR2的结构特点,需先选定Bank以及该Bank下所在行(Bank地址和行地址同时发出)后,再选定列地址及发出读写指令。

图2 DDR2简单状态转换图

2.3 桥接模块及PHY模块

桥接模块处理Synopsys的Controller信号,根据不同的类别做处理(分成控制通路信号、写数据通路、读数据通路)以匹配UniPHY接口连接与时序[12],并增加UniPHY所需要的控制信号处理。两家公司在PHY-Controller之间存在接口时序和连接的差别。

2.3.1 接口对比

Altera的UniPHY与controller之间的接口有自己定义的AFI接口规范,接口分类为SDR系列、MEM接口、时钟及复位。

SynPHY的接口信号包括DLL的配置、IO的配置及控制、SDR系列(和Altera的部分相似,还有一些时序上不同)、PHY的配置部分、MEM接口。

2.3.2 工作模式对比

Altera controller工作方式主要有Half rate与Full rate模式,在Full rate模式时,和Synopsys的模式相似,即Local侧、Controller侧与Memory侧工作时钟相同,单沿触发(均在上升沿工作),数据位宽是Memory侧的两倍。

2.3.3 时钟域对比

从时钟域看(full rate前提下)[13],Altera UniPHY提供给Memory和Local、Controller侧的时钟同频同相,而SynPHY的是同频不同相,Memory侧的时钟要滞后 90°。

2.3.4 接口时序对比

1)指令与地址不同,Synopsys指令持续时间为两个clock,而Altera相同功能指令只维持一个clock,指令格式相同,连续的写指令之间Synopsys夹的是nop指令,Altera的是 deselect device指令[14]。

2)都是通过数据有效信号标志输入数据有效及维持的时间。

3)Synopsys中没有类似的afi_dqs_burst信号,UniPHY中afi_dqs_burst必须比afi_wdata_valid信号提前一个周期到达。

4)Memory侧,Altera的 UniPHY命令和SynPHY的一致。

5)对于写数据和写数据有效信号的延迟,UniPHY中根据afi_wlat需要调整数据相对于指令的延迟,范围为0~63。

Synopsys中的数据与指令的时序关系是固定的,相当于Altera的afi_wlat=0情况。

PHY指的是DDR2控制器和DDR2存储芯片之间的电路部分,保证读写过程中DQS信号能够以精确的相位偏移发送和采集数据[15],目的是实现数据高速稳定地传输。

3 系统测试

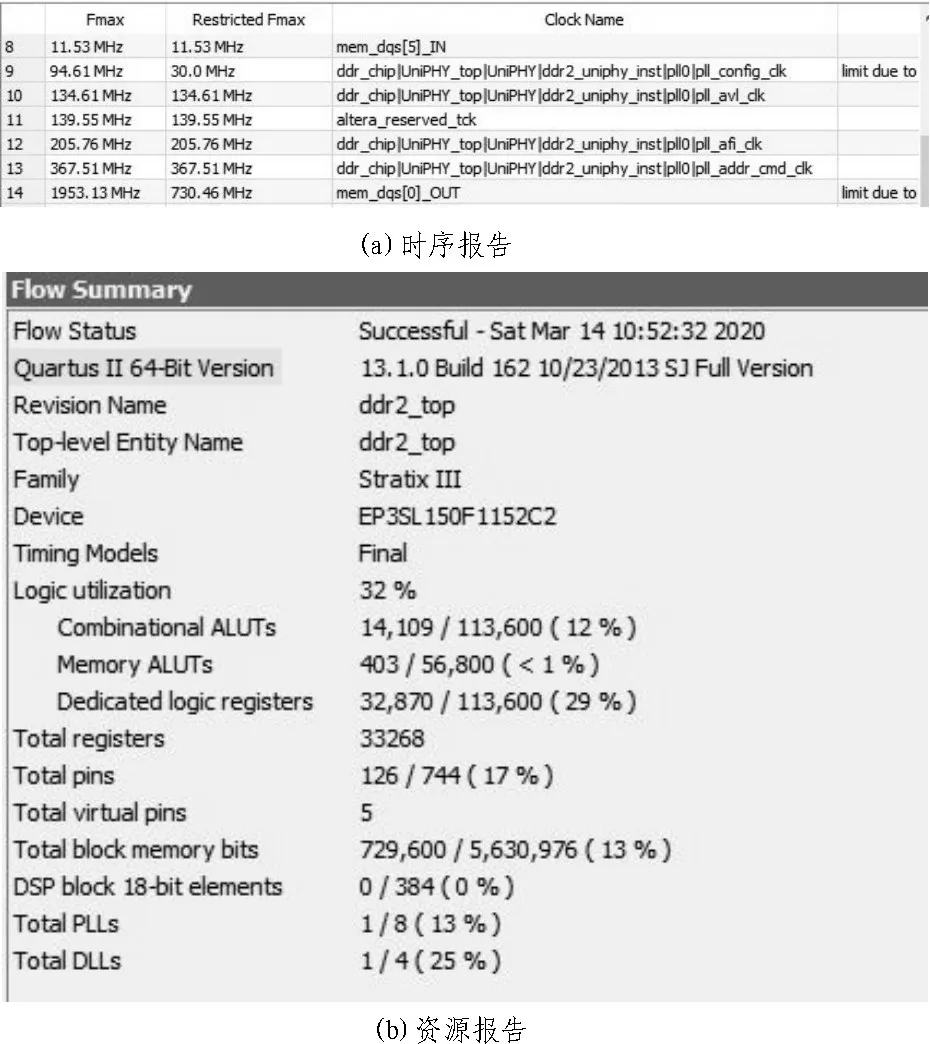

文中基于Intel的EP3SL150F1152C2器件进行了设计实现,并在Intel FPGA Stratix III开发板上进行功能验证。

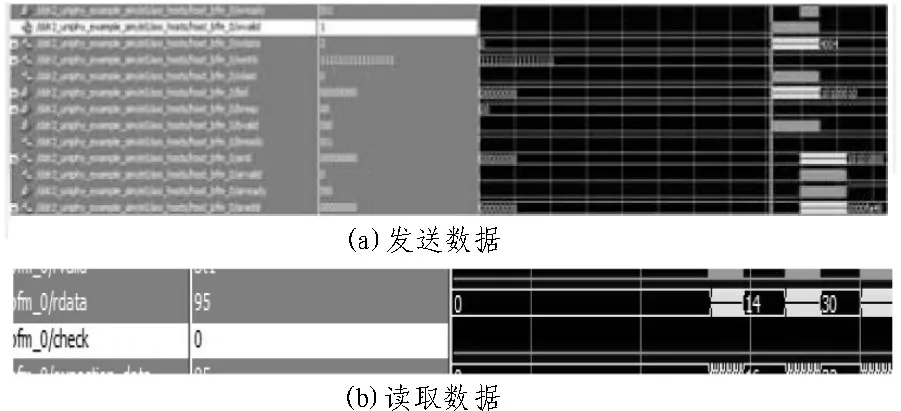

Modelsim仿真AXI突发长度为1,大小为4 kB数据的测试案例,读写命令正确写入,读出数据结果正确,如图3所示。

图3 仿真测试

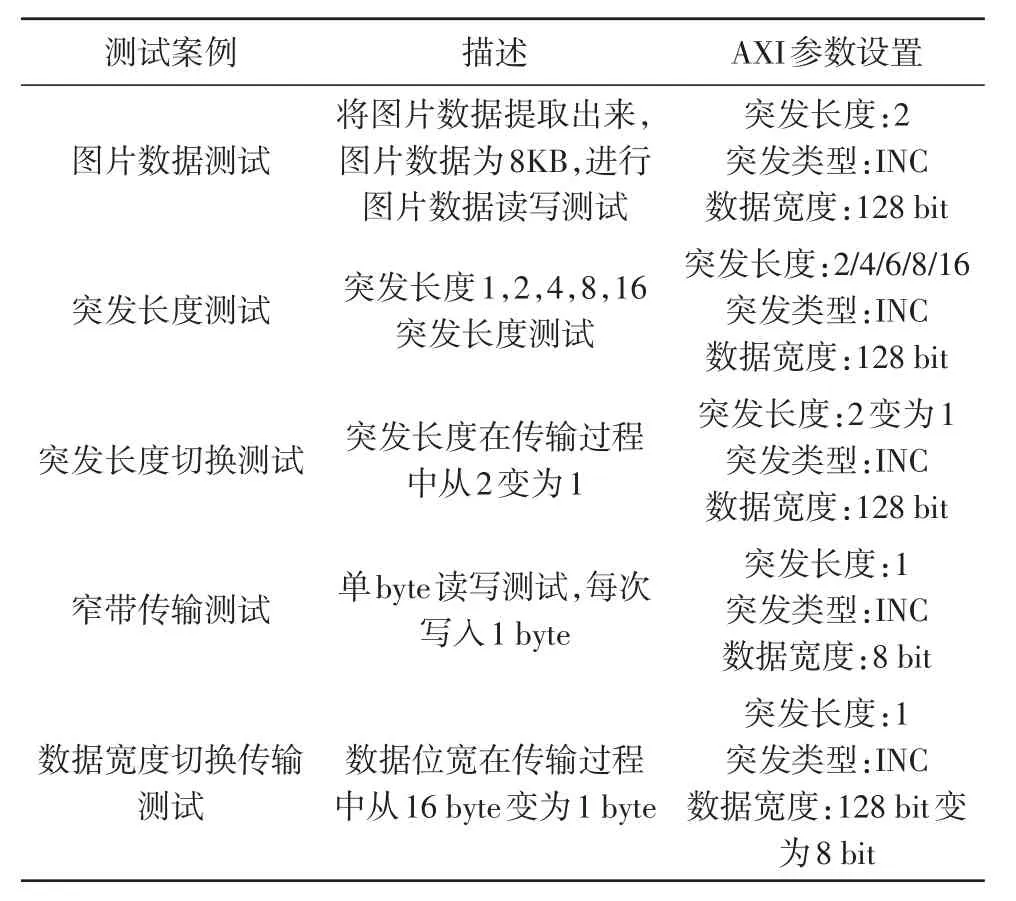

多组测试案例如表1所示。

表1 测试案例

利用Quartus II 13.1 EDA工具进行了综合、时序约束、生成网表等。处理后综合结果如图4所示,报告表明,系统可以达到200 MHz频率设计要求。

在进行系统硬件功能验证时,使用ROM IP预先存入待存数据代替上位机指令缓存FIFO,使用SignalTap导出读出数据文件,并与写入数据文件对比,结果正确。

4 结束语

针对现代数据缓存系统的要求,文中在Stratix系列FPGA开发板上借助硬件描述语言设计了一套控制器用户接口设计方案。保证数据实时缓存。使用硬件语言实现了用户接口模块和桥接模块的设计,解决了控制器与PHY层的接口匹配问题,达到了大批量连续数据读写存储的目的。最后通过FPGA完成了对系统整体的功能验证。

图4 综合报告