基于FPGA的PAL制视频信号产生器设计*

2020-12-02崔少辉王法臻马铭骏

王 成 崔少辉 王法臻 马铭骏

(1.陆军工程大学石家庄校区 石家庄 050003)(2.65655部队 赤峰 024000)

1 引言

为了满足火炮窥膛、导弹电视跟踪模块等测试的需求,现在通用自动测试系统中大多安装模拟图像采集卡用以完成装备图像采集分析任务[1],这样就需要研究模拟图像产生装置,供自动测试系统功能自检使用。然而市场上并没有方便获取的模拟信号的视频信号产生器,以往自动测试系统中图像采集卡自检往往通过在自检适配器中安装摄像头,图像采集卡连接摄像头输出完成功能自检,这种方式的缺点在于需要为摄像头单独开孔,而且难以固定。为了解决上述问题,本文基于FPGA的PAL制视频信号产生器,同时研究了VHDL程序自动生成技术,实现了图像生成过程中的“所见即所得”。

2 基于FPGA的PAL制视频信号产生器系统的设计

考虑到我国电视及国内图像采集卡都支持PAL制式,因此视频信号产生器也基于PAL制式[2]。PAL制式,由Walter Bruch提出,即逐行倒相制式。通过采用逐行倒相的方法,以扫描方式传送图像数据[3]。图像数据传送速率每秒25帧,每帧625行[4],分为奇数行和偶数行两场的隔行扫描——即每秒50场,每场312.5行,场扫描频率为50Hz,行扫描频率为15625Hz,周期为64μs[5]。

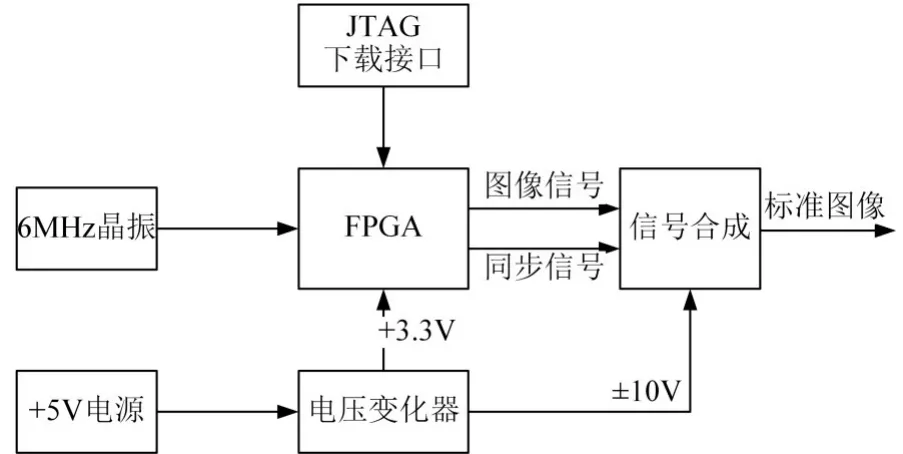

基于FPGA的PAL制视频信号产生器系统框图如图1所示,系统采用6MHz晶振,系统采用外接+5V电源输入,系统通过电压变换器,输出3.3V电源给FPGA芯片使用,±10V电源供为信号合成模块中的运放供电,FPGA需要产生图像信号和同步信号两路信号。

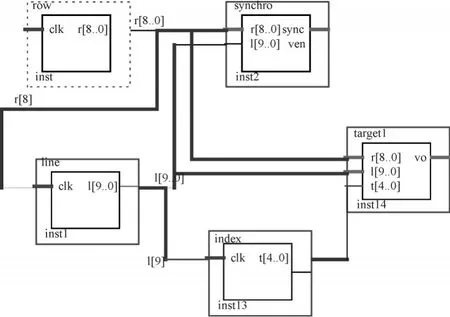

为了达到在电视屏幕上正确地显示视频信号的目的,将视频信号设计为电视信号的625行、每行时间为64μs,使视频图像点阵与电视扫描位置一一对应,并利用行计数器和列计数器记录当前的扫描位置,同时根据行/列计数器的值确定各信号的输出。FPGA的顶层设计如图2所示。

图1 基于FPGA的PAL制视频信号产生器系统设计框图

图2 PAL制视频信号产生器的FPGA顶层设计原理图

3 视频信号产生器系统设计的实现

3.1 同步信号的产生

根据PAL制式同步信号产生的需求,若采用6MHz晶振,每行64μs对应的计数值为384,对应384进制的列计数器,5种负电平的同步信号对应的起始时刻、脉宽、列计数器值分别为

S0:0μs开始,脉宽4.7μs,计数值0~28;

S1:0μs开始,脉宽27.3μs,计数值0~164;

S2:32μs开始,脉宽27.3μs,计数值192~356;

S3:0μs开始,脉宽2.35μs,计数值0~14;

S4:32μs开始,脉宽2.35μs,计数值192~206;

其中,S1~S4为场同步和帧同步信号,S0为行同步信号[6]。

设1为行计数器的值、r为列计数器的值,sync为同步信号输出,则它们之间的关系用VHDL语言可描述为

同步信号产生模块的仿真波形如图3所示。

图3 同步信号产生模块的仿真波形

3.2 图像信号的产生

由FPGA程序产生数字图像信号,即将1帧图像可以看做是一个384*625的二维数组[7],根据需要产生的图像,对二维数组进行相应设置即可产生所需的图像。考虑到手工计算二维数组,然后根据二维数组编写FPGA程序,工作量非常大。为此,我们开发了数字图像信号自动生成FPGA程序辅助软件,如图4所示。

图4 数字图像信号自动生成FPGA程序辅助软件主界面

数字图像信号自动生成FPGA程序辅助软件采用“所见即所得”的思想,采用MFC中多框架视图结构,在视图中绘制了一个384*625矩形框代表图像显示区域,设计了一系列可视化对象[8],作为软件的基本元素,可视化对象承载了所有数据信息和界面信息。考虑到VHDL本身不支持乘法运算,需要设计乘法器[9],因此在图像生成示例程序主要考虑“直线”和“方块”图像的自动生成FPGA程序,下面以产生“直线”图像为例详细介绍。首先定义了CDrawObj类完成界面拖放、序列化和设置颜色等属性的基本操作,在该类基础上继承实现了CDrawRect类用来完成“直线”图像的绘制与序列化[10]。其中序列化的实现算法如下:

步骤1:对象个数不为0,则在当前路径下创建VHDL_generate.vhd文件,成功转入步骤2,否则报错退出;

步骤2:写入VHDL文件头,主要包括使用VHDL库和变量声明等;

步骤3:根据可视化类具体类型,生成图像信号对应的FPGA代码;

步骤4:写入VHDL文件尾,主要包括图像信号输出语句和其他结构化语句。

其中生成图像信号对应的FPGA代码是核心,以“直线”图像为例,其代码生成思路是:首先确定是水平方向还是垂直方向,然后确定直线两端在可视化界面上的相对坐标,最后利用VHDL中的FOR语句生成相应代码,自动生成完整的VHDL语言代码[11]示例如下:

3.3 运动图像信号的产生

考虑到电视跟踪系统测试时需要产生标准运动图像信号,以检测电视跟踪系统是否正常工作。为此,在FPGA顶层设计中添加一个计数器模块index,并修改目标信号模块,如图5所示。

其中index模块时钟输入为晶振信号经过row和line两个模块分频后的信号,时钟周期约为40ms,其计数长度即为运动目标的长度。

target1目标模块输入受行、列和计数控制,产生一个点目标直线运动的示例代码如下:

图5 PAL制视频信号产生器的FPGA顶层设计原理图

3.4 信号合成

信号合成模块将FPGA输出的图像信号和同步信号叠加并合成,PAL制视频信号标准规定:图像信号幅度0.7V,同步脉冲幅度-0.3V,峰-峰值Vp-p=1.0V[12]。信号合成模块采用LF347单片四运放完成,其电路设计如图6所示。

图6 信号合成模块电路设计原理图

通过运放实现了图像信号和同步信号的放大与叠加,产生的图像信号符合图像采集卡自检要求。

4 结语

本文基于FPGA设计了PAL制视频信号产生器,利用FPGA产生PAL制信号所需的同步信号与图像信号,通过信号合成后可以产生静态和动态图像信号,并研究了VHDL程序的自动生成技术,开发了数字图像信号自动生成FPGA程序辅助软件实现了图像生成过程中的“所见即所得”。