FPGA配置芯片逻辑固化设备的研究与实现

2020-11-28马萌叶关山

马萌 叶关山

摘 要:本文针对传统逻辑固化方式的瓶颈,提出了配置芯片逻辑固化设备的高效方案及实现方法,并通过对比分析,采用本方案生产效率可得到显著提升。

关键词:FPGA;逻辑固化;配置芯片

中图分类号:TN79 文献标识码:A 文章编号:1671-2064(2020)12-0051-02

0引言

FPGA的使用需要将逻辑固化于存储器,按照存储器的位置Xilinx的FPGA可大致分为存储器内置和存储器外置两类。存储器内置的FPGA包括早期的95144、95288等,以及当前广泛使用的XC3S400AN、XC4VLX25等,存储器外置FPGA包括早期的XQ4010+XC17256(SM1701)、XCV600/XQV300+XQ18V04,以及当前广泛使用的XC5VFX200T/XC6VHX380T+XCF128XFT。事实上,这类外置的存储器可以称作FPGA配置芯片,逻辑即固化于这类芯片。

逻辑固化的方式一般采用JTAG接口连接。对于存储器内置的FPGA,可直接连接JTAG接口进行固化,对于存储器外置的FPGA需要根据存储芯片的特性采取不同的方式。对于18v04这类有外接JTAG接口的芯片,可直接连接JTAG;对于XCF128XFT这类没有外接JTAG接口的芯片,需要经由FPGA通过SPI/BPI的方式连接。

配置芯片的逻辑固化耗时过长已成为制约生产效率的重要问题,而JTAG接口正是造成这一问题的瓶颈。本文以广泛使用的配置芯片XCF128XFT为例,提出了配置芯片逻辑固化设备的高效方案。

1固化设备实现方案

1.1 固化设备原理

本文提出的配置芯片邏辑固化设备设计方案,采用FPGA作为主控单元,千兆以太网作为固化设备与PC机的接口,对待配置的PROM,采用16bit并行接口。

设备分为上位机软件、固化设备硬件两大部分,设备硬件又可分为固化硬件、IC测试座两部分。

1.2 FPGA单元设计

FPGA单元需要实现的功能包括以下几点:

(1)实现千兆以太网接口的初始化配置和传输控制;

(2)完成配置数据的缓存、接收和发送等任务;

(3)数据格式转换。

FPGA单元的主要元器件为FPGA及外围电路。固化设备需要高速处理配置流数据,完成千兆以太网接口的收发和PROM接口的控制,所以,高性能的FPGA是固化设备的最佳选择。

在设计时计划选择XILINX公司的28nm高性能低功耗的Kintex-7系列FPGA XC7K160T-2FBG676I作为系统的控制芯片。该系列FPGA设计在高端性能的基础上实现了最低的功耗,可提供高密度逻辑、高性能收发器、存储器、DSP以及混合信号,通过这些功能可以提高系统级性能,并可以更紧密地进行集成,非常适合本方案中高速数据的处理任务[1]。

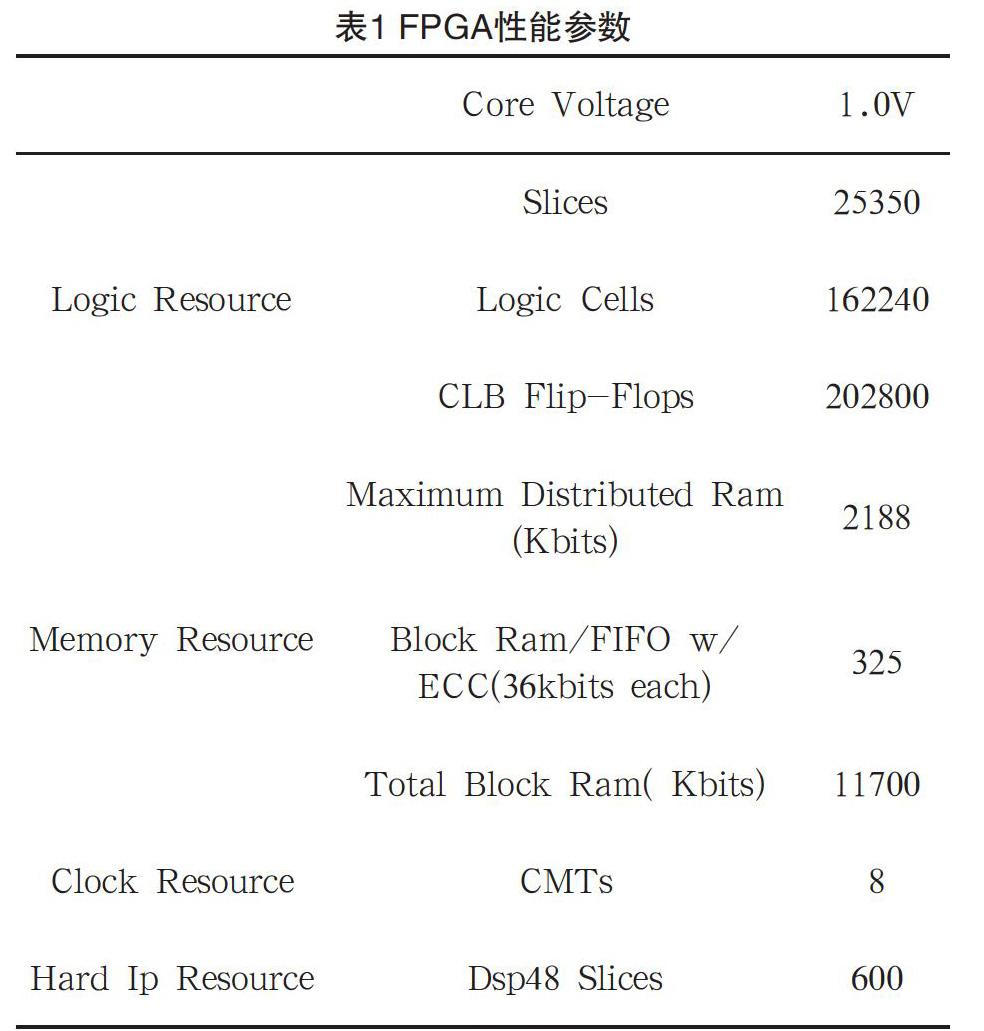

XC7K160T-2FBG676I的主要参数如表1所示。

1.3 固化设备与PC机千兆网接口设计

传统方法中,配置数据传输的一个瓶颈主要在于串行的JTAG接口,因此,为了从根本上提高系统数据传输速率,达到PROM芯片800Mpbs的最大工作带宽,固化设备与PC机接口采用千兆以太网实现。

千兆以太网理论速度能够达到1000Mbps,实际应用中,有效数据的吞吐率完全可以达到800Mbps,很好地解决数据的传输瓶颈问题。

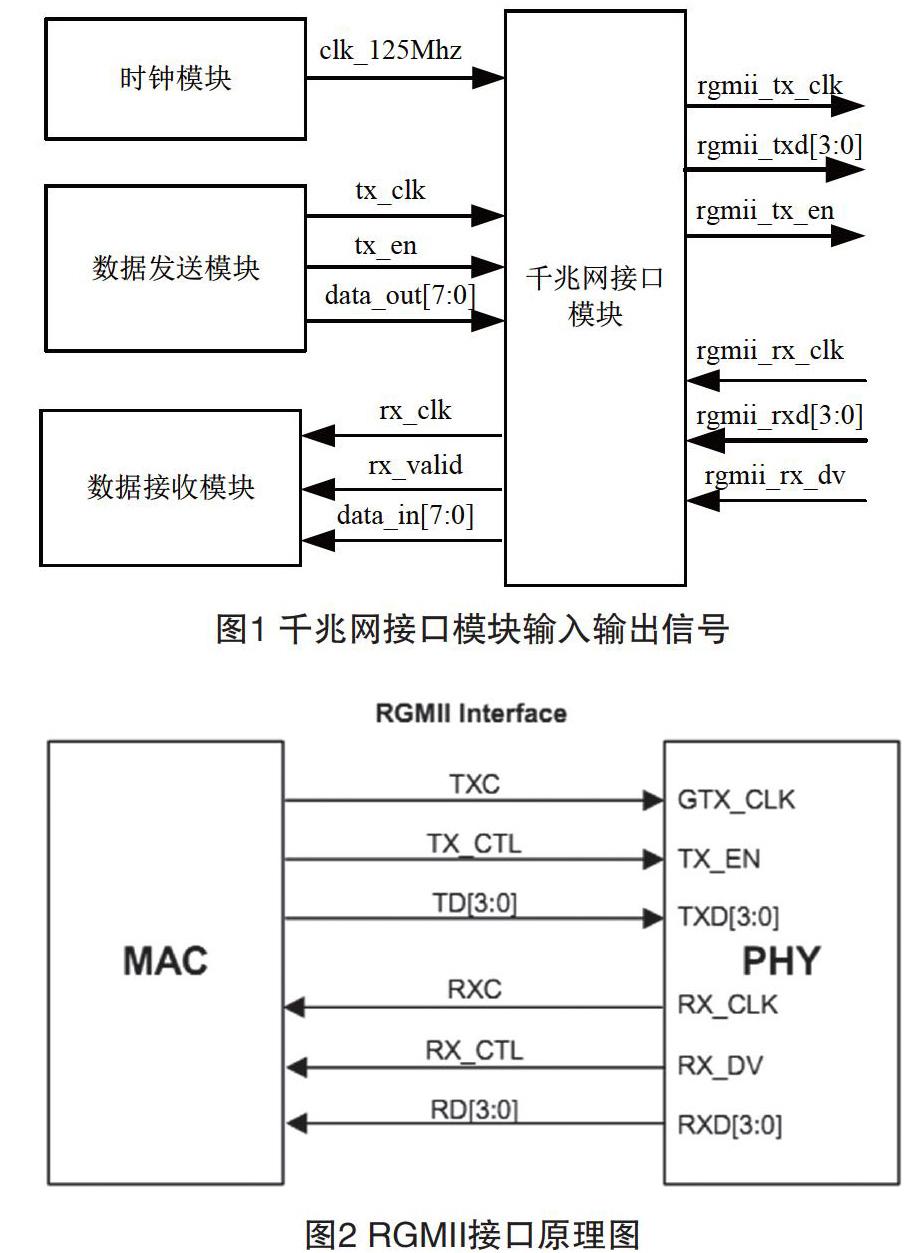

本方案中,千兆网接口模块主要采用PHY芯片88E1111与FPGA直接相连,通过上电时FPGA对88E1111进行配置,使其工作在RGMII模式。FPGA按照RGMII协议,产生数据发送时88E1111所需要的输入信号,同时接收88E1111接收到的数据[2]。

PHY芯片88E1111工作在RGMII模式时所需要的输入信号有发送时钟、使能和数据。千兆网接口模块的输入输出信号如图1所示。

在程序的设计上,需要对输入的8bit并行数据先送入FIFO进行缓存,千兆网模块在输出时,先输出帧头,接下来是目的地址、源地址、接着在时钟的上升沿输出数据的低4位,下降沿输出数据的高4位,每一帧输出的数据长度可由程序中的参数决定,最后输出奇偶校验位。

方案中采用FPGA实现MAC层协议,可以大大提高系统的集成度和可靠性,具体的RGMII接口原理图见图2所示。

1.4系统电源设计

固化设备输入电压采用常用的12V供电,各个单元需要的电压包括:FPGA接口电压3.3V,核心电压1.0V;以太网接口芯片接口电压3.3V,核心电压1.2V;PROM接口电压3.3V,核心电压1.8V。

针对这些电压,采用凌特公司的四输出芯片LTM4644实现。该芯片输入电压范围为4V~14V,适应范围较宽;有4路相同技术参数的输出通道,输出电压范围为0.6V~5.5V,每路的工作电流可支持4A,完全满足设计需求。

2性能分析与对比

首先,由于离线的方式对PROM进行烧写,固化设备专门用于烧写PROM,I/O资源没有太大的限制,因此,可以采用并行烧写的方式。而产品中可以根据具体情况采用并行或串行的方式,在上电的时候,进行配置数据的加载。

其次,采用千兆以太网接口传输PC机上的配置数据,千兆以太网理论速度能够达到1000Mbps,实际应用中,有效数据的吞吐率完全可以达到800Mbps。FPGA通过千兆以太网接口接收到这些数据后,将配置数据以并行的方式写入PROM,并行读写的工作频率为50MHz,保证了FPGA与PROM之间接口的带宽为800Mpbs,与千兆以太网接口速度相近[3],表2为本方案与传统方案中,各接口与系统性能的对比。

本方案的设计保证了整个固化器的带宽与PROM的最大带宽相符,使系统不存在其它的瓶颈,相比于传统的通过JTAG接口传输数据的方式,极大地提高了系统速度和烧写效率。

由分析结果可见,本方案相比于在线的方式,效率提高了大约80倍。相比于现有的烧写器,单套的效率也提高3倍。在较大批量的生产任务中,本方案固化设备所带来的生产效率提升的效果会更加明显。如果采用组网多台固化设备同时烧写的方式,更能够成倍提高生产效率。

3结语

针对传统逻辑固化方式的瓶颈,提出的FPGA配置芯片逻辑固化设备的方案,较之传统方式,具有高效率、高可靠、可扩展的显著优势,可大大提升逻辑固化水平。

参考文献

[1] 任程.DSP+FPGA平台功耗管理的研究与实现[D].哈尔滨:哈尔滨工业大学,2016.

[2] 杨青山.基于FPGA的千兆以太网接口应用研究与实现[J].无线互联科技,2018(8):37-38+43.

[3] 石雪梅,计贤春.FPGA配置芯片测试方法的研究与实现[J].计算机与数字工程,2010(9):77-79+87.