一种幅度调制下的成型滤波器实现方法

2020-07-23于茫

于茫

摘 要:针对通信系统成型滤波器实现过程中逻辑资源紧张的问题,提出了一种正弦曲线模板方法。利用该方法可以解决FPGA中占用大量LUT和DSP资源的问题,减少有效地址位数,提高寻址速度。该方法利用并行及流水线处理方式,提升了运算速度。最后通过仿真及频谱仪测试,占用带宽完全满足国家标准。

关键词:正弦曲线;成型滤波器;FPGA;MATLAB;仿真;ModelSim

中图分类号:TP39文献标识码:A文章编号:2095-1302(2020)07-00-02

0 引 言

通信系统中信源输出的信号会经过基带处理、DAC器件、放大器、调制器、滤波器、衰减器、功率放大器……,最后到达天线负载输出给信宿。基带处理过程包括MAC层编码、数据链路层编码、调制编码、滤波器设计等。而信源采用滤波器设计用以限制发送信号的带宽,降低带外干扰及带内的码间干扰[1]。

成型滤波器在FPGA有多种实现方案。

方案一:利用FIR算法,通过MATLAB中的滤波器仿真选取满足系统要求的滤波器系数,然后把该组系数写入FPGA中的FIR IP核内并仿真及验证[2]。

方案二:为了节省逻辑资源,把MATLAB中仿真满足系统要求而生成的FIR系数归一化后存入ROM,按照分布式算法,对查找表进行切割处理,累加乘运算得到最终结果[3-4]。

方案三:CIC插值滤波器中只有加法器,无乘法单元,因此进行上变频处理,满足DVB-S系统要求[5]。

方案一的实现过程简单明了,但逻辑的资源消耗最大,且要求FPGA器件具有大量DSP和LUT资源,支持FIR的IP;方案二相比方案一省却了资源,但在实现过程中需要考虑参数归一化的字长位数,每级乘法中需要考虑尾数截取的范围,同时对ROM的存储深度和存储字长也有要求;方案三中信号字长位宽的增加会对级联的加法器性能产生一定限制。随着滤波器阶数的增加,三种方案对逻辑资源的消耗将呈几何级增加。

本文针对无线通信的幅度调制提出了一种新的成型滤波器设计方法,首先把正弦曲线模板生成的参数存入ROM,然后把调制编码完成的信号与ROM表中的曲线参数进行累加乘运算,最终输出波形。该法不仅限制了带外干扰,节省了资源,而且占用带宽满足国家标准[6]。

1 正弦模板算法

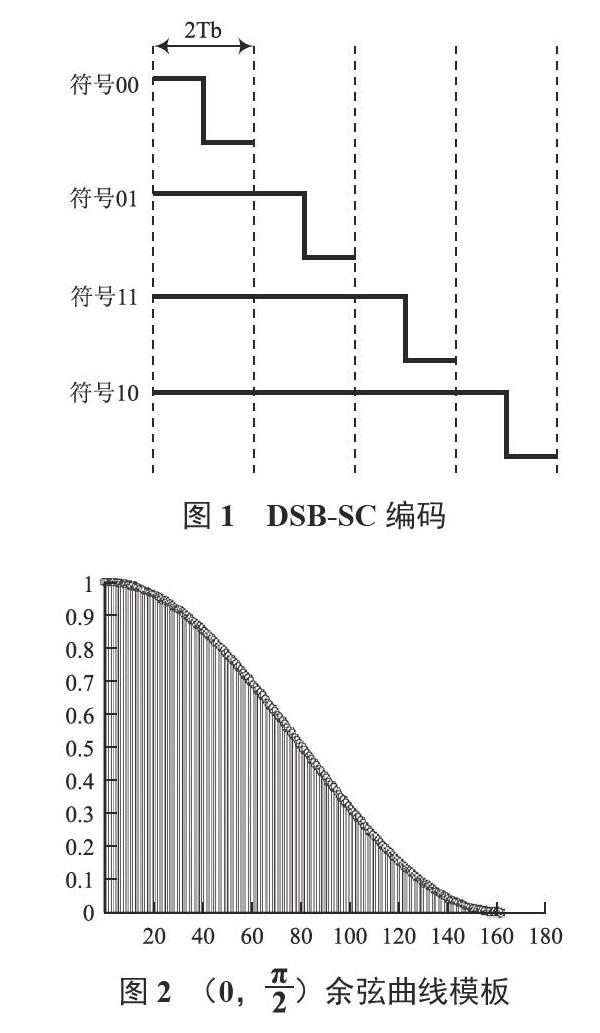

本文所阐述基带处理系统FPGA的采样频率Fs为26 MHz,先对Fb进行TPP编码(见图1),Tb=6.25 μs,然后进行DSB调制编码[6],最后经成型滤波器输出给14 bit的DAC器件。具体实施步骤如下。

(1)选取标准正弦函数y=cos(t),t取(0,),y值用来表示信号的变化沿。计算Fb信号一个码元持续时间内所需要的采样点的个数N=Fs/Fb=162,构造y(n)=acos(2πxn)+b,已知y(0)=1,y(162)=0,a=b。求出y(n)=0.5cos((2πn)/324)+0.5,保留(0,162)区间的y值(图2)。

把从MATLAB获取的y(n)值按照16 bit量化取整,处理后的数据写入FPGA的ROM。

(2)对输出信号s(t)进行调制编码,字长宽度与DAC器件保持一致,采用14 bit。码元1取十进制数4095,二进数补码为00_1111_1111_1111,码元0取十进制数低电平值是-4 096,二进数补码为11_0000_0000_0000。

(3)检测到s(t)的沿变化(上升沿和下降沿),s(t)延迟两拍输出s(t)_2d,比较s(t)和s(t)_2d数值,当数值不同时找到s(t)的变化沿后启动查找表。找到s(t)的变化沿后把s(t)当前值赋值给s_data_A寄存器,当前值对应的相反电平值赋给s_data_B寄存器。模块中信号设置均采用16 bit字长,对小于16 bit的寄存器宽度,符号位进行扩展。计算出来的s_data_A与s_data_B的值赋值给s_data_AsubB寄存器。

(4)启动查找表,每个采样时钟ROM地址加1直到N,但在s(t)的变化沿重新为ROM地址置0。每次从ROM读取出来的数q乘以s_data_AsubB,结果为S_data_dsb_out。调制编码码元0按照-4 095取值,所以计算结果S_data_dsb_out需整体向上偏移4 096。

2 仿真及验证

利用ModelSim对方法进行仿真验证,成型滤波前后的数据如图3所示。使用频谱仪进行占用带宽测试,如图4所示。不进行滤波处理的信号占用带宽约1.6 MHz,将严重影响其他信道的设备工作,而滤波后信号的占用带宽[6]小于标准要求的250 kHz。

3 结 语

本文使用一种正弦模板算法实现成型滤波器的设计,并给出了ModelSim的仿真结果及频谱仪测试的占用带宽,验证了该算法设计的正确性和可行性。采用该方法可以很好地设计无线通信系统中要求的成型滤波器。

参考文献

[1]樊昌信,曹丽娜.通信原理[M].7版.北京:国防工业出版社,2012.

[2]郭勇,杨欢.基于IP核FIR滤波器的设计与FPGA实现[J].无线电工程,2017(1):79-82.

[3]洪炳镕,趙林.利用系数函数ROM查找表设计的数字滤波器硬件[J].军事通信技术,1987(4):55-60.

[4]吴凤辉,迟永刚,郑宇希,等.一种改进DA算法的成型滤波器设计[J].哈尔滨工业大学学报,2016(5):32-35.

[5]张文坡,常亮,史丽荣.DVB-S中可变插值率CIC滤波器设计及其FPGA实现[J].现代电子技术,2018,41(11):103-104.

[6]中国国家标准化委员会.GB/T 29768-2013,信息技术 射频识别 800/900 MHz 空中接口协议[S].2013.

[7]张龚,谢文博.基于DSP Builder的FIR滤波器设计[J].物联网技术,2016,6(5):33-35.

[8]文明.基于FPGA的高速并行滤波器设计与实现[J].现代导航,2018(5):382-386.

[9]邵浩,何忠秋.减少脉冲成形滤波器系数个数的高效算法[J].应用科技,2014(6):35-40.

[10]龚业勇.高清晰度电视VSB调制器及频谱成形滤波器的设计[D].北京:北京大学,1998.