基于Proteus的80X86 外部中断电路的设计与仿真

2020-06-18符晓玲

王 超, 符晓玲, 李 斌

(昌吉学院物理系,新疆昌吉831100)

0 引 言

中断技术是微机原理课程中非常重要内容,其应用可大大提高CPU的效率,Intel 80X86 系列微机有一个灵活的中断系统,可以处理256 种中断源,每个中断源又对应一定的中断类型号供CPU识别[1-3]。中断分为外部中断和内部中断两种,外部中断主要由外部设备的请求引起,具有随机性,内部中断有指令执行引起,无随机性。由于外部中断执行的随机性,造成中断执行过程的突发事件比较多,比如:无法进入中断、中断返回“跑飞”、中断嵌套无法完成等。本文利用Proteus设计了80X86 中断电路,并进行了详细的测试分析,可将抽象的中断过程直观化地展现了出来。

1 80X86 中断电路的设计

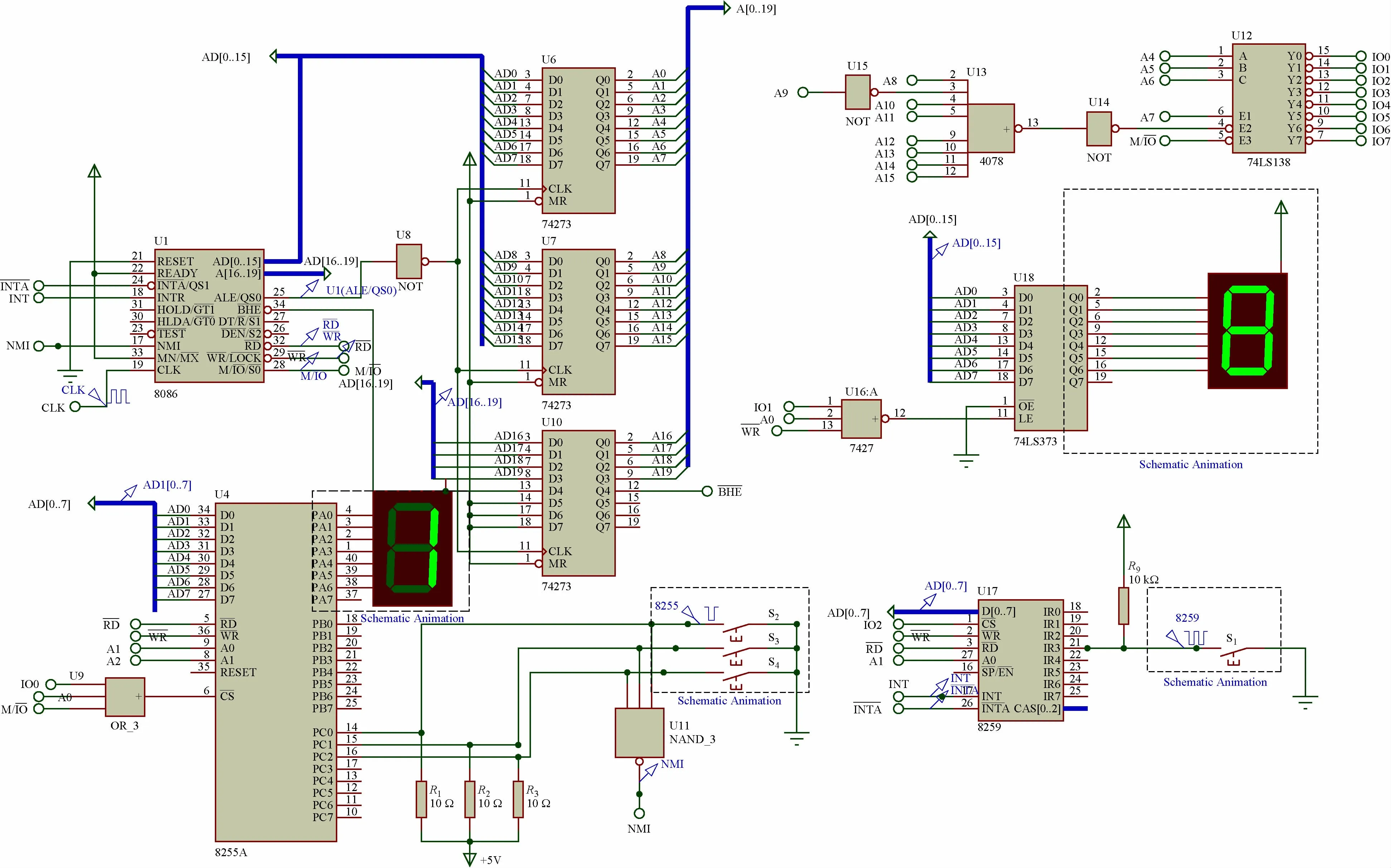

80X86 中断电路由8086CPU、数据/地址复用电路、片选电路、可屏蔽中断请求(Interrupt Request,INTR)按键请求及显示电路和非屏蔽中断请求(Non Maskable Interrupt,NMI)按键请求及显示电路组成[4-6],主要完成INTR、NMI 的中断请求及处理,以及它们之间中断嵌套功能的实现,如图1 所示。

图1 80X86中断电路设计图

数据/地址复用电路由3 片74LS273 锁存器组成,数据线用AD[0…15]表示,地址线用A[0…19]表示,用来在不同时刻分时使用总线;片选电路由4078 或非门和74LS138 译码器组成,可根据需要配置任意地址范围的片选信号;INTR 按键请求及显示电路由8259控制器、74LS373 驱动器等组成,用来对按键S1通断的输入信号进行识别并以0 ~9 递增的顺序在数码管上显示;NMI按键请求及显示电路由8255 可编程并行接口芯片、模拟中断请求按键等组成,用来对按键S2-S4的输入信号进行识别并显示在数码管上,通过8255可扩展了多个I/O口,根据需要外接多种I/O设备。

2 程序设计

根据图1 要实现的功能,完成主程序和中断服务程序的编写。主程序完成初始化8255、8259 等任务,之后循环等待外部中断的发生,当有可屏蔽中断请求时,执行加1 操作,当有非屏蔽中断请求时显示对应的按键值,中断服务结束后返回主程序(见图2)。

图2 软件流程图

3 中断电路的调试

Proteus的虚拟仿真模式(Virtual Simulation Mode,VSM)包括交互式的动态仿真和基于仿真图表的静态仿真两种,交互式动态仿真可在线实时观察电路的仿真结果,仿真结果在运行结束后立即消失,基于图表的仿真结果可随时刷新,以图表的形式驻留在图中,可供线下进行分析。为了精确分析中断的执行过程,采用仿真图表方式来观察,在原理图中分别添加CLK、M/和READY 等探针,并在仿真图表中添加相应的量。

3.1 非屏蔽中断

非屏蔽中断由CPU 的NMI 引脚出现上升沿触发时向CPU提出中断请求,不受IF的影响,也不能由软件加以屏蔽[7-8],要想通过仿真图表观察NMI 请求的过程,是不能和电路进行交互操作的,因此可以考虑在按键处加入一个等效的信号,使用虚拟仿真工具中的激励源来完成,如图3 所示。

图3 单脉冲激励源

图3 中,添加了一个单脉冲激励源,在60 ms时刻添加一宽度为50 μs 的脉冲,脉冲属性为高、低、高的脉冲,用来模拟按键的通断情况,并在上升沿触发NMI的中断请求。8086CPU 在当前指令执行完成后,立即无条件给予响应,中断类型号为2,CPU 响应后,在ALE的下降沿把出现在AD[0…15]上的地址信号0284H(8255 C口地址)进行锁存,在下一个T状态有效时读取总线AD[0…7]上的数据0FEH,如图4所示。

图4 NMI中断响应读时序

在经过若干个空闲周期Ti后,将要进行总线写周期,在T1 状态ALE 下降沿有效时,将出现在总线AD[0…15]上的数据0280H进行锁存,下一个T状态,在有效时将计算得到的按键显示码0F9H 通过总线AD[0…7]写入到8255 的A口,立即显示对应按键代码为“1”,如图5 所示。

图5 NMI中断响应写时序

3.2 可屏蔽中断

(1)CPU 访问外设读时序图。可屏蔽中断请求信号通过INTR引脚送给CPU,在中断允许标志IF =1时,CPU在结束当前指令周期后响应中断请求[9-11],中断过程如图6 所示,在T1 状为低电平,表示CPU访问的是外设8259A,多路复用总线上发出地址信息,A[16…19]不用,保持为低电平,AD[0-15]=02A2H,指示出要寻址的外设端口的地址,在ALE 信号的下降沿74LS273 锁存器对地址进行锁存;在T2 状态,A[16…19]=0010B,代表CPU 的状态信号线,分别表示8086CPU与总线相连、IF =0(中断禁止)和正在使用的为CS段寄存器,AD[0 ~15]前期浮空,后期有有效,0060H 出现在数据总线上,该值为8259A的初始化字ICW2 =0110 0000 B,其功能为设置中断类型号的高5 位;在T3 状态,A[16…19]继续提供状态信息,AD[0-15]为CPU 写的数据0060H,CPU在T3 状态的下降沿采样READY信号,因该信号为高电平,表示外设8259A 已经做好接收准备,无需插入TW等待周期,直接进入T4 状态,在T4 状态和T3状态交界处,完成数据的写入操作,总线周期结束,当CPU不执行总线周期时,系统总线就处于空闲状态,执行空闲周期Ti,在这期间,A[16…19]仍然驱动上一个总线周期的状态信息,其值为0010B,AD[0…15]处于高阻状态。

图6 CPU访问外设读时序图

(2)CPU 响应可屏蔽中断时序图。当发出中断请求后,8086CPU在现行指令执行完成之后将进行响应,如图7 所示,中断响应周期有2 个,每个响应周期由4 个T状态组成,在两有效之间,插入了3个空闲周期Ti,以等待外设提供中断类型号,每个中断响应周期CPU都会引脚发出1 个负脉冲,在第1 个响应周期AD[0…7]一直处于浮空状态,在T1状态,ALE下降沿输出地址锁存信号,A[16…19]为低电平,在T2-T3 状态,A[16…19]=0110B,其含义为IF =1 表示允许中断、CPU正在访问CS段寄存器。在第2 个响应周期,T1 状态,ALE下降沿再次有效1 次,外设8259A在收后,立即将中断类型号63H送往数据总线的低8 bit AD[0…7]上,中断请求信号INT一直维持到结束后终止。

图7 可屏蔽中断响应时序图

(3)设置硬件断点和调试弹出窗口。为了提高调试效率,以便当硬件条件发生时单步执行观察代码下一步的执行情况,可以设置硬件断点来完成,例如:想观察非屏蔽中断时入口地址是否正确,可以将中断请求信号INT作为硬件断点设置点,从模式选择器中选择电压探针,单击后放置到INT 引脚上,双击选择属性,如图8 所示,在实时断点类型选择“数字的”,即INT引脚低电平触发,输入“0”作为触发值,装备时间选择“1”,当INT引脚由高电平“1”变化到低电平“0”时进行捕获,观察中断向量表中的内容。

图8 硬件断点设置图

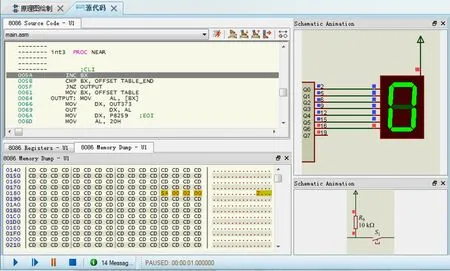

为方便观察原理图中某一小部分的变化情况,又不希望经常在原理图和VSM Studio 中来回切换,需要对调试弹出窗口进行设置,例如:想观察当S1按键按下时可屏蔽中断运行结果显示情况,可切换到ISIS 选项卡,选择“调试弹出模式”,在原理图中框选需要在VSM Studio 页面中显示的部分,这里框选了可屏蔽中断显示器、按键S1即可。按下仿真运行按钮,切换到VSM Studio选项卡,在IDE 的右边显示了刚才选择的部分原理图,如图9 所示。

图9 中,按下S1按钮,在硬件断点INT控制下,程序立即暂停至可屏蔽中断int3 PROC NEAR 处,单击调试/8086/Memory Dump,即可打开存储器窗口[12-16],通过图7 可知,8259A 的IR3 可屏蔽中断类型号为63H,乘以4 可以求得中断向量表的地址为18CH,通过存储器窗口可以观察到在18CH 地址内的内容为5A 00 02 00,即IP =005AH,CS =0002H,与代码段中可屏蔽中断服务程序int3 的入口地址一致。

图9 可屏蔽中断运行图

3.3 中断嵌套过程

依据x86 所规定的NMI 中断请求的优先级高于INTR中断请求,为用仿真图表观察中断的嵌套过程,在S1按键处放置一个连续时钟激励源,类型为高、低、高,周期为500 μs,即:每隔500 μs 向8259 发出中断请求,在数码管上循环递增显示0 ~9,用来指示进、出INTR中断的过程。INTR中断运行期间,在按键S2置一单脉冲激励源信号,脉冲属性为高、低、高,脉冲宽度为20 μs,开始时刻加在1 ms处,用来模拟NMI请求,通过仿真图表,观察中断嵌套过程,如图10 所示。

图10 中断嵌套处理过程

将图10 中断嵌套时序分成4 部分,详细分析如下所示:

(1)此波形对应的是8086 对8255、8259 等初始化操作过程。如图11,图中数据与程序中初始化数据一致。

图11 初始化操作时序图

(2)当激励源8259 有正跳变时,产生INTR 中断请求。体现在ALE两次有效有效,通过放大/缩小等工具发现该处中断类型号为63H,如图12。可屏蔽中断电路数码管接收到的字型码为“F9”转化为显示字符“1”。

图12 INTR中断请求

(3)对应的是在INTR 请求时,激励源8255 有负跳变,产生NMI中断请求。因NMI的中断优先级高于INTR信号,所以暂停INTR 过程转去执行NMI 中断,体现在INTR中断请求延长,ALE 两次有效,NMI数码管显示“1”。NMI 执行结束后,继续响应INTR 中断,有效,ALE两次有效,此处中断类型码仍是63H,可屏蔽中断电路数码管显示为数字“2”,如图13所示。

图13 中断嵌套

(4)对应的是INTR中断请求及响应过程,与第2部分过程类似,INTR 数码管显示“2”,运行过程如图14 所示。

图14 运行过程图

在仿真运行时,也可以通过示波器观察到中断嵌套情况,如图15 所示,当不可屏蔽中断与可屏蔽中断同时发生时,首先执行不可屏蔽中断,当其执行完成后,执行可屏蔽中断请求。

图15 示波器观察中断嵌套时序图

4 结 语

使用Proteus软件的多种功能对X86 系列微机的中断电路进行了设计、和仿真、分析,用Proteus仿真工具中的激励源,实现了交互式动态仿真向基于图表的静态仿真的转换,有利于对中断突发事件过程的精确分析,有助于快速发现存在的问题,提高解决问题的能力。