纳米级超大规模集成电路芯片低功耗物理设计分析

2020-05-27张博文

张博文

(运城学院,山西 运城 044000)

1 纳米级超大规模集成电路芯片功耗构成

动态功耗可分为P 沟道MOS 晶体管、N 沟道MOS晶体管同一时间导通形成的短路电流引起的功耗以及电容器充电和放电引起的功耗。静态功耗包括扩散区、衬底形成的反向偏置二极管的漏电流、通过栅氧的电流引起的功耗。由于泄漏电流大小和温度有关,因此芯片温度升高时,漏电流引发的静态功耗急剧增加,而且泄漏电流与晶体管大小成反比。动态功耗受开关频率、负载、电源电压影响,芯片电压越高,功耗越大。因此,要优先选择可在低电压运行的芯片,以降低整体功耗。本文主要针对超大规模集成电路功耗优化设计进行研究[1]。

2 纳米级超大规模集成电路芯片低功耗物理设计方法

2.1 工艺层面的芯片低功耗物理设计

工艺层面的芯片低功耗物理设计基本思路是通过改进工艺、优化电子元件布局及缩小低电子元件大小等方式实现低功耗设计目标。目前,集成电路制造工艺已经迈入7 nm 级,电路集成度急速增加,单位面积芯片中集成的晶体管数量达千亿级,导致芯片功耗快速增长。晶体管特征尺寸与其漏电流引发的静态功耗成反比。为了降低静态功耗,可利用包括多种阈值电压的单元库,尽量用阈值更高的元件,以提高阈值电压,降低功耗。此外,还可以改进工艺,根据CMOS 晶体管的衬底偏置效应适当提高晶体管阈值电压,减少漏电流,从而降低静态功耗。例如,采用立体鳍状栅结构增强元件开关特性,使元件关闭时漏电流显著降低,还可以用高介电常数材料替换二氧化硅、多晶硅栅极,以减少栅极中寄生电容[2-3]。

2.2 电路结构上的芯片低功耗物理设计

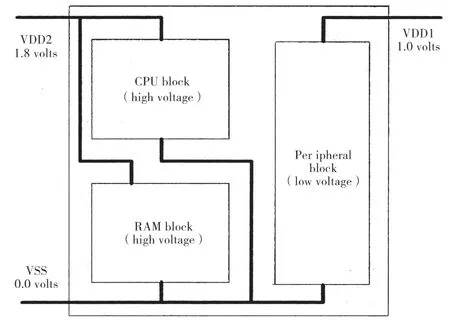

通过优化电路结构、电路实现途径的方式来实现低功耗设计目的。供电电压越高,动态功耗越大,即便是很小的电压变化都能显著降低功耗。基于此,在电路结构方面的低功耗设计中,降低供电电压是一种基本思路。例如,供电电压降低0.6 V 时,动态功耗会降低40%左右。而芯片模块的供电电压可能存在差异。图1 为多供电电压设计。

图1 多供电电压设计

图1 中处理器CPU、主存RAM 模块运行速度要尽量快,但外部接口的运行速度要求不高。模块运行速度和供电电压成正比,为了在速度与低功耗之间找到平衡,CPU、RAM 模块的供电电压VDD2为1.8 V,外部接口模块的供电电压VDD1为1.0 V。这属于多供电电压低功耗设计方案,芯片性能要求不同,适用于芯片的多供电电压低功耗设计方案也存在差异。

2.3 门级层面的芯片低功耗物理设计

2.3.1 单元映射

在逻辑门层面描述电路时应使用逻辑门单元。执行门级综合时如为手动输入,则综合器将从合成库中选择逻辑门模块。大多数工艺提供商会提供低功耗单元库。选择这样的单元库可以降低功耗,这是使用单元格映射的基本思路。此外,活跃度高的节点要尽量置于逻辑单元中,以降低其负载电容,从而降低功耗。最常见的设计思路就是增加电路的输入门,如三输入门,以减少逻辑门数量并缩短总线长度,达到降低功耗的目的。

2.3.2 公因子提取

提取公因子以精简逻辑网络,降低电路结构复杂程度,从而降低功耗。例如,设计者可通过多种逻辑结构实现同一个函数,虽然在面积、时间方面不同逻辑结构的差异不大,但输入信号反相频率存在差异,导致电路功耗存在较大差异。因此,在设计电路时,由高速旋转信号控制的负载应尽可能小,即这些信号应更靠近输出,即元件越小越好。在设计电路时,有必要弄清每个信号的活跃度,然后根据每个信号的活动性提取公因子,并合理地对每个信号在电路中的位置进行排序。

2.3.3 门尺寸优化

通过缩减路径非关键网关尺寸,实现低功耗设计目标。在电路性能不受限制的情况下,可缩小全部电路中所有逻辑门的尺寸,将门尺寸优化转为延迟限制下的功耗最低优化问题。首先可以根据路径对时间约束进行线性化,再求解线性方程获得全局最优解。由于采用了低带宽的模块,电平转换速度减慢,从而导致短路电流增加,这是优化门尺寸的一个限制因素。对于给定时间范围内优化离散快门大小变化功率问题,其基本思想是从最小的门开始逐步增加关键路径。大小以满足限制并最小化通道切换活动。

2.4 系统层面的芯片低功耗物理设计

2.4.1 软硬件划分

软硬件划分是指将电路系统分为软件、硬件两部分。目前,很多知名电子设计自动化EDA 公司已相继发布了系统层面的电路设计软件,能够实现电路系统层面软硬件划分,被行业广泛应用。例如,Synopsys 公司的CoCentric 可以同时设计、仿真、实现多个系统核心元器件,Cadence 推出的Virtual Component Co-design可以定义、分析、优化系统层面的电路设计,给电路设计者提供了系统集成、验证所需技术和工具,图形化界面方便设计人员进行协同设计和验证。利用这些软件设计人员可以从系统层面对软件、硬件两个角度综合考虑,确定最佳设计方案。

2.4.2 功耗管理

功耗管理包括动态、静态两种管理方式。动态功耗管理是指根据实际情况控制空闲模块关闭,以减少功耗。静态功耗管理的对象是电路工作模式。如果系统空闲,则停止芯片工作,休眠系统,从而减少功耗。动态功耗管理实现需要操作系统,因此其应用受到限制。

2.4.3 指令优化

指令优化流程包括如下4 步。

(1)提取指令集。合理选用指令集可以让系统功耗降至最低。

(2)合理选择指令长度,提高程序代码密度,从而降低对存储器的访问,降低功耗。

(3)优化指令编码,减少指令读取时总线信号翻转,以降低功耗。

(4)压缩指令,指令在内存中进行压缩,输入CPU 之前再解压可以降低CPU 功耗。

3 基于Golden UPF 的低功耗物理设计流程

Golden UPF 主要有便于追踪、无需修改UPF 文件及设计效率高等优点。因此,本次研究基于Golden UPF(Unified Power Format)进行低功耗物理设计,在满足电路性能需求的情况下实现低功耗设计目标,设计基本流程如图2 所示。

图2 基于Golden UPF 的低功耗物理设计流程

在开始设计前要准备好相应资料,主要包括如下3 个。

(1)网表。使用逻辑综合工具,将设计好的RTL代码转换为基于特定工艺库的逻辑门级网表。

(2)SDC 文件。用Tcl 语言编写用于表述设计目标的一种文件,如面积、时序、功耗等方面的设计目标。目前,电路低功耗设计多采用多重边角多重模式(MCMM)需多个SDC 文件来确保设计正确。

(3)UPF 文件。Unified Power Format 文件对电路低功耗物理设计思路进行了规定,用于设计的全过程。

准备好这些资料之后,通过低功耗物理设计将网表转换成GDS2 格式版图文件,经多次ECO 修复时序违例后,在MVtool 中检查低功耗器件插入正确性。再抽取版图RC 参数,使用功耗分析软件读取ICC 输出的门级网表、对应UPF 对电路功耗进行计算。

4 结论

本文简要介绍了电路功耗的构成,分别从工艺、电路、门、系统四个层面研究了低功耗物理设计方法,但是低功耗设计领域还有很多待解决的问题,因此还有待进一步研究,以不断降低芯片功耗。