基于FPGA的X射线荧光光谱仪数据采集与控制系统的设计

2020-04-21宋春苗周超胡学强

宋春苗 周超 胡学强

摘要:为提高X荧光光谱仪的准确性和测试灵敏度,本文基于FPGA设计了一套数据采集与控制系统,实现对X荧光光谱仪各个部件系统的控制,以及对探测系统输出的信号及仪器所需的环境变量的实时采集,最终实现对被测样品中元素种类及含量的分析。

关键词:X荧光光谱仪;FPGA;数据采集与控制系统;被测样品;分析

中圖分类号:TH741;TH842 文献标识码:A 文章编号:1007-9416(2020)01-0137-03

X射线荧光光谱仪是通过对样品中不同元素中产生的荧光X射线能量(或波长)和强度进行分析,以获得样品中的元素种类与含量信息,达到定性和定量分析的目的。目前,X射线荧光光谱仪在地质、冶金、材料、环境、工业等无机分析领域中应用广泛,尤其是在无损分析和原位分析方面,X射线荧光光谱仪具有无可替代的地位。

X射线荧光光谱仪由样品交换系统、X射线发生系统、分光系统、探测系统、数据采集系统组成。其中样品交换系统将样品移动到测样位置、X射线发生系统产生X射线激发样品产生X射线荧光、分光系统将激发产生的X射线荧光筛选为待测元素的特征X射线荧光、探测系统将待测元素的特征X射线荧光的能量和强度转变为电信号、数据采集系统对探测系统输出的电信号及仪器所需的环境变量(流量、温度、真空)进行实时采集上传。数据采集与控制系统是X射线荧光光谱仪的关键部件,对仪器的测试准确性和测试灵敏度起着至关重要的作用。本文基于FPGA设计了一套适用于X射线荧光光谱仪的数据采集与控制系统,实现对样品交换系统、X射线发生系统、分光系统、探测系统各部件节点的控制,同时对各元素特征X射线荧光的能量和强度进行实时采集处理及上传,最终实现对被测样品中元素种类及含量的分析。

1 系统的总体结构分析

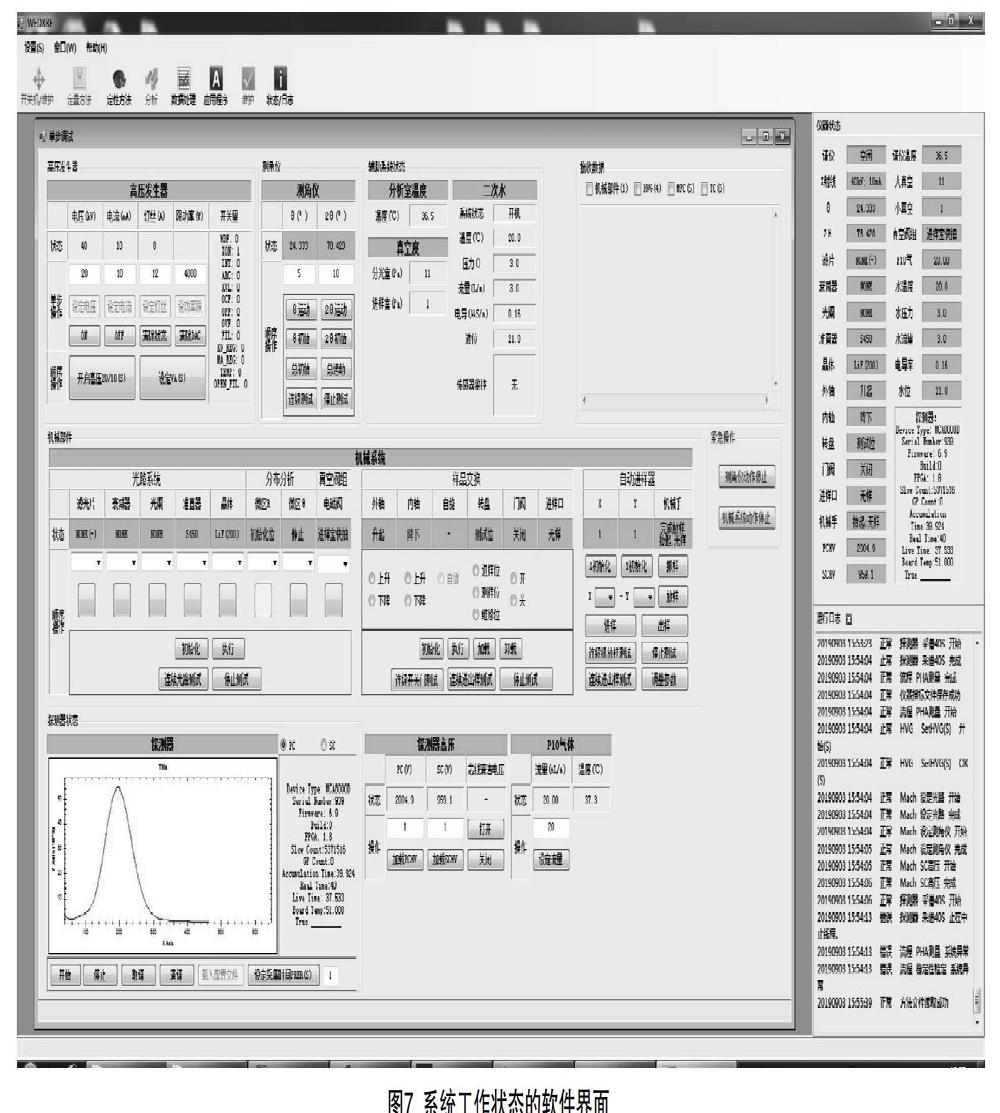

本文所设计的X射线荧光光谱仪数据采集与控制系统以网络通讯的方式与上位机进行交互,控制样品交换系统将样品移动到测样位置,然后控制X射线发生系统产生X射线来激发样品产生X射线荧光,同时控制分光系统对X射线荧光进行筛选,控制探测系统对筛选得到的特征X射线荧光进行光电转换,采集流量、温度、真空的实时状态以及探测系统输出的脉冲信号,最终以网络通讯的方式传输到上位机进行实时显示及分析,实现X射线荧光光谱仪对被测样品元素种类和含量分析的功能。

本系统由通讯单元、控制单元及数据采集单元三大部分组成,其中通讯单元负责和上位机之间的信息传递,以及与X射线发生系统、温控系统、流量系统之间的状态交互;控制单元实现对样品交换系统、X射线发生系统、分光系统、探测系统的实时控制;数据采集单元对探测系统输出的有用信号及仪器所需的环境变量(流量、温度、真空)进行实时采集。系统的总体结构如图1所示。

2 硬件电路的设计

本系统采用FPGA作为主控制器构成控制单元,W5300与MAX3232配合构成通讯单元,数据采集单元采用AD公司的A/D转换芯片实现对所需信号及状态的采集。

2.1 通讯单元

系统的通讯单元包括网络通讯和串口通讯两部分,网络通讯实现FPGA与上位机之间的信号传输,采用博控的W5300作为网络通讯芯片该芯片内部集成10M/100M以太网控制器,MAC和TCP/IP协议栈,采用总线接口与控制器通讯,可以简单快捷的实现高性能网络数据传输,W5300芯片与FPGA采用并口连接,25M外部晶振时钟信号通过W5300的内部锁相环倍频到150M作为W5300的内核工作时钟。串口通讯实现FPGA与X射线发生系统、温控系统、流量系统之间的信息交互,这里采用3片MAX3232实现,MAX3232芯片可实现TTL电平与RS232电平之间的双向转换。

2.2 控制单元

系统的控制单元由Altera公司的CycloneⅢ系列的FPGA芯片EP3C16F484实现,该芯片具有丰富的可配置逻辑单元(CLB)以及可编程输入输出单元(IOB),可以实现X射线荧光光谱仪的各个部件系统的高速并行数字化控制,其硬件配置电路图如图3所示,采用JTAG的方式加载硬件程序,设置FPGA的MSEL0、MSEL2、MSEL3管脚为低电平,MSEL1管脚为高电平。

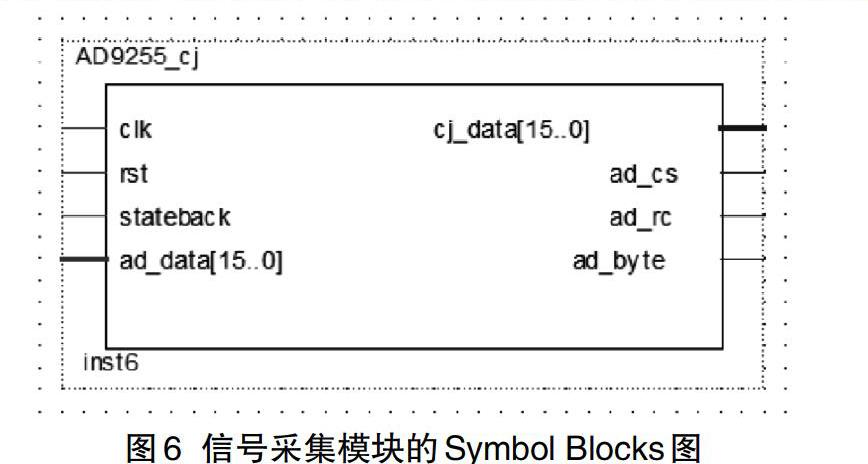

2.3 数据采集单元

系统的数据采集单元包括对探测系统输出的有用信号的采集及对仪器所需的环境变量(流量、温度、真空)的实时采集两个部分。由于探测系统输出的脉冲信号上升时间为250ns,为保证采样信号不失真,根据奈奎斯特采样定理,采样频率应大于两倍被采样信号的最高频率,本文选取AD公司的模数转换芯片AD9255,其采样速率高达125MSPS,精度为14位,可以实现探测系统输出脉冲的高速高精度数字化,由于环境变量变化缓慢,采样精度要求高,故选取AD公司的模数转换芯片AD976,其采样速率为200KSPS,精度为16位,可以满足系统要求,其硬件接口电路图如图2所示,AD976与FPGA采用并口方式连接,参考电压REF为10V。

3 数字逻辑的设计

本文采用QuartusⅡ软件进行自顶向下的模块化设计,根据系统需求,划分为时钟发生模块,系统复位模块,网络通信模块,数据转换模块,系统控制模块,信号采集模块,以及状态采集模块。系统的逻辑结构图如图3所示。

3.1 时钟发生模块

时钟发生模块将外部晶振输入的50M时钟信号通过锁相环输出系统的标准时钟以驱动系统的所有模块,同时将系统时钟根据需求的不同分频产生不同频率的时钟信号输出到系统的各个模块以满足需求,时钟发生模块的Symbol Blocks如图4所示。

3.2 网络通信模块

网络通信模块通过配置W5300实现UDP协议的网络通信,UDP是一种无连接的传输协议,资源消耗小,传输数据快,其通讯流程如图5所示。