波峰型低损耗负群时延微波电路研究

2020-03-30BlaiseRavelo李宁东万发雨葛俊祥

Blaise Ravelo 李宁东 万发雨 葛俊祥

1 南京信息工程大学 电子与信息工程学院,南京,210044

0 引言

时延是电子和通信系统[1-2]中的关键参数,现代电子以及通信系统常常遭受信号不同步的问题.尽管现代设计技术发展很快,但信号时延仍然是电子设计性能的瓶颈.如文献[3-5]所述,群时延与噪声效应相结合,会大大降低数字信号和微波器件的性能.为了解决信号时延问题,文献[6]提出了一种复杂的模拟电路均衡方法.然而,这种经典的解决方案可能会增加额外的正时延而使电路的性能有所降低.因此,负群时延电路的出现被认为是均衡电子系统时延的一种良好解决方案[7].

负群时延电路的负时延性能,对于大多数电子工程师来说依然难以理解,因此在详细介绍本文的工作之前,有必要先介绍一下负群时延电路发展历程.20世纪60年代,Brillouin[8]首次在色散介质发现了负群时延现象.20世纪80年代,Chu等[9]第一次在实验中验证了负群时延效应.近年来,一些研究小组对负群时延电路产生了浓厚的兴趣,设计并试验了各种负群时延电路[10-17].文献[10-11]给出了微波无源电路的负群时延合成器,并且引入了极低频的有源电路[12-13].但负群时延电路会产生超过20 dB的插入损耗[10-11].为了补偿电路的大损耗并使电路能够在更高频率下工作,可以将射频放大器级联到负群时延电路中,从而设计出低损耗的有源负群时延电路[14-15].然而,这些有源负群时延电路将不可避免地遭受由于集中元件固定值的设计不灵活的限制以及无法在微波频带电路中工作等困难.而且,有源放大器的使用将会增加带外噪声,并使电路结构更复杂.

此外,由于设计的复杂性,大多数负群时延拓扑结构无法集成到高速系统中.因此,利用分布式微带传输线构建的更简单和低损耗的无源拓扑结构相继被提出[16-17].这些分布式负群时延电路在高速系统中是可以集成的.然而,由于分析理论的复杂性,负群时延分布式电路需要进一步研究,并且无源负群时延电路在所需的负群时延带宽中,不可避免地具有大的信号衰减的特征.

把负群时延电路的插入损耗降低到10 dB以下是一项具有挑战性的研究工作.文献[18]设计了两个具有高特性阻抗和弱耦合系数的短路耦合微带线,这种基于耦合传输线的负群时延电路能够将插入损耗降低到7.43 dB[18].此外为降低信号插入损耗,文献[19]采用并行互连线来构建负群时延拓扑结构,并阐述了群时延理论以及设计方法[19].该并行互连线结构负群时延电路的插入损耗大约为5 dB.为设计出低损耗的无源负群时延电路,文献[20]通过把有损互连线连接在反馈环路中的隔离端和耦合端之间进而构成负群时延电路,该负群时延电路的插入损耗为2.4 dB[20].为了对负群时延电路进行分析和性能改进,仍然需要进一步研究一些新颖的负群时延电路拓扑结构,特别是低插入损耗负群时延电路的分析建模方法.

为此,本文提出了一种基于完全分布式传输线和耦合传输线的无源低损耗负群时延电路拓扑结构,该负群时延拓扑结构呈现出类似于“波峰”几何形状的拓扑结构.本文主要分为三部分.第一部分介绍电路的原理图,并基于等效电路的方法来探讨电路拓扑的S矩阵建模的理论方法.第二部分首先分析了电路的相关参数对电路性能的影响,其次介绍了电路仿真及电路加工测试,并通过理论计算、电路仿真和实际测试结果的比较验证了该负群时延电路的性能.最后,第三部分对论文进行了总结.

1 电路原理

1.1 电路结构描述

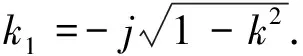

图1描述了提出的波峰型电路拓扑结构.该电路是由四条相同的微带传输线(TL1)、两条同样的耦合线(CL)、不等长的微带传输线(TL2,TL3)以及T型连接器(Tee)组成.对于传输线TLi而言,Z0,ai以及τi分别代表着传输线的特征阻抗、损耗以及时延,其中i={1,2,3}.假设传输线的长度为di,波速为v,则时延τi可用式(1)表示:

τi=di/v.

(1)

1.2 电路S参数及时延理论分析

为了分析电路的S参数,可以采用各个电路端口的归一化电压波(am,bm)来分析,其中m={1,2,3,…,14}.对于Tee连接器而言,根据微波电路理论可知:

(2)

对于微带传输线TLi而言,根据微波电路理论可知各个端口电压波的关系可由下式表达:

(3)

其中:

xi=ai×e-jωτi.

(4)

为便于分析,可将ai作如下表示:

ai=a.

(5)

对于耦合传输线CL而言,根据微波电路理论可知:

(6)

根据式(2)—(6),可以得到电路的S参数:

(7)

基于插入损耗S21,电路的群时延可以由下式表示:

τ(ω)=-∂∠S21(jω)/∂ω.

(8)

此外,I1(ω),I3(ω),I5(ω),I7(ω),以及h3(ω),h4(ω),h5(ω),h6(ω)的表达式可见附录.

2 电路仿真与实测

2.1 参数分析

为了进一步洞悉负群时延性能的变化趋势,根据式(7)和(8)可知,微带传输线的时延τ1,τ2,τ3会对电路性能产生影响.由式(1)可知,微带线的时延与微带线的长度有关,所以本文利用ADS仿真软件对微带线的长度进行参数分析.

图2探究了TL1的长度d1的变化对电路的群时延、插入损耗以及反射损耗的影响.可以看出,随着d1的变大,电路的中心频率表现出左移的动态,且电路的群时延GD的值一直小于-3 ns,损耗S21低于3 dB,反射损耗S11优于10 dB.图3和图4分别探究了TL2的长度d2以及TL3的长度d3的变化对电路的群时延、插入损耗以及反射损耗的影响,由图3和图4可知它们呈现出了与图2相同的趋势.

图5探究了频率范围在0.97~1.04 GHz内的耦合线的间距S的变化对电路的群时延、插入损耗以及反射损耗的影响.从图5中可以看出:随着间距S的变大,电路的中心频率呈现变大的趋势,此外电路的最大负群时延一直维持在-2.5 ns左右,且电路的反射损耗S11大于10 dB,损耗S21低于3 dB.

图6探究了频率范围在0.98~1.14 GHz内的耦合线和微带线的宽度W的变化对电路的群时延、插入损耗以及反射损耗的影响.从图6中可以看出:随着宽度W的变大,电路的中心频率呈现出逐渐变大的趋势,电路的最大负群时延和损耗S21一直在变大,然而电路的反射损耗S11却在逐步变小.

2.2 电路结构

这一部分主要对前文提出的电路理论进行验证.利用电路仿真软件ADS对设计的电路进行建模、仿真和优化,如图7a和7b所示,最终优化电路尺寸如表1所示.根据优化好的电路进行加工,实物如图7c所示,该电路采用的板材为FR4,具体参数如表1所示.

2.3 仿真与实测

对加工的负群时延电路(NGDC)用矢量网络分析仪(VNA)(罗德施瓦兹ZNB 20,带宽100 kHz 至 20 GHz)进行S参数测试,测试平台配置如图8所示,测试带宽为0.95~1.10 GHz,负群时延电路的反射系数、插入损耗、时延测试结果、仿真结果和模型计算结果对比如图9所示.

表1 负群时延电路的参数与优化结果

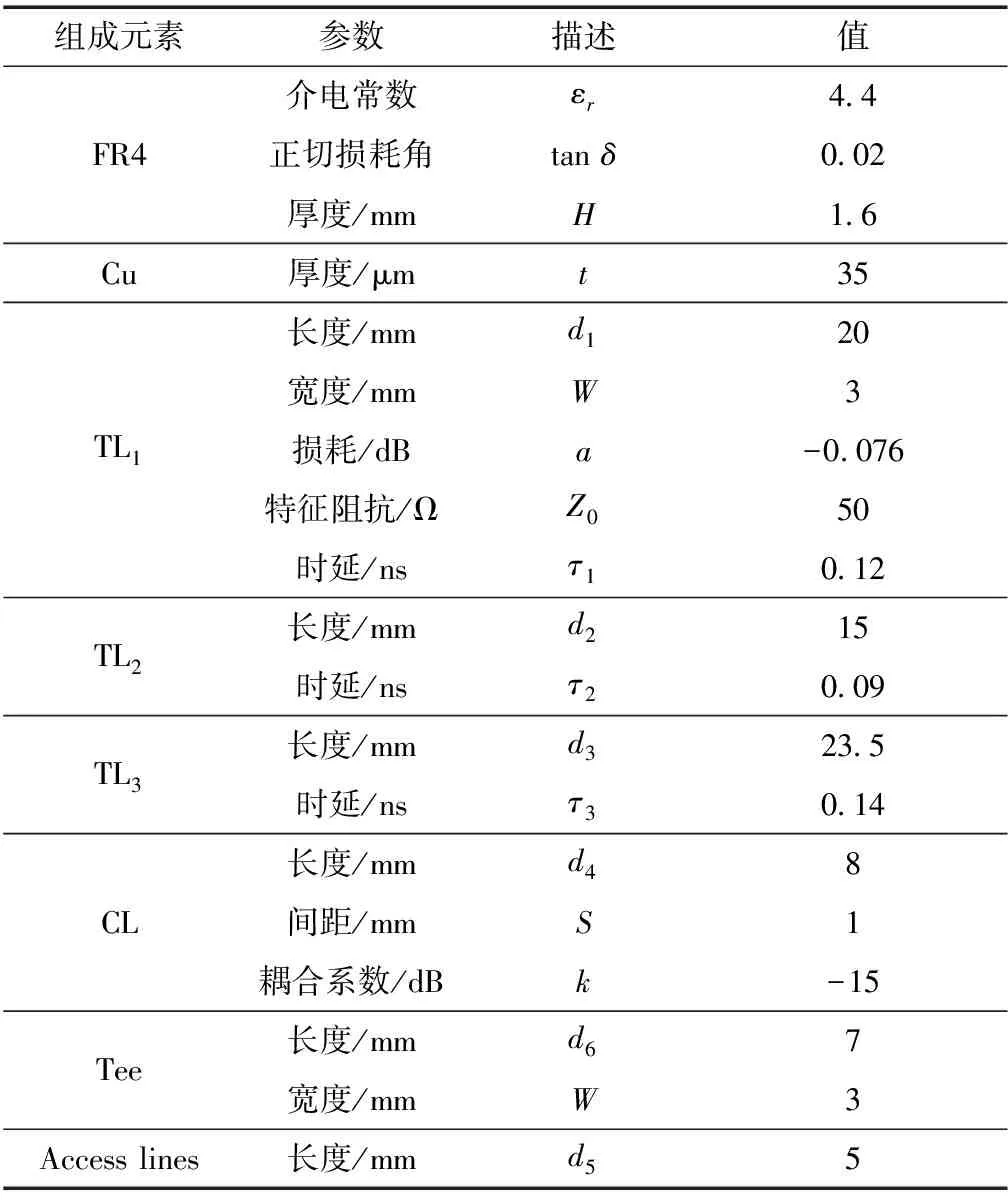

从图9可以看出对该电路在0.95~1.10 GHz进行计算、仿真与实测,并且各自曲线变化趋势大概一致.由图9a可知:计算、仿真与实测的中心频率分别为1.018、1.025以及1.017 GHz,在各自中心频率处的最大负群时延为分别为-1.25、-1.51以及-2.46 ns.由图9b和图9c可知:实测的插入损耗与反射损耗分别小于3 dB以及大于10 dB,如表2所示.

表2 计算、仿真与测试结果

从表2可以看出,负群时延电路中心频点的理论计算值、电路仿真值和实际测量值有一些偏移,大约为8 MHz左右,负群时延值有大约0.9 ns的偏差,这些偏差的主要原因是加工误差、介质基板的有效介电常数偏差、损耗偏差以及计算方法的精度偏差等.

2.4 性能对比

表3列出本文的负群时延电路与已发表文献中电路的性能对比结果,相比于其他电路,本文的负群时延电路最大的优势在于更低的电路损耗.

表3 本文电路与文献电路性能对比

3 结论

本文研究了“波峰”形状的分布式无源拓扑结构的负群时延电路设计方法. 该“波峰”形状的拓扑结构主要有微带传输线、耦合线以及T形连接器构成.可以证明,这种简单的分布式电路具有带通负群时延功能.本文还建立了整体电路拓扑的S矩阵的解析公式,从插入损耗表达式可以推导出群时延表达式.

带通负群时延功能可通过设计和加工“波峰”形状微带负群时延电路来验证.理论计算、电路仿真与实测的S参数以及群时延表现出了较好的一致性.实测结果表明:本文提出负群时延电路在中心频率1 GHz附近呈现出大约-2.46 ns的负群时延值,插入损耗约为-2.1 dB,反射系数约为-13 dB.与已有的负群时延电路[16-18]相比,本文提出的负群时延电路具有低的插入损耗.