结合STM32和FPGA的步进电机运动控制系统设计

2020-02-28陈祖霖

陈祖霖, 沈 英, 吴 靖

(福州大学机械工程及自动化学院, 福建 福州 350108)

0 引言

步进电机是一种简单、 稳定性良好的机电元件, 可以将电脉冲信号转换为角位移输出, 电机位移输出的大小与脉冲严格同步, 具有瞬间启动, 精确定位操作等特点[1]. 步进电机转动的位移由驱动脉冲的数量决定, 而转动的速度快慢通过脉冲频率的高低来表示, 因其只存在周期性的误差, 没有累积误差而深受欢迎. 使用单片机、 DSP等处理器对步进电机实现自动化控制, 能够更好地应用和服务于生活的各领域, 如数控系统、 医疗器械、 机械臂等, 但此类系统的资源消耗大且存在实时性差的问题. 现场可编程门阵列(field-programmable gate array, FPGA)是完全基于硬件的可编程, 相比于单片机FPGA具有多线程、 运行速度快等优点, 使其在电机控制系统的应用越来越广泛[2].

本研究主要以光学及精密机械检测系统中的光学位移台为例, 结合单片机与FPGA技术设计一种步进电机运动控制系统, 光学位移台主要用于光学元件的位移, 使得在光学测试系统中达到调光、 调焦的目的. 通过对上位机和运动程序的设计, 使得光学位移台能够实现速度、 位移的控制, 达到精准定位, 运行平稳及低噪声等控制要求. 采用FPGA可以同步或异步控制多个步进电机运动, 因此通过上位机界面可以控制多个光学位移台的运行. 光学位移台可以与其他种类的台子组成多维电动调整台. 步进电机控制系统借助增量式编码器完成电机位置的反馈, 实现了闭环控制, 其中微处理器STM32作为控制系统数据收发的转换模块, FPGA作为步进电机运动控制的核心模块. STM32和FPGA能各行其是, 完成系统对电机运动状态的控制及反馈. 经过仿真和测试, 该控制系统的稳定性良好, 达到所设定的要求. 本研究对系统的软硬件分模块进行说明, 实现对单路步进电机的控制, 为多路步进电机控制系统的开发提供了一定的参考.

1 控制系统的整体框架与介绍

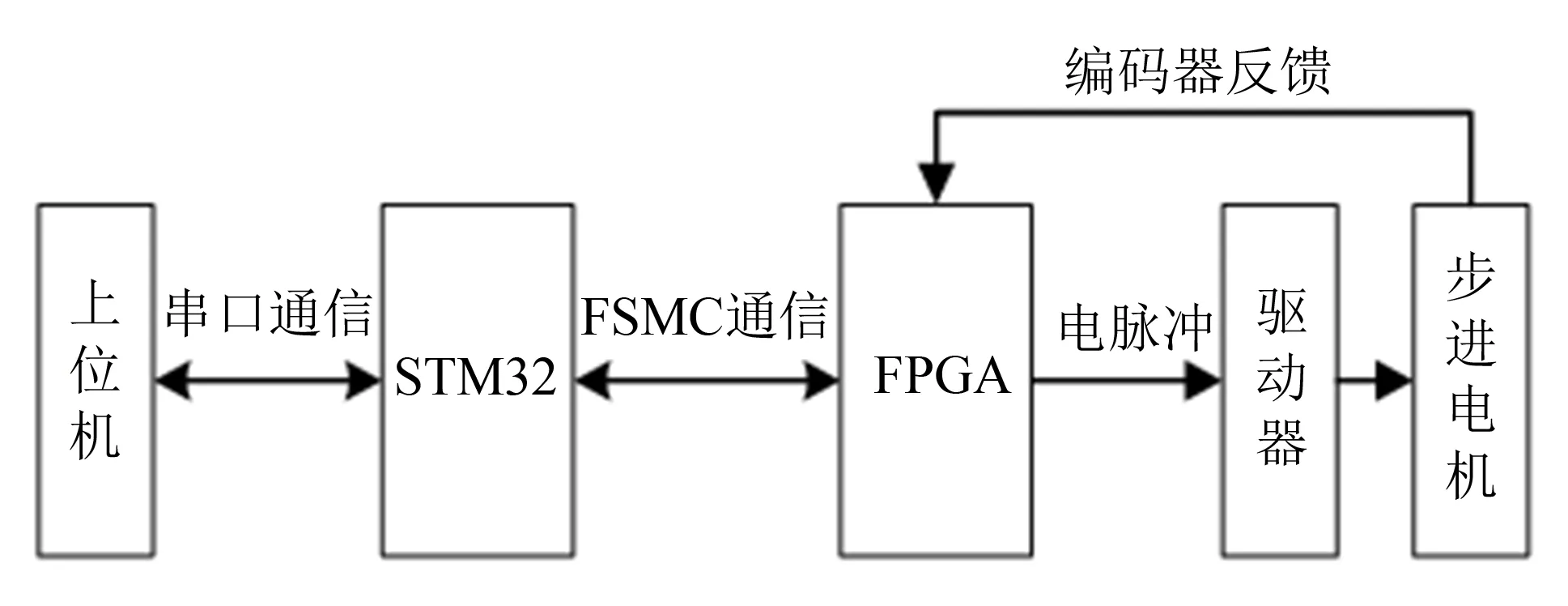

图1 控制系统结构框图Fig.1 Control system block diagram

本系统使用的FPGA为Cyclone IV系列, 基于VS(visual studio)软件设计了上位机人机交互界面; 利用串口通信, STM32F103把从上位机接收到的命令, 通过自带的FSMC(flexible static memory controller)接口, 将命令转化成FPGA能接收的方式. 控制系统结构框图如图1所示.

在人机交互界面进行步进电机运行参数的设置, 发送命令实现步进电机的启停、 速度等级选择、 加减速、 方向控制等状态转化. FPGA采用异步复位, 同步释放方式, 通过上位机复位按钮发送复位指令即可实现FPGA的系统复位, 增加了系统复位的可靠性. 应用Verilog编写偶数分频器, 实现脉冲的输出; 采用编码器完成电机的位置闭环控制, 在电机运行时, 可将电机运行的状态数据反馈到上位机. 因此结合STM32和FPGA不需要复杂的硬件电路, 就可以实现合理的资源分配, 通过上位机达到实时控制步进电机运动状态的目的, 提高整个系统数据传递与电机运行的稳定性和准确性.

2 系统硬件设计

2.1 通信模块

微处理器STM32与上位机用串口(usart)进行通信, STM32负责接收上位机发送的命令、 数据并进行转换, 然后发送给FPGA, 从而实现对步进电机的控制[3]. 同时STM32通过FSMC总线接收来自FPGA关于电机运行的反馈数据, 并通过串口通信在上位机界面显示出来. STM32与FPGA能实现多种方式的通信, 如USART、 SPI、 IIC等, 本研究使用高速数据采集及传输的FSMC总线进行并行通信[4].

图2 FSMC总线通信图Fig.2 FSMC bus communication diagram

FSMC是一种灵活的静态存储控制器, 单片机上有FSMC的接口, 通过数据线和地址线完成数据的发送和接收. 大规模FPGA设计基于SRAM结构, 对于外部SRAM的控制一般有: 地址线(A0~A18)、 数据线(D0~D15)、 写信号(WR)、 读信号(RD)、 片选信号(CS). 本研究使用3根地址线, 使用16根数据线一次传输2个字节. STM32与FPGA采用FSMC总线通信如右图2所示.

2.2 驱动模块

驱动器用于将FPGA发送的电脉冲信号转换为角位移. 当驱动器接收一个电脉冲信号时, 就会驱动步进电机转动一个步距角. 二相混合式步进电机的步距角为1.8°, 大小与驱动器所设定的细分数有关, 本研究设定驱动器为32细分, 因此细分后的步距角为0.056 25°, 转动一圈需要6 400个脉冲. 细分数的设定有利于减小电机的低频振荡和运行时的噪音. 步进电机的驱动器与FPGA采用的是共阴极接法, PUL+接脉冲信号、 DIR+接方向信号, 使信号能从ENA+接入, 将PUL-、 DIR-、 ENA-接公共地.

3 系统软件设计

在步进电机控制系统中, 微处理器STM32应用Keil uvision5编程软件和C语言进行程序的设计编写; 步进电机运行程序是基于Quartus II软件和Verilog语言设计编写的; 人机交互界面是借助Visual Studio软件以C#语言为基础进行设计的.

3.1 分频器的设计

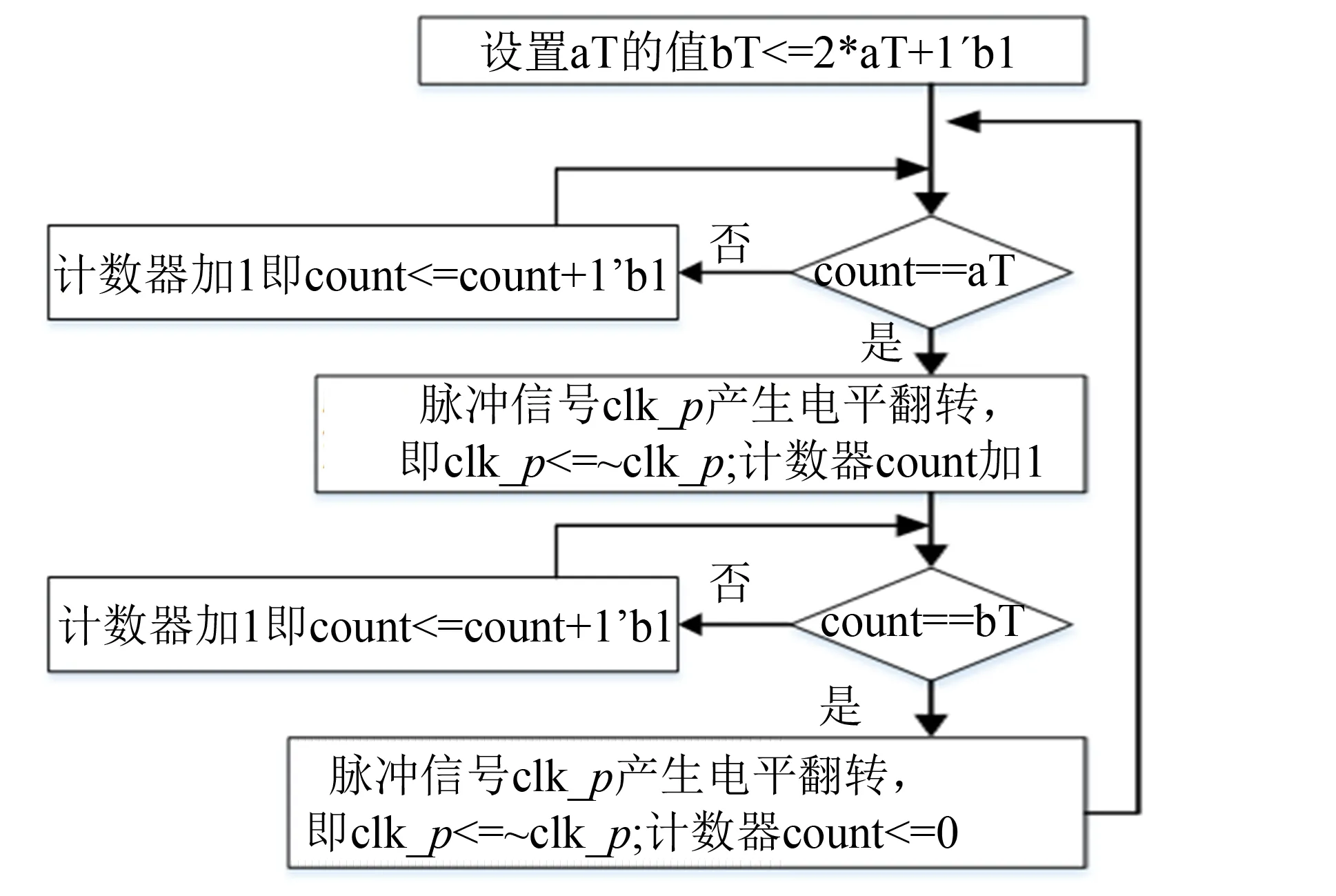

分频器利用一个高稳定和高准确度的基准频率产生一系列等间隔的离散频率信号. 步进电机的持续运转要通过一系列的脉冲来驱动, 通过对分频器的设计可产生连续不断的脉冲信号和获得需要的脉冲频率. 定义步进电机运行的脉冲频率为f(Hz), 分频系数为p(即p分频), 两者关系如下式所示:

(1)

图3 分频器设计流程图Fig.3 Divider design flow chart

3.2 状态机设计

步进电机在进行加减速时, 通过控制单位时间内输出的脉冲数来改变其脉冲频率[5]; 如在加速过程脉冲频率会不断增大, 对应的脉冲周期相应减小, 通过分频技术可以得到想要的脉冲频率.

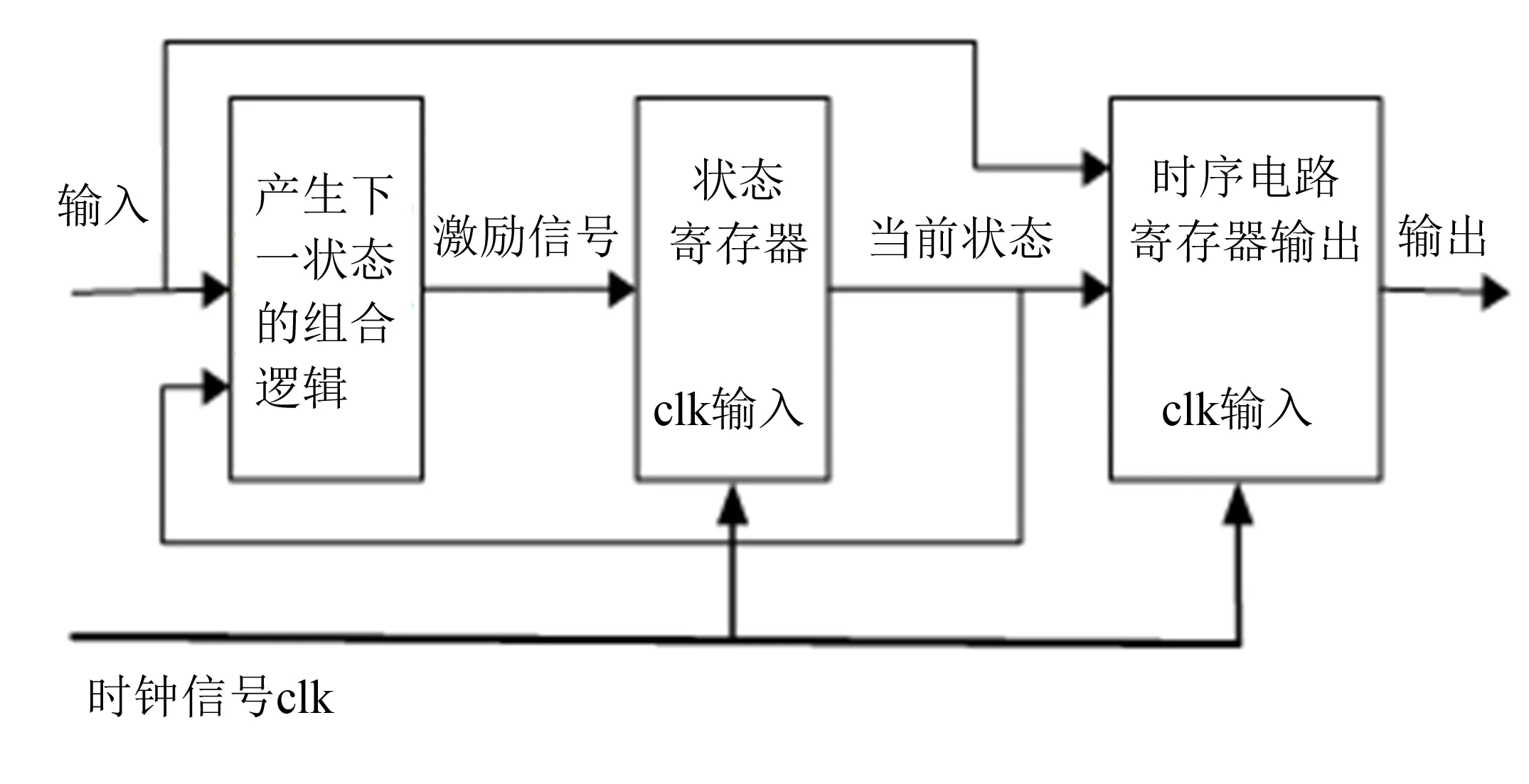

图4 Mealy状态机模型Fig.4 Meary state machine model

脉冲频率的变化通过有限状态机(finite-state machine, FSM)完成程序设计; 本研究使用三段式Mealy(米勒)状态机, 包括2个时序逻辑的always块和一个组合逻辑的always块, 通过设置现态(cstate)和次态(nstate)两参数完成加减速过程状态之间的转移和脉冲输出. 图4为Mealy状态机模型.

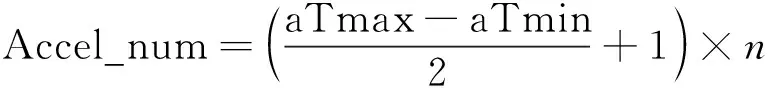

步进电机加减速包含加速、 匀速、 减速这三个阶段; 当电机接收到加减速命令后, 以设定的起始脉冲频率加速到最大速度点, 然后进行匀速运动, 达到减速点时减速至起始频率后停止[6]. 定义在加减速过程中步进电机的位移即脉冲数为Pulse_num, 起始分频系数aTmax=a, 最大转速时分频系数aTmin=b, 每频率段的脉冲数(位移)为n, 设定每发出n个脉冲分频系数减2, 程序上这样设定aT=aT-2, bT=2×(aT-2)+1. 由于aT与bT在程序运行时是并行的, 因此aT的值为前一状态保留的值. 加速阶段的脉冲数Accel_num计算如下:

(2)

匀速阶段的脉冲数为Uni_num计算如下:

Uni_num=Pulse_num-2×Accel_num

(3)

因此, 对于给定的脉冲总数, 系统运行时都会按照程序中的设定, 对三个阶段所需要的脉冲数进行分配. 步进电机转向的控制, 主要由方向信号的高低电平来决定的; 所设计的控制系统默认电机为逆时针方向转动即dir=0, 当方向信号变为高电平即dir=1时, 电机为顺时针方向转动.

3.3 例化模块

模块化设计是FPGA最基本的理念, 一个较为复杂的控制系统往往包含多个子模块, 采用例化的方式可将各模块的输入和输出进行连接. 因此在FPGA中实例化控制系统的各功能模块, 有利于代码的简化和修改, 使系统在实时性和灵活性等方面有很大提高, 有利于实现步进电机运动状态的控制[7]. 现对电机运行采用模块的例化, 实现层次化设计. 将电机运行分成4个.v文件来实现, 顶层文件drive_1.v, 负责例化模块并连线; 速度选择模块sel_speed.v, 包含4个不同的速度等级; 加减速模块T_speed.v, 通过有限状态机实现加减速运动的控制; 闭环控制模块closed_loop.v, 防止电机丢步. 系统经例化处理后, 综合结果的顶层模块图见图5 .

3.4 编码器模块设计

闭环步进电机的补偿, 补偿值为编码器测得的实际步数与设定步数的差值; 在电机到达停止点时由驱动器完成补偿脉冲. 增量式光电编码器与电机相连, 当电机接收驱动脉冲转动时, 便带动了码盘转动, 从而产生了转角信号[8]. 光电编码器中A、 B是相位差为90°的脉冲波; Z信号用于调零, 编码器每旋转一圈时产生一个脉冲信号.

在一个编码器周期内, A、 B信号共有4次的跳变沿, 因此为了提高编码器的精度, 采用4倍频技术. 电机正转时, 每检测到一次跳变沿, 设置可逆计数器counter加1; 电机反转时, 每检测到一次跳变沿, 则可逆计数器counter减1. 以步进电机正转为例, A信号超前B信号90°, 相对的电平信号变化为10-11-01-00, 如图6所示.

4 仿真和调试

4.1 FSMC通信仿真

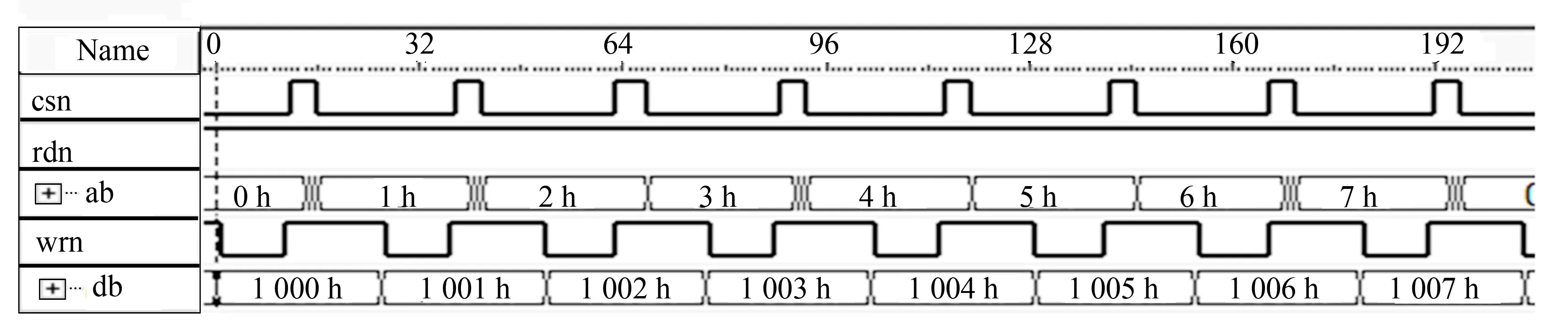

FSMC通信使用读写模式A, 因此FPGA通过模式A的时序完成数据的写入和读取. 微处理器STM32的FSMC接口支持8/16/32位数据宽度, 进行数据传输的实验, 在FPGA对应的地址上写入16位数据宽度, 如表1所示.

表1 STM32向FPGA写入数据表

在FPGA程序代码里设置db为16位inout类型数据, 即从端口内部看, 可以对端口进行赋值即输出数据, 也可以从此端口读入数据即输入. 设置assign db=rd?indata:16’hzzzz, rd(读信号)为wire型变量, 当rd=1时, 可以进行数据的输出, rd=16’hzzzz时, 表示高阻”Z”状态, 输出受限制. 微处理器STM32向FPGA写入数据时, 片选信号csn为低电平有效, 写信号wrn为低电平有效; 当wrn显示为低电平时, 在ab上的地址0~7 h分别写入数据db为1 000~1 007 h, 实现了STM32对FPGA给定地址写入给定数据.

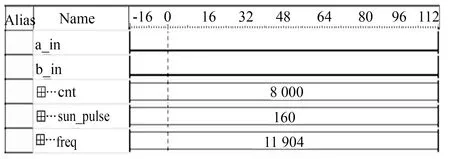

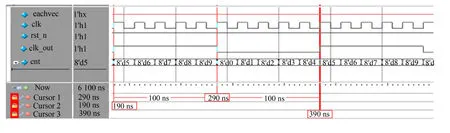

应用嵌入式逻辑分析仪SignalTap实时显示从微处理器发送来的数据, 如图7所示. 在进行命令发送时, 当上位机发出命令后, 微处理器STM32通过串口实现数据的接收并进行转换, 通过FSMC总线把转换后的命令发送给FPGA, FPGA接收到发送来的命令后, 开始执行相关的运行模块, 控制步进电机的运行状态.

图7 SignalTap数据传输实时仿真图 Fig.7 SignalTap data transmission real-time simulation diagram

4.2 输出脉冲仿真

实验所用的FPGA为ALIENTEK新起点EP4CE10开发板, 系统时钟为50 MHz, 即一个时钟周期为20 ns,应用Modelsim对FPGA的输出脉冲实现联合仿真. 本研究设定4个速度等级, 本次以分频系数为25 000的输出脉冲为例进行仿真实验, 为了节省仿真时间, 把分频系数25 000缩小2 500倍即为10, 在程序中设置参数aT=8’d4、 bT=8’d9, 运行程序仿真结果如图8所示. 在一个脉冲周期内, 高电平的时间为100 ns即5个时钟周期, 低电平也为100 ns, 因此输出的脉冲占空比为50%, 为偶分频. 为了实现步进电机的不同速度等级, 可采用设置不同的分频系数来获得不同的脉冲频率.

步进电机一个脉冲运行一步, 在电机加减速阶段, 单位时间内的位移会发生变化. 因此在每个频段都设置相同的位移, 即在加速时, 位移一定, 随着速度的增大, 所用的时间减小; 在减速时, 随着速度的减小, 所用的时间变长. 程序中设置位移为2个脉冲, 起始的分频系数设为15, 脉冲数为30个, 用Modelsim进行加减速仿真, 结果如图9所示.

从图9可以得出, 在进行加减速时分为3个阶段: 在加速阶段, 脉冲频率每隔2个脉冲增大一次, 即对应图中左边部分脉冲宽度减小, 脉冲数为6个; 匀速阶段的脉冲频率不变, 即对应图中间部分脉冲宽度不变, 脉冲数为18个; 减速阶段脉冲频率为每2个脉冲减小一次, 即对应图中右边部分脉冲宽度增大, 脉冲数为6个; 当步进电机的脉冲频率降到起始频率即分频系数为15时, 输出脉冲数为零, 步进电机停止运行. 因此, 输出脉冲的仿真结果表明, 在加减速运行时能够准确的达到设定的脉冲数.

4.3 系统的运行与调试

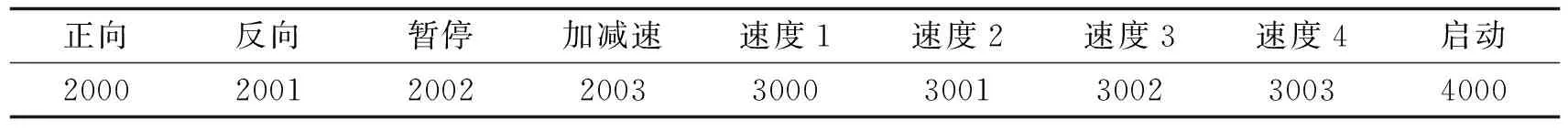

搭建电机运动控制系统所需要的实验平台, 进行实际的运行和调试, 如图10所示. 在进行通信程序设计时, 应设置好步进电机运动过程所对应的状态码, 如表2所示. 在上位机设有数据的接收区, 接收来自FPGA关于电机运行状态的反馈数据, 接收模式设有两种为十六进制hex和字符, 这里为方便显示, 设为字符串接收模式. 打开上位机软件进行操作, 配置串口号、 波特率和电机运行参数, 设置完成后, 点击运行, 步进电机就能按照设定的要求运转. 步进电机接收到命令运行稳定, 并通过FSMC总线成功向上位机发送运行状态的反馈数据. 控制系统的上位机操作界面如图11所示. 在数据接收区显示, 地址1、 2、 3的数据为0, 表示系统复位完成, 将3个地址里的数据清零; 接收到的数据1: 3003 2:2000 3:4000, 查询表2可知步进电机以速度等级4、 正向、 启动; 系统复位后, 1:0 2:2003 3:0, 查询表2可知步进电机进行加减速运动. 因此设计的上位机能够准确地接收和发送命令, 控制步进电机运行.

表2 电机运行状态编码

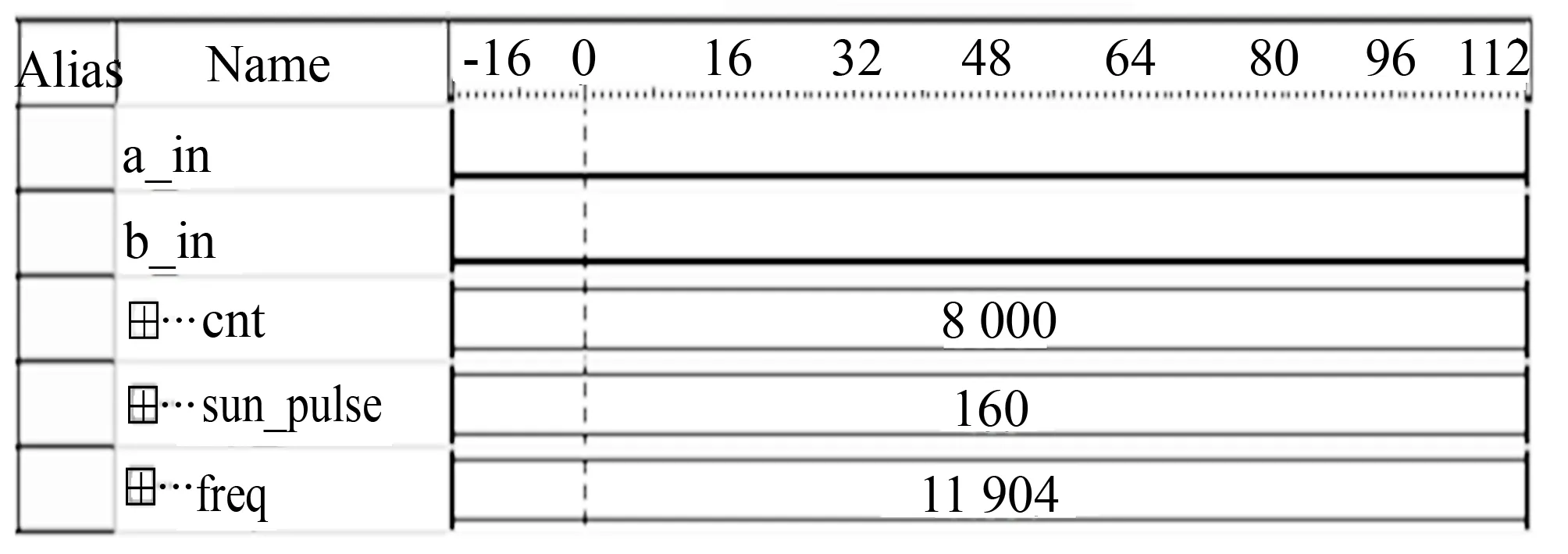

图12 电机位置闭环控制图Fig.12 Motor position closed loop control diagram

步进电机在加减速运行时, 通过SignalTap实时测得的电机位置闭环控制图如图12所示, 图中显示编码器计数cnt, 补偿脉冲sup_pulse, 以及电机运行脉冲频率freq. 在调试中设定目标脉冲数为set_p=256 160个; 从图12中得到编码器计数cnt=8 000, 因采用4倍频, 计算出编码器实际计数值为32 000, 实际测得的脉冲数actual_p=32 000×8即256 000个. 闭环控制采用步校验, 在电机运行到达停止点之后补偿160个脉冲, 实现电机位置的闭环控制. 因此经过调试, 控制系统达到光学位移台的要求, 能实现速度和位移的精确控制, 通过上位机能准确地控制步进电机的运动状态, 进而控制光学位移台平稳的运行.

5 结语

本研究结合STM32和FPGA设计了一种步进电机控制系统, 采用编码器, 通过步校验的方式实现电机位置的闭环控制. 此外, 借助Visual Studio进行UI设计, 提供了人机交互界面. 仿真和测试结果表明, 该控制系统稳定性良好且控制精准, 步进电机运动的各项指标符合设定要求. 利用FPGA并行速度快的特点, 在本系统的基础上可完成对多路步进电机控制系统的设计, 可移植性高, 因此具有广泛的适应性和参考价值.