LTE-A空口监测仪下行基带板的可行性分析

2020-02-18王美乐张治中

王美乐,张治中,2,席 兵

1.重庆邮电大学 通信与信息工程学院,重庆400065

2.重庆重邮汇测通信技术有限公司,重庆401121

1 引言

目前,随着增强型长期演进(Long Term Evolution-Advanced,LTE-A)的发展和应用,以及TD-LTE-A载波聚合技术中的终端接收机、TD-LTE无线综测仪等的出现,把LTE-A改进的网络架构以及新兴的无线通信技术运用到实践中,促进了国内仪表的发展[1-2]。在国内众多的LTE-A产品中,依然缺少LTE-A空口监测类仪表。虽然美国和日本的两家仪器仪表公司研制的空口监测仪器在行业内获得一定的应用,频谱分析、基带数据解析以及协议栈解析等功能也比较全面,但是该仪表操作复杂并且功耗高,很大程度上解决不了现场的问题,仅能应用于实验室内部[3]。相比国外的监测仪器,LTE-A空口监测分析仪在保证其应有功能的条件下降低了操作复杂度,大幅度减少了仪表的体积,解决了现场应用受限的缺点,因此LTE-A空口监测分析仪在一定程度上促进了国内仪器仪表的发展,具有很高的研究和应用价值[4-6]。

在LTE-A空口监测分析仪中,基带板负责接收射频板采集的数据,将采集到的数据进行物理层的处理,从而恢复出基带数据,然后将基带数据传到上层做进一步处理,因此基带板在监测仪保证正常的监测功能中发挥着不可或缺的作用[7]。近年来,许多相关的研究人员对基带板进行了深入的研究:文献[8]利用现场可编程门阵列(Field-Programmable Gate Array,FPGA)、数字信号处理器(Digital Signal Processor,DSP)、进阶精简指令集机器(Advanced RISC Machine,ARM)的各自优点,设计了一种多通道基带处理硬件架构方案,实现了良好的人机交互界面,通过实际上板测试,验证了板卡设计的合理性与正确性。文献[9]对移动终端管控系统基带板卡进行研究,给出了一种DSP+ARM+FPGA多通道基带板卡设计方案,并且对系统硬件电路进行详细设计和实现,验证了设计的正确性。文献[10]基于DSP和FPGA间的音频互交换文件(Audio Interchange File,AIF)接口需求,设计了多通道复用、空口对齐方案以及两套传输不同数据流的方案,实现了AIF接口能传输连续数据流和突发数据流。虽然近年来对基带板的研究已经证实了其应用价值,但是在基带板设计之前却缺少可行性分析,只是通过最终的实现来验证其可行性。殊不知实现时,若基带板上的处理器达不到其所需的处理速率,内部资源不足,存储器内存不足,或者所需传输速度达不到要求,都需要重新选择芯片并且重新设计原理图,在这个过程中为此付出的时间和精力是相当大的。因此在设计LTE-A空口监测仪的基带板之前,有必要对基带板的可行性进行分析。本文首先分析了基带板上核心处理器所需的处理速度,确定了FPGA的选型,然后重点分析基带板上存储器的存储能力以及元器件的总线能力,确保芯片的选型能够达到要求,为基带板的选型以及原理图设计提供参考。

2 基带板的可行性分析

2.1 基带板的整体架构

在LTE-A空口监测仪中,基带板主要负责完成1个2×2多输入多输出系统(Multiple Input Multiple Output,MIMO)的载波单元的基带处理,包括基带解调、信道解码等过程恢复出基带数据,通过高速串行计算机扩展总线(PCIe总线)采用成组数据传送方式将基带数据送到层二处理板。除此之外,基带板还需要完成两路基带数据的存储,即稳定存储10 min离线基带数据。基带板需要完成的技术指标如下:

(1)支持时分双工(Time Division Duplex,TDD)和频分双工(Frequency Division Duplex,FDD)模式;

(2)支持1.5 MHz、3 MHz、5 MHz、10 MHz、15 MHz和20 MHz信道带宽;

(3)支持子载波间隔为15 kHz;

(4)支持采样数据精度为12 bit;

(5)支持正交相移键控(Quadrature Phase Shift Keying,QPSK)、正交幅度调制(16QAM)、相正交振幅调制(64QAM)下行解调功能;

(6)支持正常循环前缀(Normal CP)和扩展循环前缀(Extended CP);

(7)支持LTE和LTE-A增强特性,包括载波聚合(最大支持5载波聚合,含intra-band、inter-band载波聚合)。

本基带板是面向LTE-A处理能力的需求进行设计的,由于基带板的最大支持带宽是20 MHz,该带宽下的采样率为30.72 Mb/s,采样的每个基带数据都是由16位的I路数据和16位的Q路数据组成,此时单天线的数据速率为30.72 Mb/s×(16+16)=0.983 04 Gb/s,由于基带板最大支持5载波聚合,则基带板需要提供的传输速率为5×0.983 04 Gb/s=4.915 20 Gb/s。基于此需求,并且为了保证核心处理器有足够的内部资源供电路使用,基带板采用FPGA作为核心处理器,型号为XC7Z100-2FFG900I。该芯片是Zynq®-7000系列芯片中内部资源最丰富的一款芯片,包含一个双核的ARM处理器和通用的逻辑部分,逻辑部分和ARM部分协同工作,其CPU频率高达1 GHz。该FPGA芯片支持的外设接口包括:

(1)丰富的存储器接口:动态内存控制器支持DDR3、DDR3L、DDR2和LPDDR2内存,静态存储器控制器支持NAND闪存接口;

(2)DDR控制器和相关的以太网接口:支持DDR3的速度可高达1 833 Mb/s;

(3)PCIe接口:可根据系统设计要求进行配置,在2.5 Gb/s或5.0 Gb/s数据速率下运行;

(4)GTX收发器:采用倒装芯片封装的高性能GTX收发器,能够提供高达12.5 Gb/s的线路速率。

除此之外,XC7Z100芯片支持的外设还包括两个支持IEEE Std 802.3和IEEE Std 1588 2.0版的10/100/1 000三速以太网MAC外设,两个USB 2.0 OTG外设,两个SD/SDIO2.0/MMC3.31兼容控制器以及两个高速UARTs等,满足基带板的需求。

本文在进行存储器件的选型时,缓存10 min基带数据的存储器选用mSATA。由于mSATA在数据传输过程中可能会发生中断,实时性不能满足要求,因此在XC7Z100芯片的外部连接了一片DDR3存储器,以保证mSATA与FPGA之间数据的良好传输。XC7Z100芯片的逻辑部分完成基带接收解调工作,ARM部分负责配置调度控制,这两部分在工作时,需要存储大量数据,因此设计时在XC7Z100芯片外部设计了外部存储器,均采用两个16 bit的DDR3并联成32 bit的方式作为存储器件进行缓存。整体架构如图1所示。

图1中射频板采集的两路基带数据传入基带板,mSATA作为存储基带数据的容器存储两路基带数据,由逻辑部分连接的一片DDR3作为缓存。图中的NAND Flash和SD卡作为基带板上FPGA上电的两种上电模式,两个存储器均配置了XC7Z100芯片的启动程序,SD卡未插入时,NAND Flash作为默认的启动程序,在SD卡插入时,默认从SD卡启动。与ARM部分相连的两个DDR3用作ARM部分的缓存,33.33 MHz的晶振作为ARM外部处理的时钟。逻辑部分的看门狗用来检测系统运行是否正常,各种时钟的晶振作为逻辑部分外部所需的时钟,经过基带板处理之后的基带数据经过PCIe接口传到层二处理板中。基带板中需要考虑可行性的元器件,最终确定型号如表1所示。

表1 元器件选型

在此之前已经确定了XC7Z100芯片符合需求,接下来主要针对mSATA、DDR3、PCIe总线进行可行性分析,主要是分析其存储能力和总线能力是否满足需求。

2.2 存储能力分析

2.2.1 mSATA存储

基带板支持的20 MHz带宽下采样点2 048个,支持子载波间隔为15 kHz,则每一路基带数据的最高时钟速率为2 048×15 kHz=30.72 MHz。由于采样的数据精度为12 bit,通过PCIe总线以双通道的方式向基带板传输数据,因此可以计算每秒钟存储的基带数据为12×2×2×30.72 Mb=1 474.56 Mb。那么mSATA 10 min所存储的数据量为1 474.56 Mb×10×60=110.59 GB。基带板中选用的mSATA型号内存容量为500 GB,存储能力远远满足要求。

2.2.2 DDR3存储

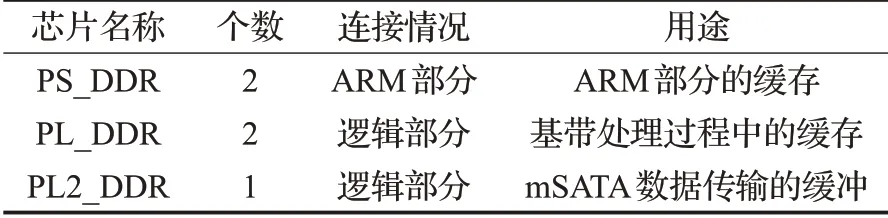

在基带板中设计了五片DDR3,其中一片用于mSATA传输数据的缓冲内存,由于只是弥补mSATA的实时性,因此对该DDR3的要求不高;其中两片DDR3用于XC7Z100芯片ARM部分的缓存,即缓存ARM部分的配置程序;还有两片DDR3用于基带处理过程中信道估计之后数据的存储。具体连接情况和用途如表2所示。

表2 基带板上各DDR3用途

在这些DDR3存储器中,用于基带处理过程中的缓存数据量最大,因此若该DDR3的存储能力满足需求,其他DDR3必然也能够满足要求。在计算该DDR3存储数据量时,按照LTE-A下行基带处理的最大配置来计算,具体配置如表3所示。

表3 配置信息

该DDR3存储以子帧为单位,由36.211协议[11]可知20 MHz信道带宽下对应的传输带宽为100个资源块(RB)。在Normal CP情况下,可以计算一个RB包含了84个资源元素(RE),因此在20 MHz下,一个子帧包含了两个时隙,可以计算得出一个子帧包含了1 200×14=16 800个RE。每个RE携带2个频域数据和4个H值,相当于6个数据,而每个数据包含4 Byte,因此可以计算出每个子帧中需要存储的最大数据量是16 800×6×4=403 200 Byte,即使考虑需要缓冲多个子帧的情况,总的存储需求也远远小于一个DDR3的存储容量。

2.3 总线能力分析

2.3.1 PCIe总线

PCIe总线将GTXE2收发器用于Xilinx 7000系列,能够与XC7Z100芯片完美兼容。XC7Z100芯片支持PCIe总线8B/10B编解码方式,并且可根据系统设计要求配置PCIe总线的时钟以及通道数[12]。本文中基带板接收两路基带数据,数据传输速率可达到5.0 Gb/s。由于LTE-A空口监测仪的背板可插入10块基带板用于上下行的基带处理,因此可以通过配置锁相环使得不同的基带板共享同一个采样时钟,保证每块基带板的采样时钟同步,从而严格地在同一时刻进行数据采集。

2.3.2 SATA总线

在基带板接收数据时,数据精度为12 bit,通过PCIe总线以双通道的方式向基带板传输数据,传输数据分为两路,由此可以计算每秒钟存储的基带数据为12×2×2×30.72 Mb=1 474.56 Mb,即mSATA需要的传输速率为1.47 Gb/s。

SATA总线所需的吞吐量遵循LTE-A下行基带处理中需要的吞吐量,限于篇幅,加之已有前人对LTE-A下行吞吐量进行深入的研究,因此本文直接加以运用。在20 MHz的带宽下,TDD-LTE单载波下行峰值吞吐量可达到160 Mb/s,Cat5进行测试时,FDD-LTE下行单UE的吞吐量能够达到127 Mb/s[13-14]。

SATA接口先后出现了SATA 1.×、SATA 2.×、SATA 3.×版本,最大传输速率分别对应1.5 Gb/s、3 Gb/s和6 Gb/s[15]。本设计选用的三星硬盘采用了SATA3.0接口,传输速率理论最大可以达到6 Gb/s,接口支持高达600 MB/s带宽吞吐量,总线的传输速率和带宽吞吐量均能满足要求。

2.3.3 DDR总线

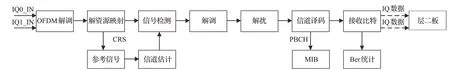

在基带处理过程中,XC7Z100芯片需要对接收数据完成数据的处理工作,处理过程如图2所示。

基带板接收的两路基带数据首先需要解OFDM基带信号,然后计算出CRS在时频资源网格中的位置,从而进行导频分离,将取出的导频信号进行信道估计,估计输出的H矩阵作为信号检测的输入信号,而用户参考信号、同步信号以及各个信道资源依次按照其解资源映射规则进行解资源映射,解出来的各信号以及信道资源依次经过信号检测、解调、解扰、信道译码(其中PBCH信道译码成功后得到系统信息块(MIB)),最终把处理结束的比特数据上传到层二处理板进行上层处理。

XC7Z100芯片中的DDR3控制器最大支持32位宽,考虑到在基带数据的处理过程中信道估计的数据量较大,并且需要减少数据传输过程中的延迟,因此设计中采用两片16位宽的DDR3并联的方式进行缓存。在计算基带处理过程中每秒传输的数据量之前,需要先确定信道估计后单个RE包含的数据量。在信道估计模块工作时,输入数据为两路频域数据,输出为估计后的H矩阵,而输出的H矩阵需要考虑2发2收模式,因此单个RE的数据量包括2个频域数据和4个H值。由于输入的两路频域数据,每个数据包含16 bit的I路数据和16 bit的Q路数据,同样每个H矩阵包含了16+16=32 bit的数据量,因此单个RE携带的数据量为2×(16+16)+4×32=192 bit,从而可以计算每秒钟传输的数据量为192×1 200×14×100=322.56 Mb,即基带处理过程中所需的传输速率为322.56 Mb/s。本文所选的型号为MT41K256M16HA-125IT:E的DDR3芯片最高传输速率能够达到1600 Mb/s,并且在XC7Z100芯片中DDR控制器支持的范围内,符合要求。

3 测试

3.1 PCIe接口测试

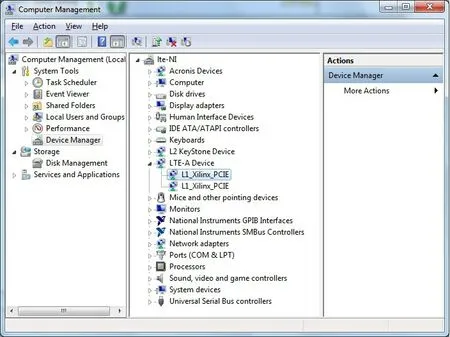

LTE-A空口监测仪中基带板提供PCIe Gen2接口,PCIe接口通过P2连接器连接到监测仪的PCIe背板。本文通过对PCIe接口进行测试来验证PCIe信号能够正常传输,若PC机与基带板的PCIe接口能够正常连接,则证明PCIe接口功能正常。在测试PCIe通信功能之前需要将基带板插入到监测仪的PCIe机箱中,在设备管理器中查看是否有新硬件显示,若出现未安装驱动的新硬件选择安装公司提供的PCIe驱动软件,安装完成之后,在设备管理器的LTE-A设备中发现“L1_Xilinx_PCIe”设备,说明基带板与背板之间的硬件连接没有问题。如图3所示,证明了PCIe接口可以正常与PC机通信。

3.2 DDR3测试

DDR3以及mSATA的可行性均是通过Vivado工具进行测试验证。Vivado是2012年Xilinx公司发布的一套集成设计环境,该环境结合了各种可编程技术,能够在满足客户需求的条件下定制设计流程[16]。相比Xilinx的ISE,Vivado工具的出现提升了设计的生产力以及升级扩展能力,加速了FPGA的设计。

图2 下行基带数据处理过程

图3 PCIe设备测试结果

在测试DDR3可行性时主要是测试其功能,若DDR3能够正常读写,那么DDR3的可行性就得到了验证,当然其传输速率以及吞吐量同样能够满足要求。虽然基带板上有5片DDR3分别作三种用途,但是DDR3都是通过Vivado软件进行可行性测试,并且测试过程相同。因此在DDR3的测试过程中,本文以XC7Z100芯片逻辑部分连接的两片DDR3为例进行测试,其他DDR3的测试参考该DDR3的测试过程。

在测试DDR3之前,将PC机连接至基带板上XC7Z100芯片的JTAG接口,该接口为2×7的连接座,PC机打开Vivado工具,若基带板不插入机箱中测试,则需要额外提供一个40 MHz的时钟。测试过程如下所示:

(1)在例程中打开mig_7series_0_example文件,该文件中存储了DDR3测试的配置程序;

(2)建立连接,将Vivado工具连接到基带板;

(3)录入程序,将生成的比特流文件加载到基带板中;

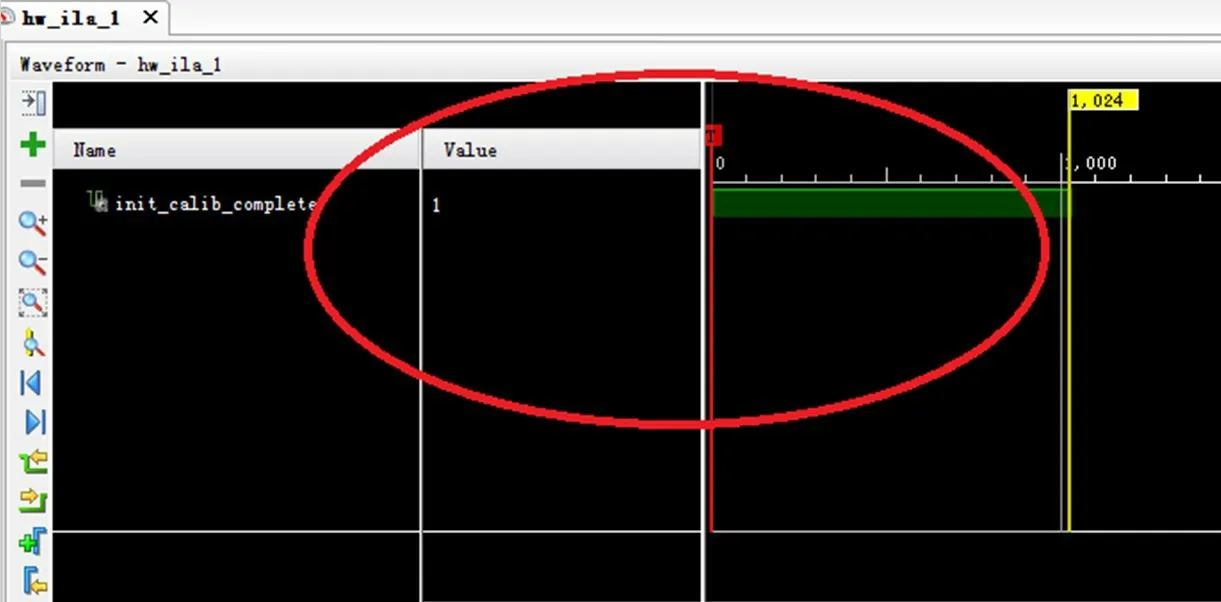

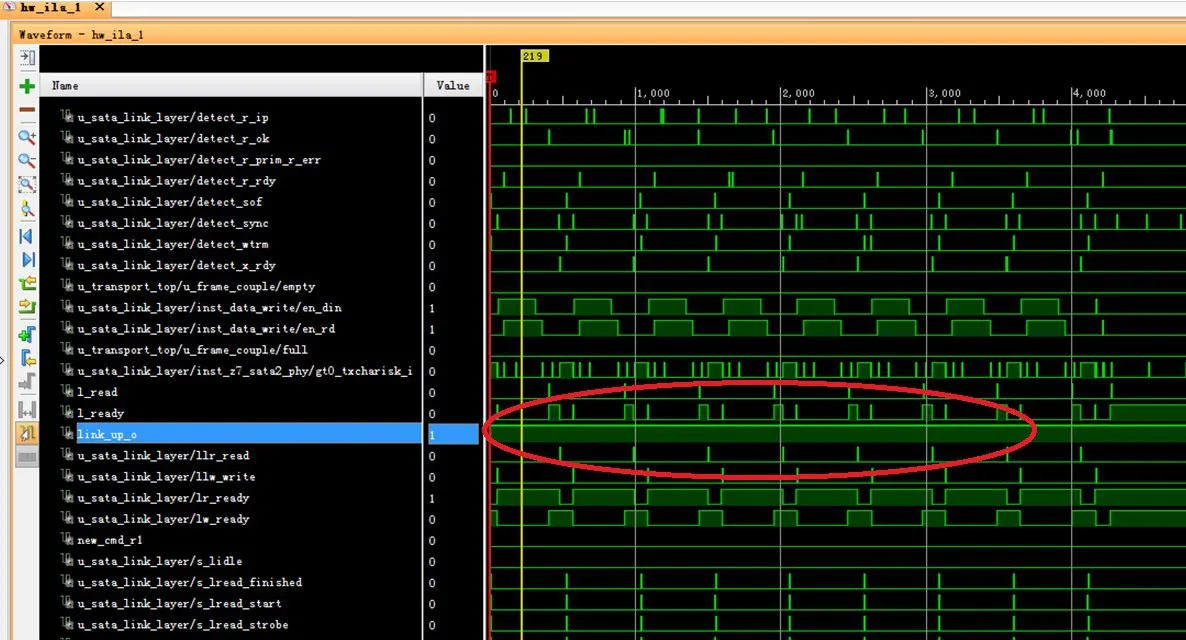

(4)确定触发信号为上升沿触发,运行触发器,查看数据触发值,最终触发结果如图4所示。

图4 DDR3测试结果

图4中信号触发值为1,init_calib_complete信号波形显示为高,说明该DDR3运行正常,由此可以验证该DDR3存储器可行。

3.3 mSATA测试

mSATA负责存储基带板接收的基带数据,为了防止测试mSATA过程中基带板上的其他硬件出现问题,将其放在其他硬件测试结束之后进行测试。与DDR3测试过程相似,通过对mSATA进行功能测试验证mSATA的传输速率以及吞吐量达到要求。在测试之前,将PC机连接至基带板上XC7Z100芯片的JTAG接口,该接口为2×7的连接座,PC机打开Vivado软件,测试过程如下所示:

(1)建立连接,加载测试配置文件;

(2)添加触发信号,修改上升沿触发;

(3)点击触发,查看link_UP_0是否为高,运行结果如图5所示。

图5 mSATA测试结果

图5中触发值为1,link_UP_0信号波形显示为高,说明mSATA运行正常,由此可以验证mSATA存储器可行。

3.4 系统测试

本文将基带板卡插入LTE-A空口监测仪中,先依照LTE-A空中接口监测分析仪表测试规范要求配置小区信息,再利用仪表解析其配置信息。通过仪表解析MIB信息的正确性以验证下行基带处理流程的正确性。

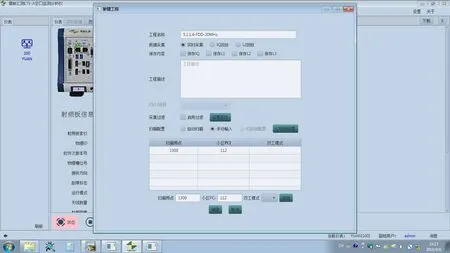

以FDD模式为例,配置基站带宽为20 MHz,辅助被测终端接入该小区,小区配置信息如图6所示。

图6 小区配置信息

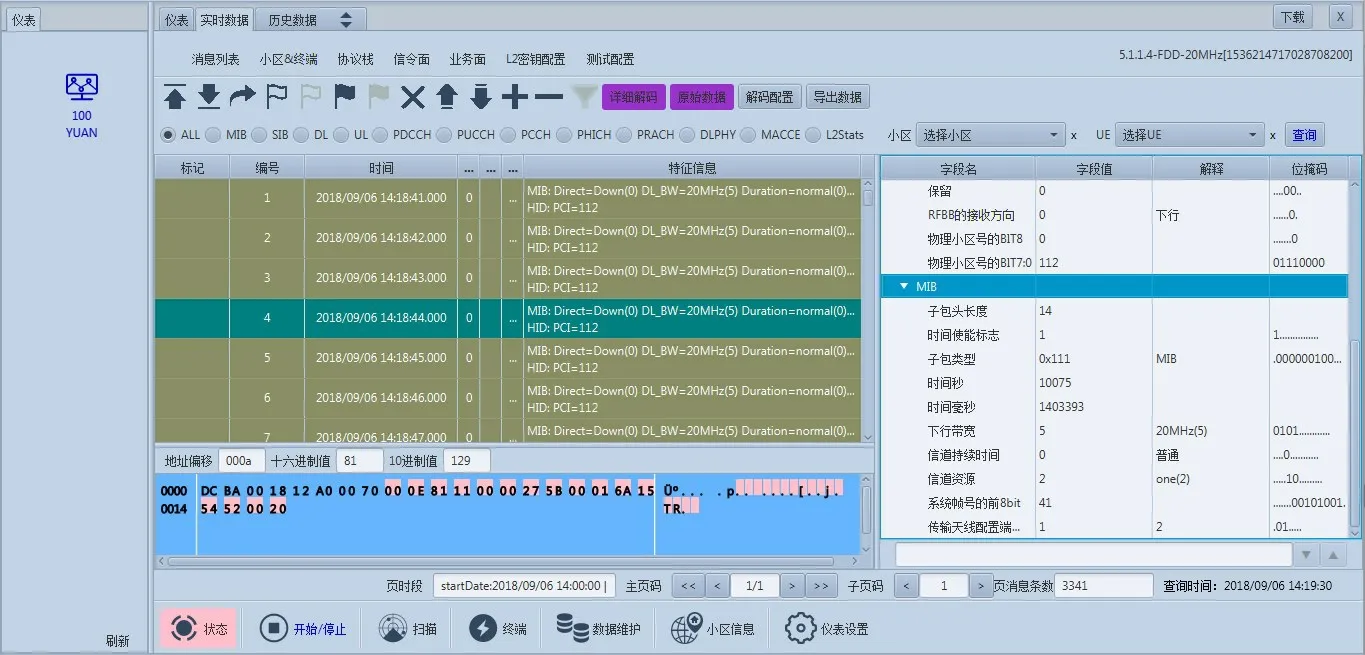

图7 仪表解析出的MIB信息

图7为LTE-A空口监测仪解析出的MIB信息,解析出的16 bit MIB信息为1010100010100101,其中下行带宽掩码为101,表示下行带宽为20 MHz;信道持续时间掩码为0,表示在时域中,每个PHICH组所占的OFDM符号个数均为1;信道资源掩码为10,表示phich-Resource参数为“one”;MIB信息中的systemFrameNumber字段只能传输系统帧号的高8位,系统帧号的前8 bit掩码为00101001;传输天线配置端口参数占2 bit,掩码为01,表示传输天线配置端口为2。

由此可见,LTE-A空口监测仪可正确解析出MIB,验证了下行基带处理流程的正确性,同时也进一步验证了基带板卡整体设计的可行性。

4 结束语

国内对基带板的研究已经日趋成熟,但是目前依然缺少专门对基带板可行性分析的相关资料,而仅限于通过实现来验证其可行性。因此本文提出了在硬件设计之前对可行性进行分析,防止在实现时芯片资源不足而导致人力和时间等资源的浪费。本文以LTE-A空口监测分析仪的下行基带板为例进行可行性分析,主要分析FPGA、DDR3、mSATA以及PCIe总线相关的可行性,经过最终测试证明了本文提出的可行性分析思路的正确性。本文的研究内容不仅确定了LTE-A空口监测仪中基带板的芯片选型,大大降低了基带板设计的风险,同时也为其他硬件的芯片选型提供参考。