高频宽带延迟线的设计

2020-02-05许在运

许在运

(合肥工业大学电子科学与应用物理学院 安徽省合肥市 230009)

延迟线是一种将电信号通过某种介质材料来延后一段特定时间的元件或器件,为了满足现代电路及各种汇总器件的延迟需求,常采用延迟线来进行电路设计。当电信号通过某一延迟单元后,会将电信号延迟一段特定时间后输出。

近些年随着微波集成电路的不断发展,延迟线的应用也更加广泛,比如在相控阵雷达系统、信息对抗中,延迟线的使用也显得越来越重要。在设计延迟线时,尽量使其具有良好的幅频特性,衰减量小、起伏和色散要尽量小,在满足良好的阻抗匹配的同时还需要具有一定量的相移特性。同轴电缆延迟线、声体波延迟线、超导微波延迟线、光纤延迟线等,这些传统的延迟线普遍存在体积过大的缺点。延迟线采用共面波导曲折传输线的布局方式以及偶模的电磁场模式,有利于消除共面地之间电场的形成条件,减弱宽带大信号波束指向的偏离,与传统延迟线相比,这种延迟线更适用于现代雷达系统。

共面波导微波传输线最早是由学者C.P.WEN 于1969年提出,其后共面波导延迟线越发地被人们所设计和使用。2016年合肥华东电子研究所的汤艳燕等人设计研制出了一种共面波导延时放大组件。然而,目前国内外对高频下这种延迟线的指标特性研究较少,为此,本文设计了一组4 位共面波导延迟线,分别可产生1 λ、2 λ、4 λ、8 λ 的延迟量,工作频率在Ku 波段,相位线性度优于2°,器件同时还具有小型化、低色散等特点。

1 共面波导传输特性

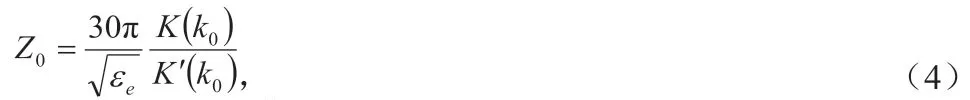

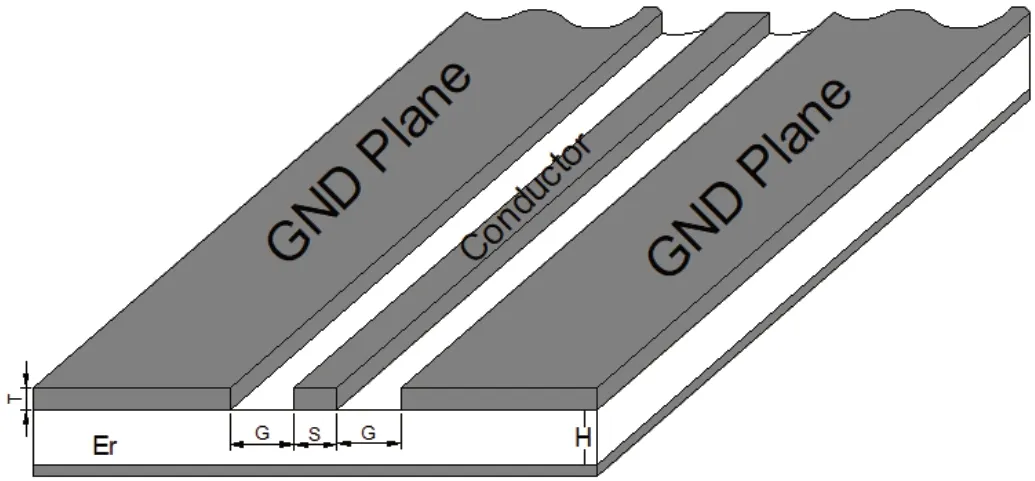

本文中延迟线采用的是共面波导平面传输线,它的基片正面是由一中央导带和两边共面的金属接地板构成。如图1 所示,共面波导由厚度为 H,介电常数为Er 的介质基片和厚度为H 的表层金属构成。其中,中央导带与两边共面的金属接地板之间的缝隙宽度为G,中央导带宽度为S,底部的金属接地层起到增加电路功率容量和电路片散热的功能。

共面波导的导波相速度vp可以表示为:

式中:c 为电磁波的在空间中的传播速;εe为共面波导的介电常数。

共面波导的波导波长λg为:

式中:f 为工作频率;λ0为自由空间中的波长。

则由两条射频支路产生的射频信号的相位延迟量 为:

共面波导的特性阻抗Z0为:

图1:共面波导模型

由于,共面波导传输线的色散特性与其导带线宽、缝宽和介质厚度有关,所以在构建50 欧姆共面波导传输线时需通过HFSS 等工具进行计算;另外,在共面波导传输线之间添加适当的接地孔,能够减弱一定量的信号间串扰,因此在布局时,共面波导传输线电路可以设计得更加密集,有利于解决尺寸过大的问题。

2 共面波导延迟线设计

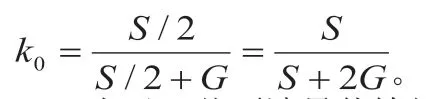

下面简单叙述下共面波导延迟线的设计过程。1 λ、2 λ、4 λ、8 λ 共面波导延迟线采用曲折传输线的形式设计,基于薄膜工艺基础,采用Al2O3为基片材料,介电常数为9.8,基片厚度为0.254 mm,基片表面镀金厚度为4μm,通过使用ADS 自带Linecalc 计算工具,计算出线宽为0.1 mm,缝宽为0.05 mm,采用圆弧形切角方式,通过电磁仿真软件在工作频带上的仿真,得出1 λ、2 λ、4 λ、8 λ 共面波导延迟线三维仿真模型如图2 所示,延迟线上下面采用接地孔贯穿,有效地保证在较低损耗下具有较低的色散特性。

3 仿真结果与分析

通过上一章节分别对四个共面波导延迟线进行枝节长度的优化和传输线的布局,最终得到1λ、2λ、4λ、8λ 的共面波导延迟线的仿真结果如图3 所示。

从图3 可以看出,由于共面波导的电长度不同,1 λ、2 λ、4 λ、8 λ 中心频点插入损耗分别为0.4dB、0.8 dB、1.8 dB、3.7 dB,输入输出驻波比均小于1.2,相位线性度优于2°,带内起伏优于0.5 dB。在如此高频特性下,由于各端口之间金丝阻抗匹配、射频信号的不连续性等原因,都会导致插入损耗变大,并会对延迟线的输入输出驻波造成一定的影响,所以在后续的设计中还需要进一步完善和优化。

本文通过对不同延迟量的共面波导延迟线进行仿真计算,采用曲折传输线的方式,实现了延迟线的小型化特点。与传统延迟线相比,共面波导延迟线,因其小型化、集成度高、低插损、低色散等优点,更适用于现代相控阵雷达等系统中。

图2:共面波导延迟线仿真单元

图3:共面波导相移特性