局域无线时间同步系统伪码测距环路优化

2020-01-17湛小蕾刘音华张慧君李孝辉

湛小蕾,刘音华,张慧君,李孝辉,4

(1.中国科学院 国家授时中心,西安710600;2.中国科学院 时间频率基准重点实验室,西安710600;3.中国科学院大学,北京100049;4.中国科学院大学 天文与空间科学学院,北京101048)

0 引言

局域无线时间同步系统具有精度高、设备简单以及布置灵活等优点,在许多重要领域都有着迫切的应用需求和前景。例如,现代军事靶场、无线传感器网络以及大型建筑物内部等都需要点对点、甚至分布式的无线时间同步技术。因此,局域无线时间同步系统的设计与实现具有非常重要的意义。

而以上各领域中的不同系统是由非同源基站组成。当两地信号源无线传输时,非同源时钟导致不同设备所测得的结果存在钟差,无法进行统一的分析与处理。所以高精度无线时间同步作为一种能够为上述各领域场景提供技术支撑与便利的方法,适用于可视距离下的无线时间同步。

本系统是指在低动态环境下多个地面基站相互之间进行伪码测距处理后消除钟差的系统。主要应用于消除有限距离下两测距终端的钟差,对时间进行比对,并对钟进行调整,使两测距终端时间同步。在此环境下,为改善同步精度,基于双向伪码测距原理可知双向同步精度与跟踪环路精度息息相关。故通道的环路结构会导致跟踪环路无法正常工作,积分时间、环路带宽、载噪比等环路参数也会影响跟踪环路的测量误差与跟踪精度[1]。因此本文首先通过研究通道结构来改善跟踪精度,其次为适应低动态环境,本文分析了环路参数与跟踪环测量误差的关系,以便对环路进行优化,从而降低测量误差,改善同步精度。

1 双向伪码测距原理

局域无线时间同步系统是指在两地面站安装信号发射装置和接收装置进行测距信号互发互收的系统。利用伪码测距原理在两测距终端分别以自身时钟为基准发射前向测距信号和反向测距信号。其中一端通过跟踪计算得到本地伪距,并从跟踪到的电文中解析出异地伪距。该测距方法中,前向测距信号和反向测距信号路径相同但方向相反,可最大限度地消除由传播路径延迟引起的误差,从而实现两测距终端的高精度时间同步[2-4]。双向单程伪码测距如图1所示。

图1 双向单程伪码测距

如图1所示,设r为A、B两端的真实距离,光速为c,δtSA为A端的发射通道时延,δtRB为B端接收通道时延,δtA-B表示A、B两端时钟的钟差,两端都以1PPS上升沿为计时起点且TB、TA分别表示B端的本地时间和A端的发射时间,那么根据无线传输,本地时间减去发射时间后只剩下电波的传输时延和两地的钟差,故可得到式(1):

根据伪码测距原理,可得伪距ρ=(TB-TA)×c。设δtB-A=-δtA-B,同理,A、B两地互发互收的伪距方程如下式(2)和(3)所示:

两地的钟差可以通过伪距与两地的几何距离、收发通道时延求差得到。式(2)和(3)等号两边分别求差,得到时差双向计算公式,如式(4)和(5)所示:

式(4)和(5)中,1ρ、2ρ分别代表A端和B端的伪距测量值。

在A、B两地的无线收发装置相同的情况下,式(5)中的收发通道时延差几乎可以忽略不计。因此,可以计算得到两地的钟差δtB-A。已知限制伪码测距精度的因素有两个:伪码码元宽度和接收机的跟踪精度[5]。在低动态速度为10 m/s环境下,为达到时间同步精度为ns级以下的指标,本文通过减小码宽采用5.115 MHz的码元信号来增大测距精度,同时通过分析码环路以及优化跟踪环路参数来提高跟踪精度。

2 环路结构分析与优化

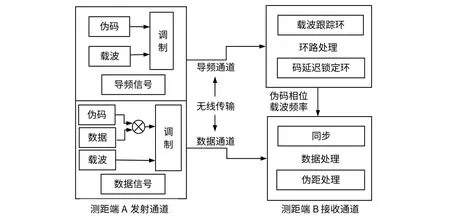

局域无线时间同步系统的发射端采用5.115 MHz的伪码以及5 kb/s的数据率。若在发射通道中采用传统单一的信号调制方式,即扩频码上调制时间同步电文数据,然后在载波信号上调制扩频码信号,那么接收通道在数据跟踪时,相干积分过程会受到电文数据比特位翻转的限制,故最大预检积分时间只能与电文比特时间一致,所以只能设为0.2 ms,否则就不能保证跟踪环路锁定。且0.2 ms的预检积分时间使信道载噪比降低,误码率增大,使传输数据在接收端难以解调。传统单一的通道跟踪结构如图2所示。

图2 传统单程测距信号环路模型

对比图2的传统环路,为增大载噪比并成功解调数据,在无线时间同步跟踪环路中,采用双通道辅助环路结构。双通道辅助环路结构中发射的中频信号由不调制任何数据电文的导频信号和数据信号组成,且两者严格同步。因此在仅跟导频通道信号的条件下,不受电文比特翻转的限制,预检积分时间变长,使跟踪通道载噪比增大,从而提高跟踪精度。下图3则为导频通道与数据通道整个跟踪环路的设计结构。

图3 无线时间同步系统单程测距信号环路模型

如图3所示,测距端A的发射通道中包含同相的导频和正交的数据两条信号支路,其中两条信号支路中的伪码采用码分多址的方式。在测距端B的接收通道,由于预检积分时间较长,能够在高载噪比的条件下跟踪导频支路信号,计算出本地载波频率以及相位。然后,数据支路通道根据本地载波频率以及相位进行数据解调以及伪距处理。

3 环路参数选择

在信号收发处理器中,伪距观测量是根据码跟踪环环路对发射信号的同步跟踪而获得的。因此,码环路的跟踪误差是伪距测量误差的直接来源。所以在低动态环境下,选择合适的环路参数使伪距测量误差可满足指标要求,对地面基站之间的收发信机测距准确度和稳定度也至关重要。与此同时,可通过式(5)求出更加精确的钟差,从而对两地的时钟进行调整。

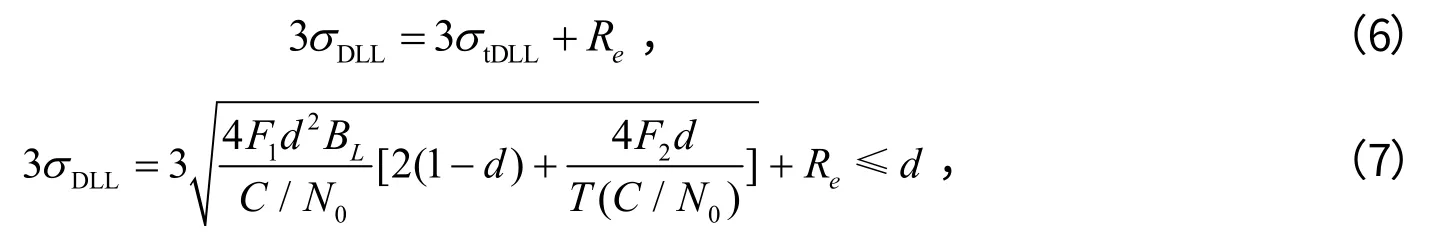

3.1 码环跟踪误差

在局域无线时间同步系统中,码环的跟踪误差主要是由两部分组成:热噪声造成的热噪声颤动误差以及由多普勒或设备间相互运动引起的动态应力误差[6]。由于该系统是在低动态环境下测试,设置动态速率为10 m/s。码环经验方法门限是由环路所有的误差源造成的抖动的3σ值,其值不允许超过鉴别器线性牵引范围的一半所计算的,所以码跟踪环的跟踪门限值经验确定方法为:跟踪误差的码片的3σ颤动不能超过码片数表示的相关器间隔[7-11],即:

式(6)和(7)中,σDLL为码跟踪误差的均方误差;σtDLL为的1σ热噪声码跟踪颤动;Re为跟踪码环的动态应力误差(静态环境下忽略);F1和F2为码跟踪环鉴相相关因子,一般取值为1/2;C/N0为载噪比(rad/Hz);BL为环路滤波器带宽;T为环路更新时间间隔;d为超前和滞后伪码码片间隔。

由于码片速率比载波速率低的多,通常利用载波环测得的多普勒频移辅助码环,以消除码环中的动态误差,这有利于码环在非常窄的噪声带宽下进行伪距测量,进一步降低码环的热噪声颤动[12]。因为码片的最大相关是0.5码片,取码片间隔 0.5d=,根据以上因子可简化得到二阶码跟踪误差造成时间抖动公式为

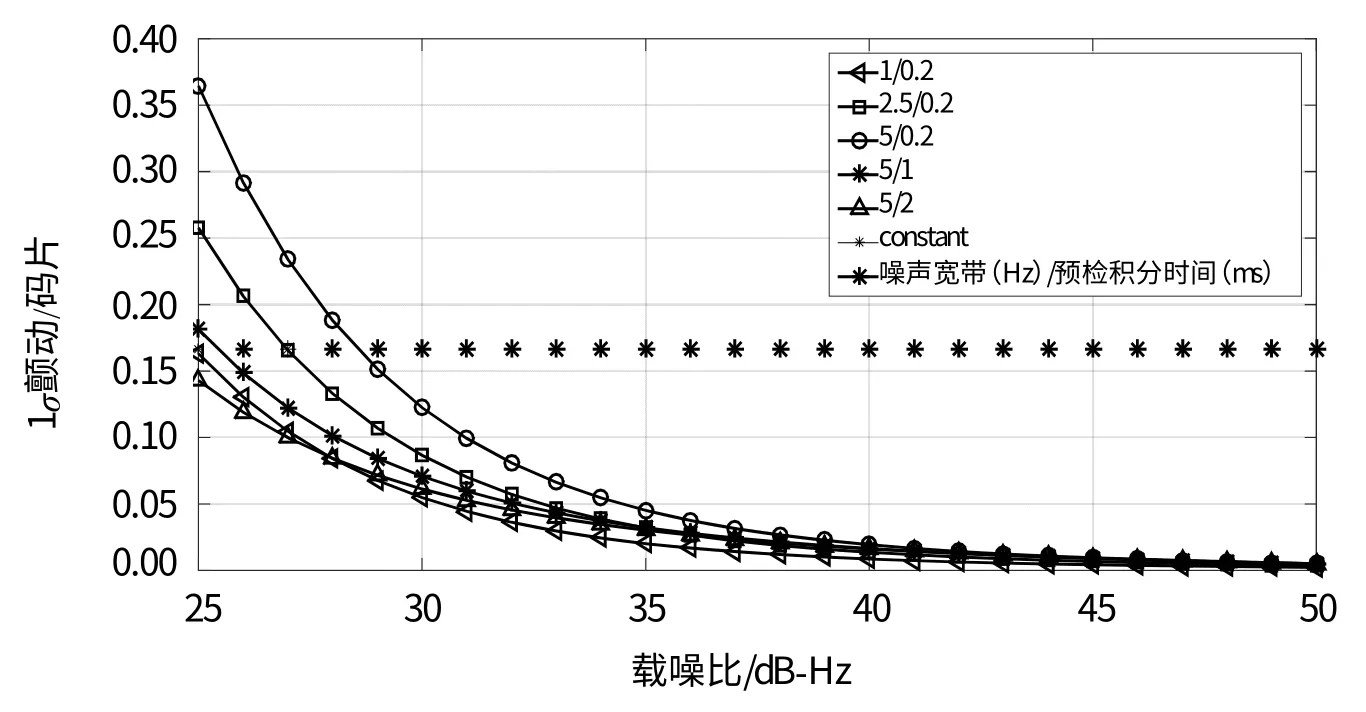

因环路采用导频辅助数据结构,故可将积分时间提高,本文选取积分时间T=1ms=1×10-3s;当取码环路带宽BL=0.5Hz时;因为码环误差随载噪比的升高而降低,根据实验经验值,取载噪比为50 dB,即式中C/N0的取值转化成功率之比为105;因此计算得到码测量误差为σDLL=0.00224码片,已知码片宽度对应的时间为,Fc=5.115MHz为伪码的码片速率;c为光速,可以计算得到的码测量误差时间为0.438 ns。在忽略其他因素导致的测距误差下,理论情况总的测距误差精度适用于同步系统之中。不同环路参数下二阶码环跟踪环测量误差与载噪比的关系如图4所示。

由图4可知,在低动态环境下码跟踪环码片颤动与载噪比、预检积分时间以及环路等效噪声带宽密切相关:载噪比随着预检积分时间的减小而增大,使得环路的1δ热噪声码跟踪颤动增加,从而导致测量误差增大;当测量误差限定在跟踪门限内时,测量误差随着环路带宽的减小而减小,随着预检积分时间的增大而减小。以下对预检积分和环路带宽进行分析与优化,减小热噪声,提高码环路的测距准确度的同时改善同步精度。

3.2 环路参数分析与优化

增加载噪比0/CN,减小环路带宽都会减小热噪声,增加预检积分时间会减小平方损耗,从而也减小了热噪声[13]。与此同时,预检积分时间可通过双通道辅助跟踪结构来增加,环路带宽可通过载波环辅助码环来减小,故为了减小热噪声提高测距精度,以下主要对预检积分时间和环路带宽参数进行了分析与优化[14]。

3.2.1 预检积分时间

与单通道的跟踪结构相比,双通道辅助跟踪结构因导频通道只调制伪码,故不存在数据的比特翻转问题。而双通道在不考虑比特翻转的情况下,可适当增加预检积分时间,提高信噪比,改善跟踪精度。图5对积分时间分别为0.2 ms的单通道、1 ms的单通道及1 ms的双通道下的环路跟踪结果进行了分析。

图4 不同环路参数下二阶码环跟踪环测量误差与载噪比的关系

图5 不同积分时间下单通道和双通道跟踪结果

对图5分析可知,当设置预检积分时间为0.2 ms,单通道跟踪成功,即时支路相关值与超前、滞后相关值比例为1.3倍,增大预检积分时间为1 ms,由于比特翻转,单通道跟踪完全失锁,而双通道辅助跟踪环路在只跟导频通道的情况下即时支路相关值远大于超前、滞后支路相关值,比例为2倍。由公式(8)与图4可知增大预检积分时间的同时可提高环路的载噪比。但预检积分时间持续增加,环路参数更新率下降,多普勒偏移值无法及时获取,因此本系统的预检积分时间选取适当值为1 ms。

3.2.2 环路带宽

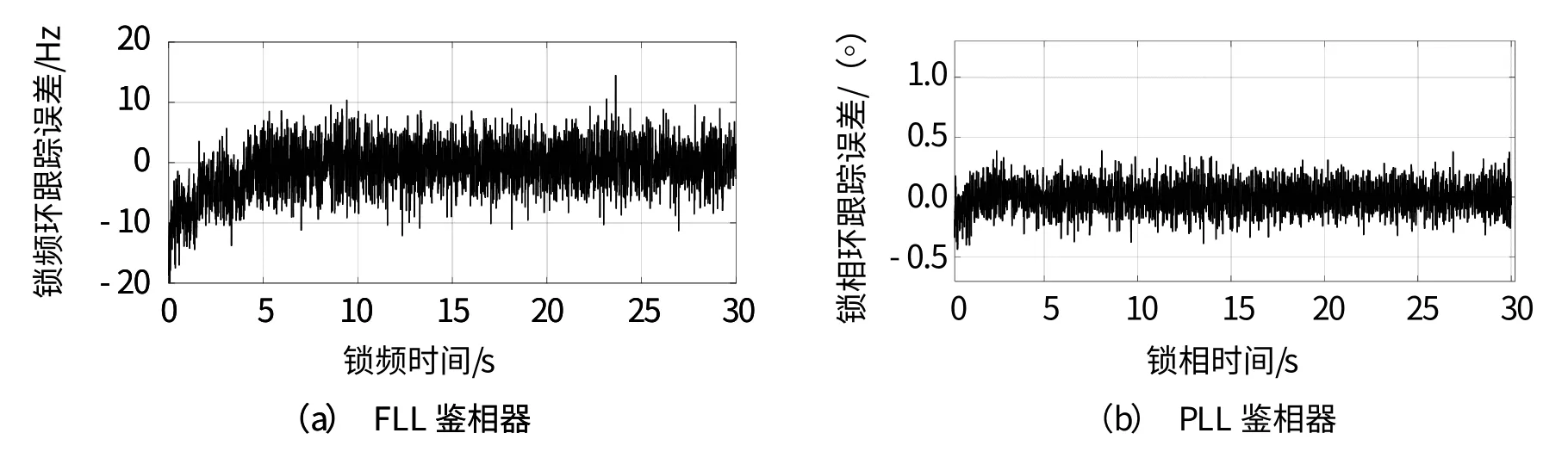

基于无线时间同步伪码测距的基本原理,无线时间同步系统的同步精度只跟伪码跟踪环路有关,故本小节只对不同的码环路带宽进行比对。但在对码环环路带宽进行仿真的前提下对载波环环路带宽进行仿真,确定载波环路带宽。如图6所示,数据为同步系统的同步数据,动态设置为10 m/s,锁频环带宽设为10 Hz,锁相环设置为15 Hz,可得到如下的跟踪结果[15]。

图6 载波跟踪环路曲线

图6中,锁频环消除了绝大部分不稳定状态,在含有噪声的情况下只剩下5 Hz左右的频率偏差。锁相环在此基础上能够稳定跟踪频率相位,使得剩余相位误差约等于0。如果锁相环单独工作,可计算得到相位误差为1.8712°[16-19]。

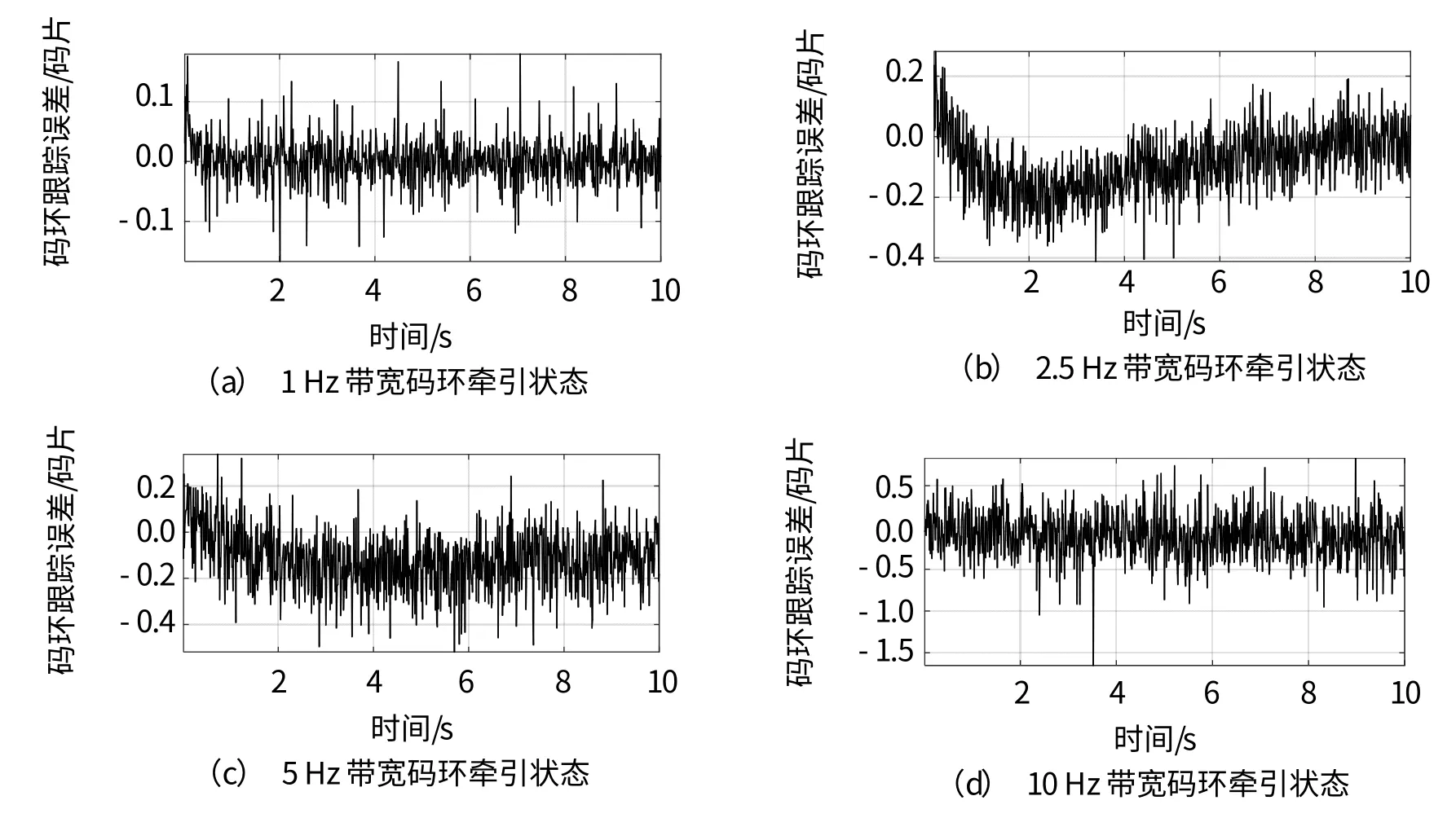

为了探讨跟踪环路的可行性,以及在不同环路阶数和环路噪声带宽等情况下的性能,在Matlab中对跟踪环路进行了仿真。下列仿真数据环路直接采用二阶锁频辅助三阶锁相跟踪环,伪码码速率选为5.115 MHz,以及带纠错编码的5 kb/s电文来提高伪码跟踪精度。收到的仿真数据采样率为62 MHz,信号功率为0.5 W。不同带宽码环跟踪误差示于图7。

图7 不同带宽码环跟踪误差

由图7码跟踪环路噪声带宽对环路牵引状态的稳定分析可知:较宽的环路带宽能够使环路稳定较快,但是却存在较大的环路跟踪误差;反之较窄的环路带宽能够保证更高的环路跟踪精度和更小的稳态误差,但是却需要较长的稳定时间[20-24]。因无线时间同步系统侧重点在测距精度上,所以环路的稳定时间本文忽略不计。不同带宽码环跟踪误差结果示于表1。

表1 不同带宽码环跟踪误差结果

码环的跟踪误差是伪距测量误差的直接来源,选择合适的环路噪声带宽使伪距测量误差满足接收机的设计指标要求,是伪码跟踪环设计的重要环节[25-28]。在动态较小的收发信机中,通常要求码环跟踪误差小于0.1码片甚至更低,根据表1的仿真结果此时一般要求环路噪声带宽小于5 Hz。

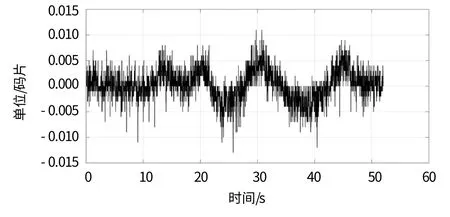

图8 码环路带宽为0.5 Hz下伪码环路滤波器输出

按照上述环路参数,在低动态接收发信机中通过DSP向Flash写环路滤波器输出参数。从式(8)跟出来的码跟踪误差结果可知,伪码环路滤波器输出值的波动范围在-0.01~0.01码片之间,符合表1得到的仿真结果,根据码片与码速率关系可计算出波动误差为-5~5 ns之间。

4 结语

综上所述,本文在局域低动态环境下基于双向伪码测距原理对环路跟踪误差进行了分析与仿真。根据影响跟踪精度性能的关键性因素,可知单一环路结构或环路参数设计在局域低动态环境下并不能获得良好的跟踪性能,因此本文主要从环路结构与环路参数入手。通过以上环路结构的研究,提出了导频辅助数据通道的双通道结构,并将预检积分时间从0.2 ms提高到1 ms,减小了平方损耗,从而减小了热噪声,最终减小了跟踪误差。与此同时,对跟踪环路的积分时间、环路带宽参数进行了性能仿真,提高载噪比与跟踪精度,最终改善同步精度。在对环路误差分析后,选取环路结构锁相环和锁频环带宽分别为15 Hz和10 Hz,码环路采用环路带宽为0.5 Hz二阶码环。