基于AD9914的频率合成信号源设计与实现*

2019-11-28季忠健

季忠健

(中国船舶重工集团公司第723研究所 扬州 225001)

1 引言

信号源是现代电子系统的重要组成部分,它可以为电子系统提供宽频带,高稳定度,高精度的各式调制信号,广泛应用于各式电子系统之中。它的输出信号品质的好坏直接决定了整个电子系统的性能优劣,因此如何设计稳定可靠且性能优越的信号源,一直是相关领域的研究热点。得益于数字信号处理技术和集成电路技术的快速发展,采用DDS技术的信号源性能指标得到了极大的提高,在电子系统领域也得到了广泛的认可和应用[1]。本文基于目前比较新型的AD9914芯片对DDS信号源进行了开发应用与研究[2~3]。

2 DDS技术原理

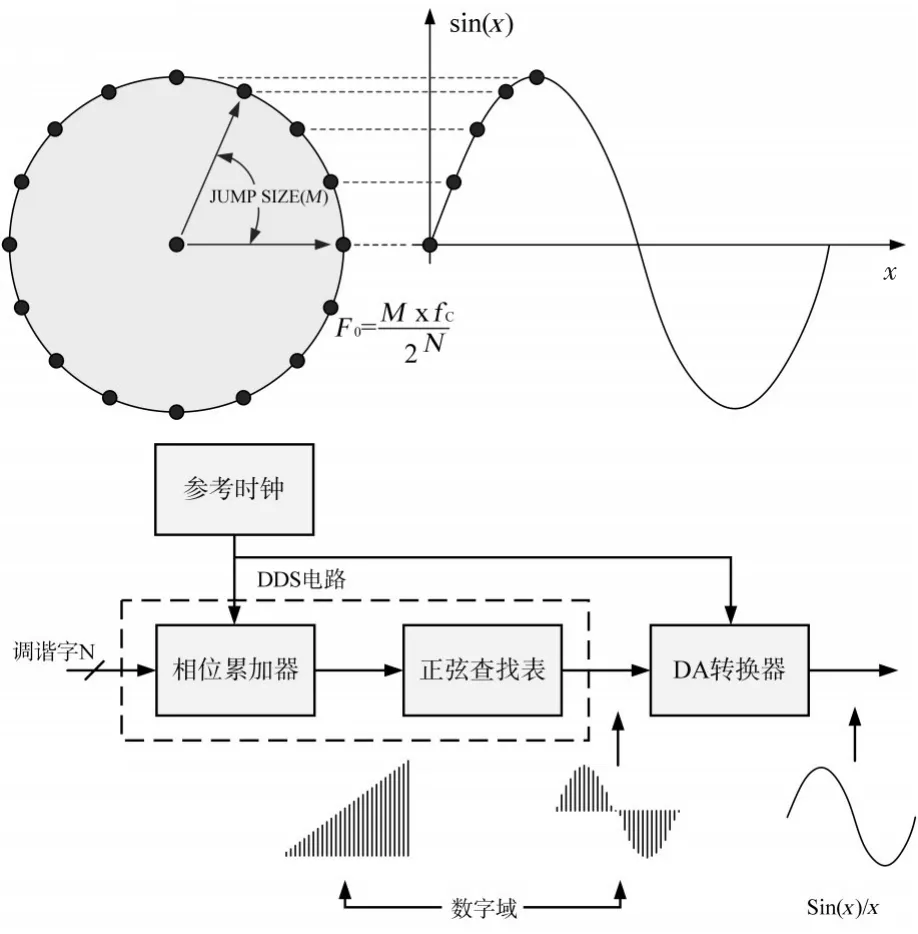

连续的正弦时间信号具有周期为2π的重复角相位范围。根据这一特点,就可以采用处理数字信号的方式,利用计数器来作为DDS目标频率信号的相位轮。如图1所示,将正弦波振荡看作围绕相位轮旋转的矢量。相位轮上的每一个指定点对应于正弦波周期上的一个等效点。当矢量围绕相位轮匀速旋转时,对应的时间轴上便会产生一个相应的正弦波。计数器步进距离对应相位轮的旋转角度,当步进距离增大时,旋转角度增大,则对应产生的正弦波周期减小,从而增大信号输出频率[4]。

如图1所示,DDS技术的物理实现主要包括如下的几个主要单元:相位累加器、一种相位幅度转换方法(通常是正弦查找表)和一个数模转换器[5]。

相位累加器即存储并累计相位值的计数器,在一个时钟信号下,相位累加器按照设定的步进距离(M)进行一次累加,并将累加值作为寻址地址进行查表,相位累加器的位数(N)和步进距离共同决定了最终的信号输出频率。

ROM查找表为存储器单元,存储着经过数字化处理的正弦幅度值序列,幅度值序列的寻址地址与相位累加器的值一一对应。由正弦信号的特性可知,正弦信号的完整波形可以由1/4周期的波形信号通过镜像方式完整表述,因而实际ROM查找表只存储1/4个正弦波量化幅度值信息,这样在有限的容量内大大提高了最终输出信号的分辨率性能。

图1 数字相位轮示意图及DDS工作原理图

数模转换器可以将表中读取的量化幅度值转换成连续模拟信号。

3 指标与设计分析

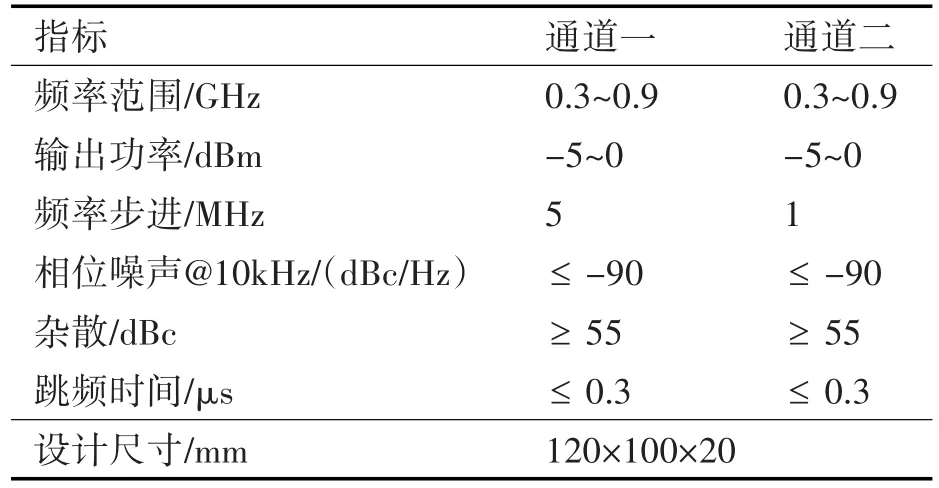

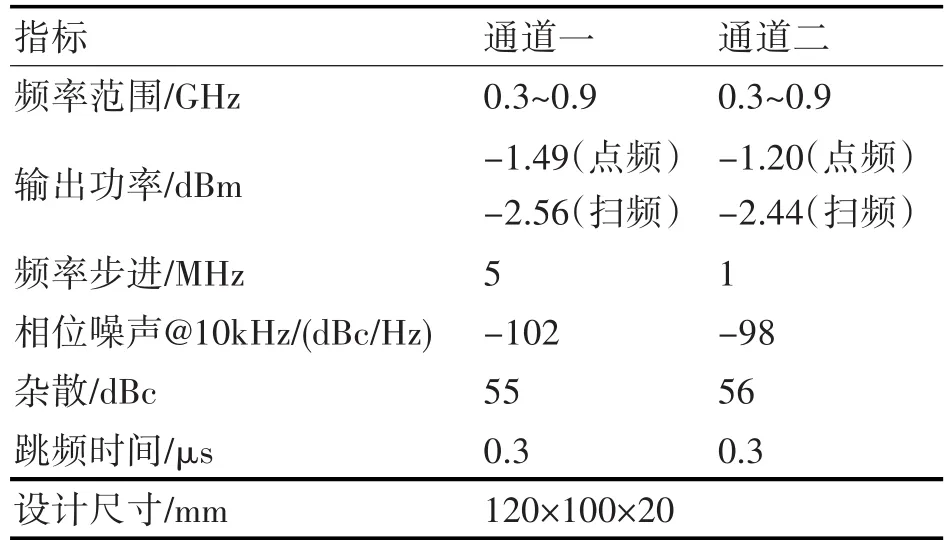

根据雷达系统的应用需求,需要两路射频信号输出,并且具有同步时钟,对信号源指标的具体设计要求如表1。

表1 指标要求

3.1 硬件设计

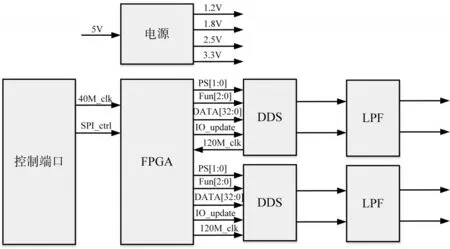

根据设计要求,需要两路射频信号输出,因此设计方案采用了FPGA+双DDS的结构,系统设计结构图如图2所示[6~7]。

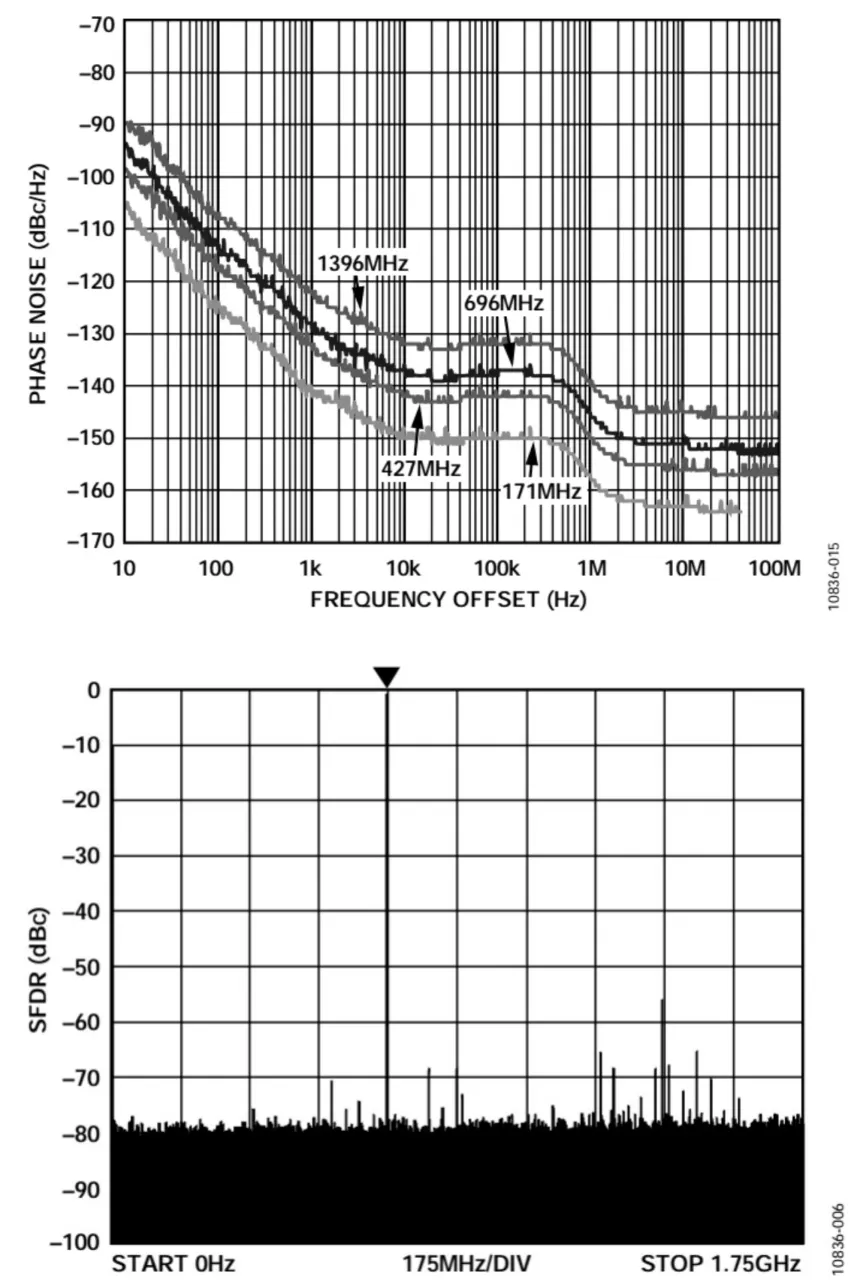

输出的信号频率需要达到0.9GHz,根据根据奈奎斯特采样定律结合输出信号质量的问题,最高输出频率取0.4倍参考频率,因此工作参考频率需达到2.3GHz。因此采用工作频率在3.5GHz的AD9914作为频率合成芯片[8],该芯片具有48位的相位累加器,频率调谐分辨率为190pHz且宽带SFDR大于50dBc;支持频率、相位或幅度的高度线性扫描控制,调制方式灵活。根据参考手册,可以看到该芯片在工作频段内的相位噪声小于-130dBc/Hz@10kHz,杂散指标优于60dBc,满足信号源的设计需求。

图2 系统功能模块结构图

图3 宽带SFDR和相位噪声曲线

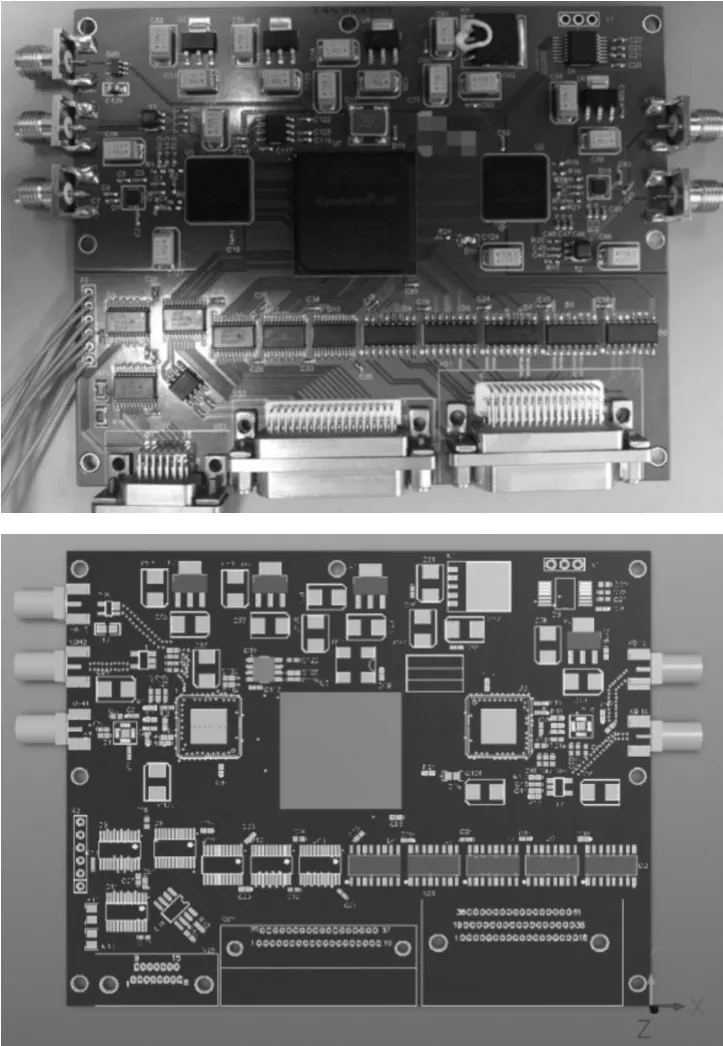

因设计要求跳频时间小于300ns,而AD9914的跳频时间算上传输延迟可以控制在90ns以内,因而对于控制信号的速度要求比较高,本方案采用FPGA作为控制器,FPGA作为一种硬件逻辑设计芯片具有并行执行的特点,相对于DSP,单片机等主流控制器具有更短的响应时间,本文采用Altera公司CycloneⅢ系列的EP3C40F484作为控制芯片[9],该芯片具有40000个逻辑单元(LEs),最大用户I/O为535,单个AD9914器件的控制位需求数量位为50个,满足对双DDS工作模式的控制需求。同时以其中一个DDS的输出信号(SYNC_CLK)作为整个系统的同步信号,分别给FPGA和另一个DDS芯片提供同步工作的时钟。信号源设计的PCB模型图及实物图如图4所示。

图4 DDS信号源模型及实物图

3.2 软件设计

软件设计由SPI接收模块,控制字生成模块和并行控制模块三部分组成。该信号源通过14对422差分信号传输控制报文,FPGA负责接收报文并读取DDS的配置信息。对于DDS的控制信息主要是频率,相位和幅度字。根据参考手册,AD9914的输出频率(fout)由频率调谐字(FTW)控制,fout、FTW和 fSYSCLK之间的关系可由以下计算式表示:

其中,FTW是介于0~(231-1)之间的32位整数,表示完整32位变量的低半部,包括从直流DC到奈奎斯特频率 fSYSCLK/2之间的所有频率[10]。通过写FTW值,利用式(1)可获得输出频率值。AD9914的相对振幅范围可由14位振幅比例因子(ASF)进行数字化控制。振幅范围的计算式为

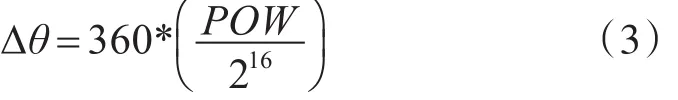

其中,ASF取值为0~(214-1),上面是一个分数,表示输出振幅占满幅的比值。写ASF的值即可设置输出信号幅值。DDS信号的相对相位通过16位的相位偏移字(POW)来控制。相对相位偏移(Dq)可由以下式计算:

其中,Dq的单位是度数,对于任意给定的Dq可利用式(3)计算POW。按照给出的公式可以计算出需要的控制字,部分控制程序如图5。

图5 控制程序

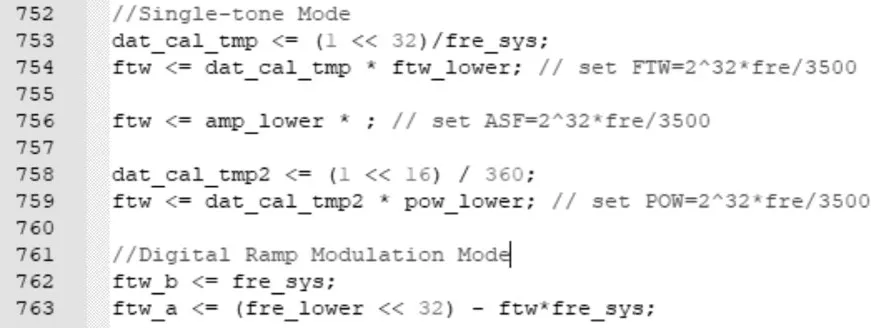

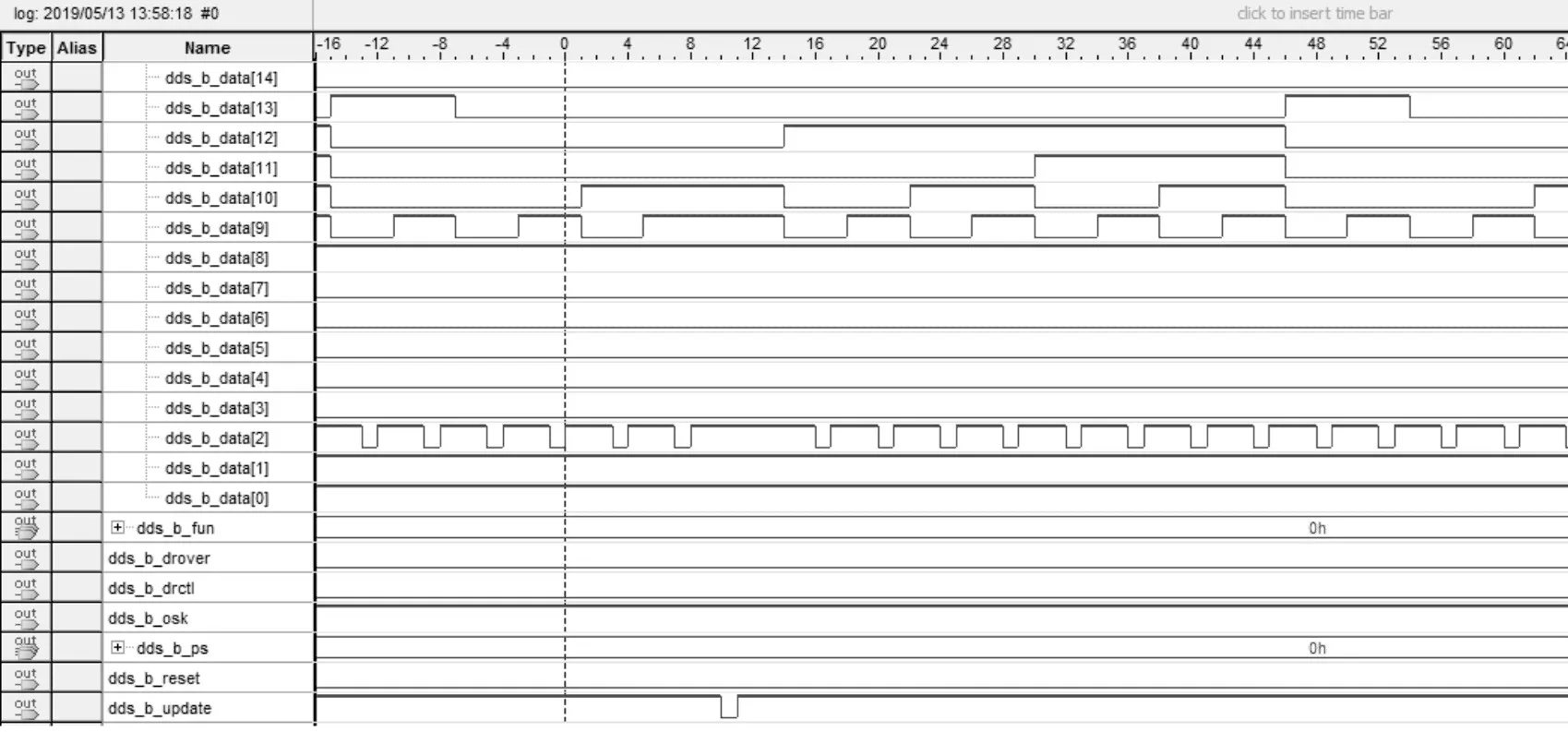

为了减小控制时间,本方案采用了并行I/O控制模式。AD9914支持五种工作模式,根据应用的需求,本方案采用单频和线性扫描两种模式。在单频模式中,信号的控制参数由Profile寄存器提供,AD9914提供了8个独立的Profile寄存器,因此需要单独对PS0~2引脚进行配置,选择需要的Profile寄存器控制信号。在线性扫描模式中,主要的控制寄存器有CFR1,CFR2,数字斜坡上下限值寄存器,正负斜率斜坡的步长和步率寄存器等。为了灵活控制各个寄存器和信号端口,本方案利用状态机模式控制DDS芯片,这样不但可以很好地综合,也使得输出信号的同步性能更好。首先对芯片进行主机复位处理,对所有的寄存器进行清零,恢复为默认值。然后启动DAC校准程序,调整内部DAC时序的建立与保持时间,从而减小DAC底噪。在Signal Tap上捕捉的实时信号图如图6所示。

图6 Signal Tap实时信号图

3.3 杂散指标的分析及优化

DDS技术具有优越的捷变频特性以及较高的相位噪声,这些指标都可以从理论上得到保证,但是由于实际工艺水平的限制,累加器位数,ROM存储空间等都无法到达理想值,因此实际产生的DDS信号会有不太理想的杂散和谐波[11],本方案在设计中主要采用了以下几种方式进行了优化处理:

1)布局及走线的优化。进行数模隔离,利用不同的电源网络供电,中间的公共地采用电阻跨接,尽量减小数字信号串入模拟地,并且尽量避免高频传输线的平行布线,减小相互串扰的影响,并且高频信号链路之间通过增加布线间距和接地孔进行隔离。

2)电源模块处理。在保证能效的利用率,尽量选择LDO电源芯片,LDO相对开关电源来说具有较低的输出纹波,高频杂散较少。在电源的输出口采用磁珠对高频噪声进行滤波,同时在磁珠两侧对地接电容,组成滤波网络。

3)设计优化。后级增加滤波器将带外的杂散滤除,同时落在带内的杂散可以通过增加开关滤波器组进行针对性的过滤[12]。

4 实验结果

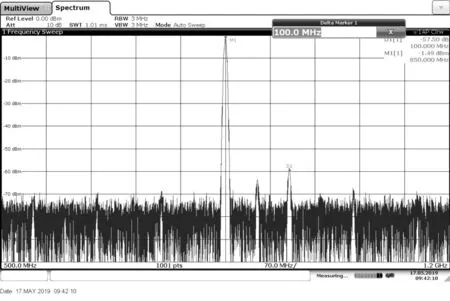

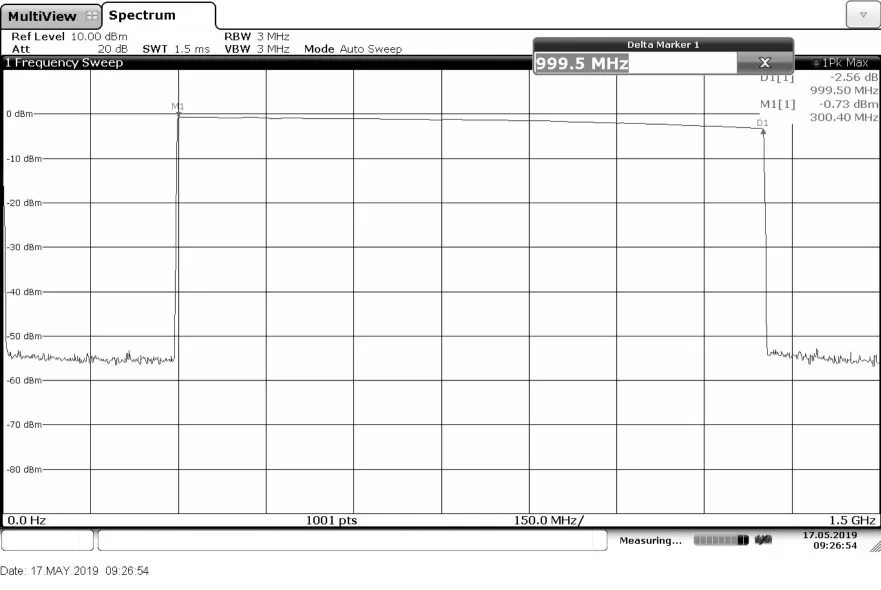

用频谱仪,示波器等仪器进行测试,对于单频工作模式和线性扫描工作模式的关键指标测试结果如图7和图8所示。

图7 850MHz点频实测图

图8 300MHz~1.3GHz宽频带扫频实测图

从实测结果来看,在单频点模式下的杂散效果较好,宽带范围内能够达到55dBc往上,在100MHz内的窄带中则可以达到70dBc的杂散抑制;而对于线性扫频模式来说,从测试结果来看SFDR超过50dBc,也发挥出了器件的性能指标。其余指标测试结果见表2。

表2 实测结果

5 结语

本文围绕目前比较前沿的AD9914芯片进行了信号源电路设计,从最终的实测结果来看,该型信号源无杂散输出动态范围宽,调制方式灵活快速,具备DDS技术的多种优点,实现了一种宽带高速扫频雷达信号源,其中也存在一些设计的不足,在今后的设计中还需要考虑对电路进一步的优化和改善,以期发挥DDS信号源的最佳性能。