基于FPGA高精度多参数传感器存储设备设计

2019-11-20辛海华张会新

张 华,辛海华,秦 丽,张会新

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.北京宇航系统工程研究所,北京 100000)

0 引 言

在飞行器试验中各种参数对飞行器的影响有着非常大的影响,如力学中的压力、过载、振动、冲击、加速度等,这些参数的实时性和准确性直接影响到飞行器试验成功与否,所以一种或多种传感器放置于飞行器的多个不同位置是必不可少的[1]。目前,在飞行器的实验中,多路传感器信号的准确性和精度一直是制约航空航天的一大难题。设计高精度的A/D 采集和高频信号采集,可以有效地提高飞行器的可靠性和准确性。

1 总体方案设计

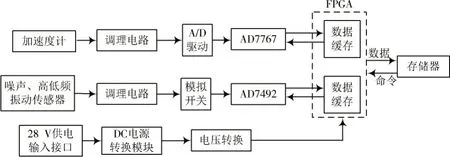

存储设备的设计是基于FPGA 的多路传感器信号实现高精度采集,高速存储,该设备可以对加速度计、噪声传感器、高平振动传感器进行高精度采集。加速度计信号存储设备的设计基于FPGA 的多路传感器信号实现高精度采集,高速存储,该设备可以对加速度计、噪声传感器、高平振动传感器进行高精度采集。

其中加速度计信号转换精度不少于22 位,采样频率为1 kHz,电压输入范围[2]为0~5 V,采用AD7767芯片;噪声、高频传感器不少于8位,噪声传感器信号采样频率为50 kHz,高频振动传感器信号采样频率[3]为10 kHz,采用AD7492 芯片。电源供电由28 V 供电,经DC-DC 转换为5 V,再由电源转换芯片转出3.3 V,2.5 V,1.2 V。总体方案如图1所示。

2 硬件电路设计

2.1 高精度电路设计

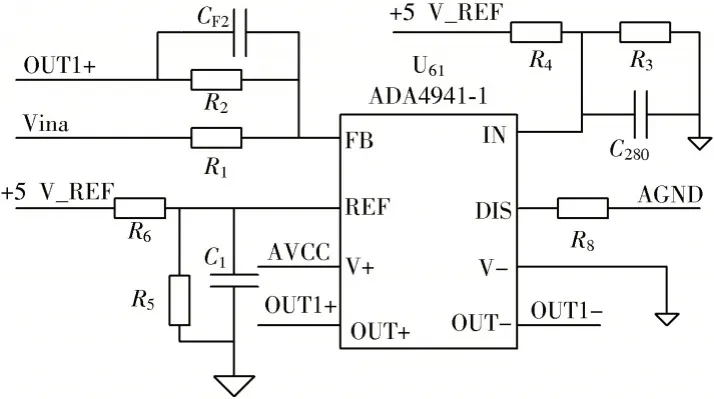

AD7767 在设计中采用全差分驱动,ADA4941-1 具有功耗低、噪声小的特点,非常适合驱动分辨率为24 位的A/D 转换器AD7767。ADA4941-1 由双通道轨对轨运算放大器组成。利用ADA4941-1 与AD7767 组成高精度 ADC 电路,如图2所示。

图1 总体方案Fig.1 Overall scheme

图2 高精度ADC 电路Fig.2 High-precision ADC circuit

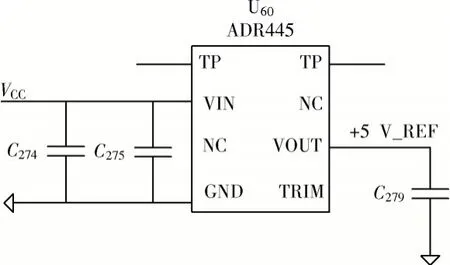

ADR445 具有超低噪声、高精度和低温漂性能,它的输出电压随温度变化程度较低,噪声只有2.25 V 峰峰值[4],这种特性非常适合于高端数据采集系统中的信号转换。采用ADR445 作为AD7767 的基准电压源[5],电路连接原理图如图3所示。

图3 基准电压源Fig.3 Reference voltage source

2.2 噪声、高频信号A/D转换电路设计

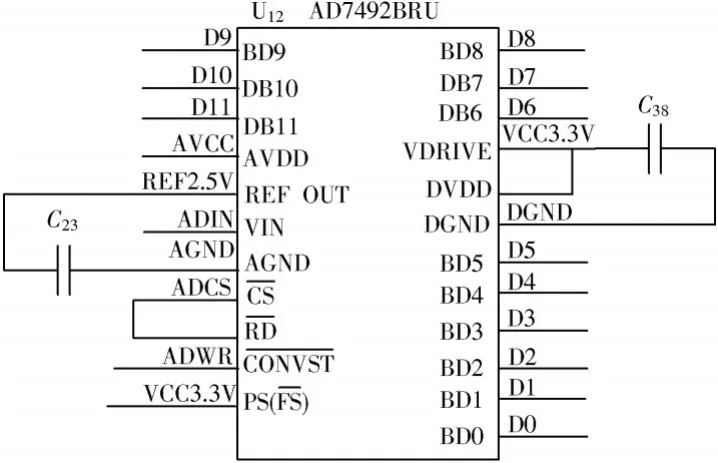

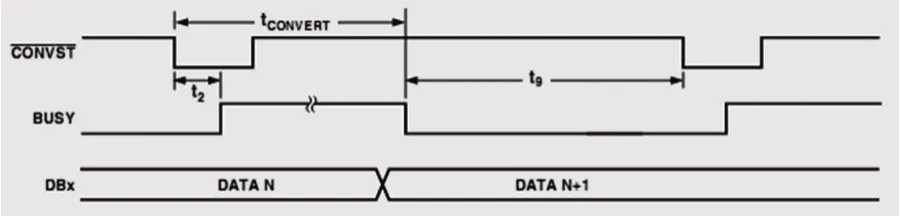

AD7492 负责采集模拟开关ADG706 选通的噪声或者高频振动传感器信号,图4为AD7492 的电路连接原理图。经模拟开关选通后的模拟电压从VIN 管脚输入,信号为启动A/D 转换器的写信号,当A/D 正在忙于进行数据转换时,它的状态通过BUSY 信号显示出来,BUSY 信号即为 A/D 忙信号。DB0~DB11 为 A/D 转换后输出数据[6]。PS(FS)管脚为控制AD7492 工作状态信号,直接设置为高电平,使其处于局部睡眠模式,在一定程度上降低A/D 的功耗。

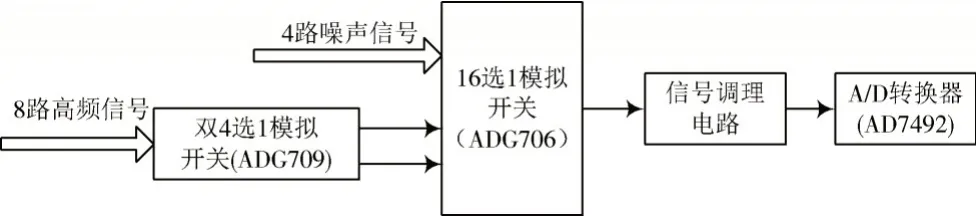

多路模拟开关主要实现对输入端的信号进行切换和选择。采集的信号有4 路噪声信号和8 路高频信号,设计两种模拟开关组对噪声和高频混合信号进行选通,其中4 路噪声信号采用1 片16 通道的ADG706 即可实现通道选择[7],对于8 路高频信号,也可以采用1 片双4 选1的模拟开关ADG709 进行选通。图5为模拟开关组成原理框图。

图4 AD7492 电路原理图Fig.4 Schematic diagram of AD7492 circuit

图5 模拟开关组成原理图Fig.5 Composition schematic of analog switch

2.3 FPGA供电电路设计

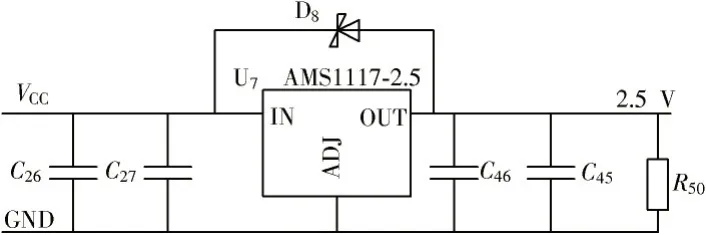

FPGA 供电有2.5 V,1.2 V 和3.3 V。低压差线性稳压电源转换芯片TPS70345[8],它是双通道输出电压,能输出 3.3 V 和 1.2 V 电压。FPGA 的辅助电压为 2.5 V,本设计采用AMS1117 系列稳压源器件AMS1117-2.5,该系列稳压器能输出稳定的2.5 V 电源电压,并且AMS1117的片上微调功能通过自身的调节把基准电压调整误差缩小到1.5%以内[9],同时也具有限流调节的功能,可以尽量减少电源电路或稳压器超载而造成的压力,还可以满足FPGA 对供电电源的稳定性要求,供电模块电路如图6所示。

图6 2.5 V 电压输出电路Fig.6 Output circuit of 2.5 V voltage

3 A/D采集逻辑分析

AD7767 工作的逻辑时序图如图7所示,在第一个MCLK 时钟上升沿到来时对差分输入电压差启动转换,SCLK 是该A/D 器件的串行移位输入时钟,在SCLK 下降沿到来时将转换后的数据串行移位输出。的下降沿指示着A/D 的输出寄存器内有新数据字可用,在允许从SDO 引脚读取输出数据期间保持低电平,不从器件读取数据时信号变为逻辑高电平。在FPGA 从SDO 读出A/D 转化后的数据时,转换结果最高位MSB 在下降沿送至SDO 线,随后转换结果的其余23 位在 SCLK 下降沿逐个送至 SDO 线,FPGA 内寄存器data[23:0]读取数据在SCLK 上升沿读取,对读取到的数据进行编帧,再存储到存储器中。

图7 AD7767 工作的逻辑时序图Fig.7 Logical timing diagram of AD7767

图8 AD7492 工作时序图Fig.8 Timing diagram of AD7492

4 测试结果

设备上电进行数据采集和分析。图9为读取的一帧模拟量数据。模拟量数据的帧头标志位为EB 90,便于查找和分析一帧完整的数据,帧计数用来记录已经采集了的数据量,确保每一帧数据是否连续,保证数据不丢失。0X14 6F 为高频信号小帧标志,用来区分噪声信号、高频振动信号和加速度计信号。存储器对模拟量进行A/D 转换及采集存储后,通过上位机进行回读和软件分析处理,相差小于1 mV,可见加速度计信号、传感器信号的精度已经达到高精度范围。

图9 存储器回读的片段数据Fig.9 Segment data read by memory

5 结 语

本文设计一种以FPGA 为主控芯片的高精度多参数传感器信号存储模块,采用AD7767 作为加速度计传感器信号采集工作核心,AD7492 作为高频传感器信号采集工作核心,AD7767 与ADA4941-1 组成高精度ADC以确保传感器信号的高精度存储,实现多参数传感器信号的高精度存储。通过多次实际测试显示,模块对多参数传感器信号的存储精度高,且具有很高的可靠性,已成功运用于实际工程中。