基于STM32+FPGA的存储控制系统优化设计

2019-11-08孟令军谢玲芳王静波

许 艳,孟令军,谢玲芳,朱 珊,王静波

(中北大学 仪器与电子学院, 太原 030051)

随着图像采集技术的不断发展,对图像的采集存储系统的要求也越来越高,比如军事领域炮弹姿态的获取、飞机飞行过程中的遥测监控、高速公路的路况获取等都离不开图像的采集存储,在实验过程中将运动状态记录下来,为线下的研究分析提供实验依据。因此对存储控制系统进行优化设计也是至关重要的[1]。

传统的数据存储控制系统具有通信复杂,IO资源紧缺,成本高,体积大、功耗高的特点;意外掉电,系统错乱,无法正常记录,并且每次上电记录前都需要擦除FLASH数据,经常擦除会降低FLASH芯片寿命[2],这会使得前期的系统开发效率低下,研发周期较长。因此,针对行业需求,研究并开发了一种基于STM32+FPGA的存储控制系统的优化设计,该系统采用STM32F103(以下简称STM32)作为主处理器,它具有精简指令集以及功耗低、成本低等特点;FPGA作为协处理器可编程逻辑强,并行处理速度快,STM32与FPGA相结合可以实现性能互补,从而提高系统的稳定性。该设计解决了意外掉电存储的问题,在通信复杂、资源短缺的情况下用数据拼接方式进行通信,减少IO口资源的占用,减小体积,使模块趋于小型化,降低电路复杂度,从而降低系统开发成本。该系统还具有可移植性强和可维护性好的特点,可为其他相关系统研发提供一种参考方式。

1 总体方案设计

该系统采用STM32+FPGA的主协处理器进行顶层设计,主要包括三大模块:供电与掉电检测模块、422差分指令的接收、解析、编帧发送模块和数据存储及发送模块。系统框图如图1。

图1 系统组成框图

系统每次上电后等待上位机发送系统开启工作指令,上位机下发指令通过读数盒到STM32,STM32作为主控,完成了422差分指令的接收、解析、编帧、数据拼接方式的指令传输以及电源电压的监控;存储板FPGA接收指令,进入指定的工作状态;当上位机下发启动记录指令时,存储板将外部数据进行编帧存储写入FLASH,上位机下发下载指令时,对存储板进行数据回读,将数据以LVDS的形式发送至读数盒,读数盒转换成USB上传给上位机,存储板在意外掉电时存储每次掉电时FLASH的当前地址[4]。系统工作的主要指令有:自检、复位、启动记录、停止记录、下载、下载取消及容量查询。

2 系统主要硬件设计

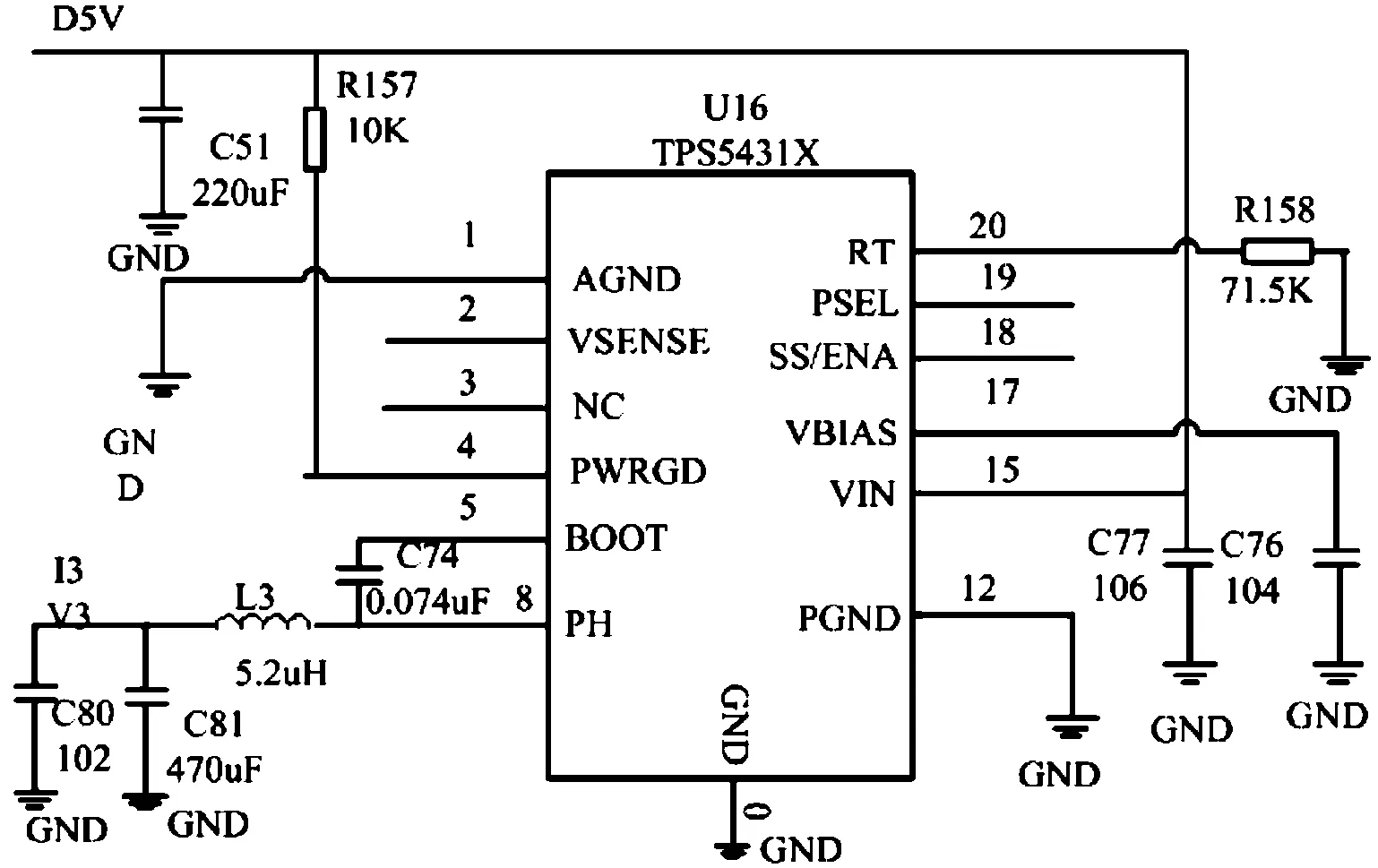

2.1 电源模块设计

该设计的供电系统采用5 V电源适配器供电,控制系统直接采用5 V电源,经过一个肖特基二极管,二极管的作用是防止电流倒灌,这种设计既能减小干扰又不会损坏设备。此外,系统还需要3.3 V、2.5 V及1.2 V电压,分别有开关电源模块TPS54316、TPS54315与TPS54312来输出3.3 V、2.5 V及1.2 V。图2为开关电源模块电路原理图。

图2 开关电源设计原理图

2.2 接口模块设计

存储板和机箱读取盒之间的通信接口采用的是LVDS接口,LVDS接口可以最大限度地减少影响远距离数据传输信号的干扰因素,满足设计系统测试要求。为了便于在恶劣环境中进行测试,应用了性能最好的七类全屏蔽双绞线作为LVDS传输线。这种类型的网络电缆在双绞线的基础上增加了一个高效的屏蔽网络层,可以有效地屏蔽大气颗粒子对信号产生的干扰[5],为方便LVDS线缆拔插,采用了RJ45接口插槽,图3是RJ45网口传输接口原理图、图4是LVDS驱动电路设计原理图。

图3 RJ45传输接口原理图

图4 LVDS驱动电路设计原理图

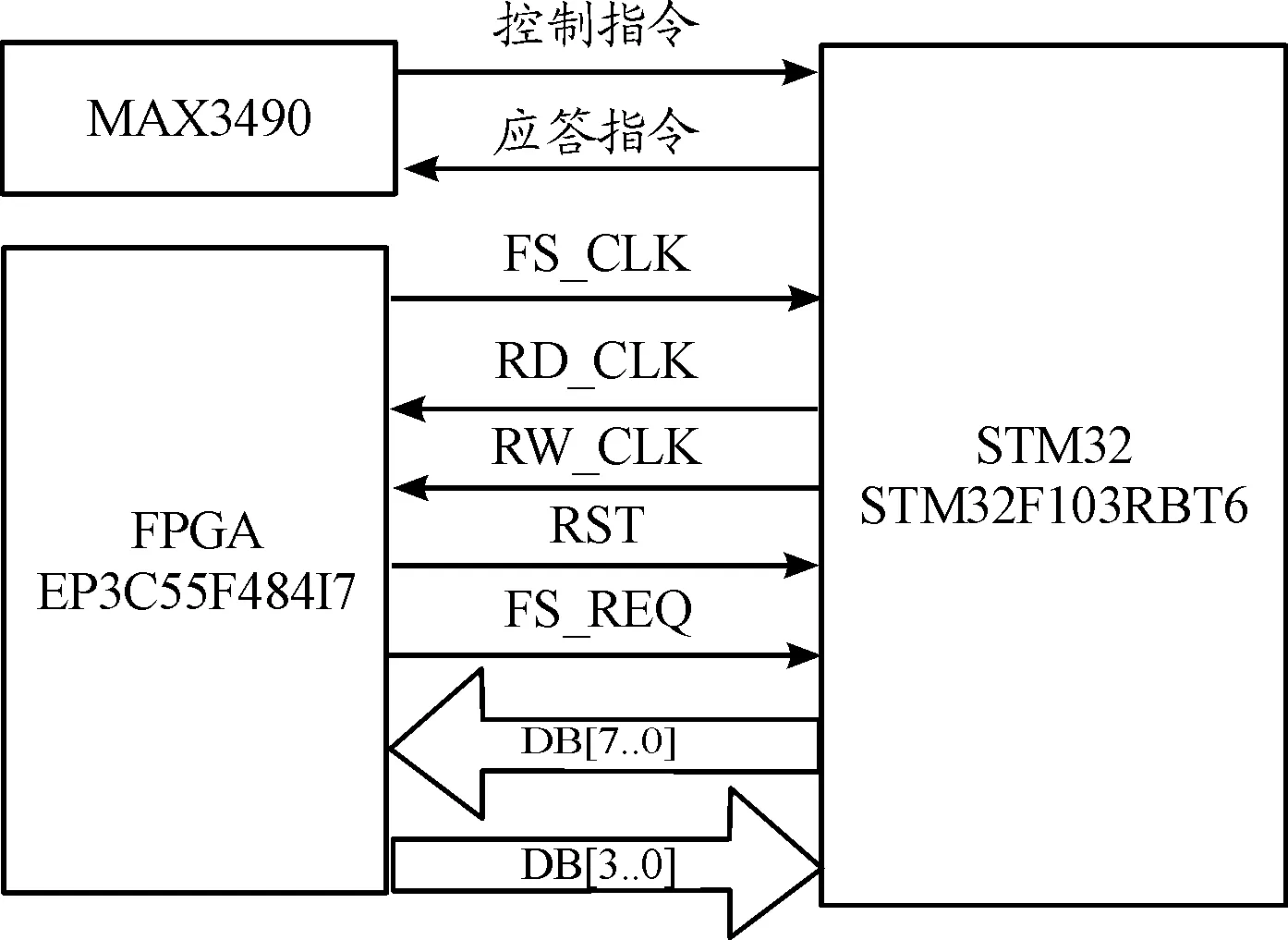

2.3 存储控制模块设计

存储模块主要由四块镁光8Gbytes的FLASH芯片和一块FPGA芯片组成。STM32控制着存储板模块复位、自检、启动记录、停止记录、擦除、下载、下载取消动作,STM32与存储板之间的硬件连接结构示意图如图5所示。

图5 STM32与存储板硬件连接结构示意图

STM32通过8位数据线给FPGA下发指令,FPGA收到指令后会给一个请求信号FS_REQ,之后STM32通过4位数据线回读FPGA给出的数据信息,由于STM32F103引脚较少,存储模块通信复杂,IO 资源紧缺,采用数据拼接的方式接收数据能够有效节约双方的通信资源。

3 系统的软件设计

3.1 掉电监测

电源供电维持着一个电子系统的工作,但并不是关闭电源系统就会立即停止工作。电源关闭后,一般系统都可以继续正常工作数个毫秒或者数个微秒,本系统的掉电检测正是利用系统掉电后短暂的延迟效应,监测系统电源[6]。当STM32监测到供电电压VDD低于阈值时会触发PVD掉电中断,系统进入中断服务函数进行紧急处理,立刻给FPGA输出一个掉电信号。存储板FPGA连续判断到掉电信号有效时得知系统即将掉电,存储模块可以在系统完全掉电之前将当前地址信息等进行存储,下次上电时即可重新读出掉电时的存储地址,避免了每次上电后重新擦除再记录,节约系统开发周期,有效的防止了意外掉电系统进入紊乱状态。掉电监测的工作流程框图如图6。

掉电信号检测如图7所示。图7(a)中①是系统外部供电直接切断电源后的示波器信号图,②是系统内部5 V供电的电压下降曲线图,时间单位是1 ms。图7(b)中①是触发PVD中断后输出的掉电信号,②中的FLASH存储掉电信号所用的时间信号线(低电平时间段为存储所用的有效时间<200 μs),单位是100 μs。由图7(a)可知系统完全掉电最少需要3 ms的时间,图7(b)可知,存储模块从检测掉电信号到完成掉电信息的存储需要的时间小于600 μs,因此,掉电监测模块可以满足系统工作要求。

图6 掉电信号检测工作流程框图

图7 掉电信号检测

3.2 多路指令编帧

本控制系统通过串口中断和定时器中断完成了多条422指令的接收,编帧处理。上位机通过RJ45网口下发指令至读数盒,然后将422指令发送到STM32,STM32解析编码下发指令字给存储板FPGA。

存储板FPGA在WRCLK的下降沿接收STM32发送的指令,FPGA接收完成后进行指令校验解析并下发至FLASH控制器,回读FLASH数据,并将回读结果传输给STM32。

STM32在RDCLK的下降沿接收存储板的数据信息写入内部FLASH,时序如图8所示,并进行编帧处理,给出应答指令上传至上位机。主要包括接收FLASH坏块数、停止记录的结束地址、ID字比较结果及指令反馈。

图8 STM32读数据时序图

STM32接收FLASH数据使用了4位数据端口,采用数据拼接的方式接收FPGA数据,即4位数据为一组进行接收,STM32两个读时钟接收1Byte的数据,数据拼接过程如图9所示。STM32通过PB5、PB6、PB7、PB8 进行IO口数据接收,定义一个16位变量DATA_H,将接收的数据右移1位后再与0x00f0相与,同理定义一个16位变量DATA_L,将接收的数据右移5位后再与0x000f相与,两个变量各自相与后的和相加组成了一个1Byte数据,即两个读时钟完成一字节的数据接收,多次测试,系统稳定,能够准确传输。此设计有效的节约了4个IO口,STM32F103价格便宜,IO相对较少,本次实验也是一次数据接口的新尝试,在数据接口通信复杂,资源紧缺的情况下可以采用此方案设计,为数据接口通信设计提供一种新思路,节约资源,降低开发成本。

图9 数据拼接过程图

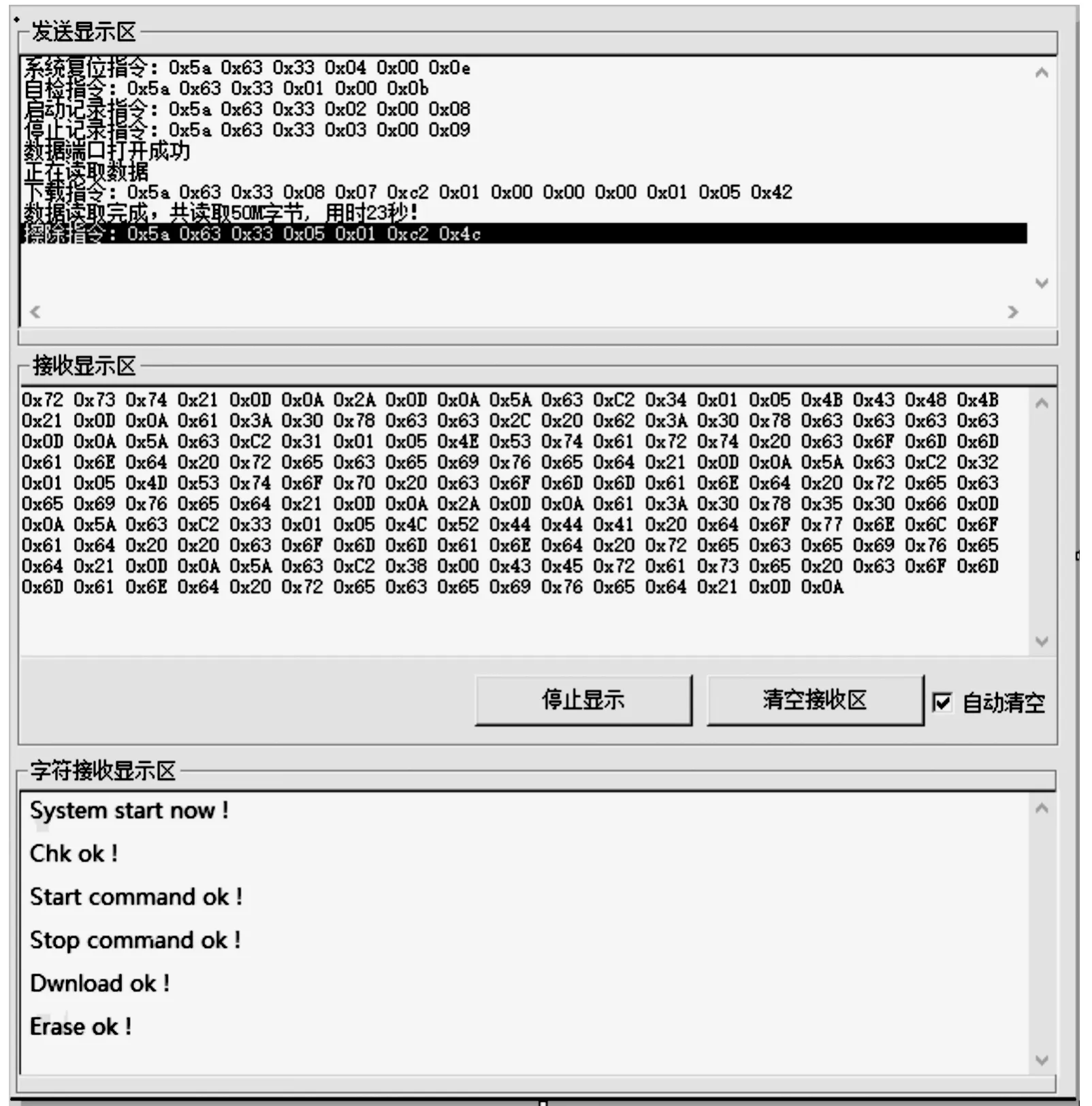

本控制系统上位机采用VB编程,人机交互友好,界面显示清晰。系统上电后通过上位机发送指令,发送的指令显示在发送显示区;接收的应答指令显示在接收显示区,指令的含义在字符显示区显示,下载回读的数据以文件的形式存储在电脑磁盘,便于提取分析,数据回传无误。控制系统上位机测试结果如图10所示的操作界面。

图10 上位机操作界面

3.3 数据存取

数据存储单元主要包括数据接收、数据缓存、flash控制等模块。其功能框图如图11所示。

本系统采用8 Gbytes的镁光FLASH,每块FLASH有16 384个BLOCK,采用FLASH的第零块BLOCK不同页存坏块数、系统的启动记录次数、停止记录地址以及每次系统意外掉电的结束地址[7],在下次启动记录时找到上次的启动次数和结束地址,分别对应累加后再开始新一次的记录。发送下载指令读取FLASH中的数据,其回读结果如图12所示,用Matlab进行数据分析处理提取页计数结果如图13所示,分析可知数据无丢帧乱码现象,多次测试,系统稳定,数据回传正确。

图11 数据存储功能框图

图12 数据回读结果显示

4 结论

该系统分别从硬件和软件方面对存储控制系统进行了系统优化,利用STM32强大的内部资源与FPGA灵活的操控性能进行系统设计,实现了功能互补,符合系统优化的原则[8]。系统采用PVD监测系统电源VDD,给出掉电信号后有效存储数据,保证系统工作的稳定性及准确性。另外系统采用数据拼接的方式接收,有效的节约通信双方的IO口资源,在综合性强、通信复杂度高资源不够用的情况下,此种方法能够有效的减少IO口的使用,节约资源,并且节省电路板空间、降低系统开发成本。该系统还具有良好的可移植性和可维护性,具有很好的实用价值。