全相参数字化连续波应答机的FPGA实现*

2019-11-05方水汛杨述华孟明珠

方水汛,杨述华,孟明珠,孙 欣,杜 玲

全相参数字化连续波应答机的FPGA实现*

方水汛1,杨述华2,孟明珠1,孙 欣1,杜 玲1

(1 北京遥测技术研究所 北京 100076 2 火箭军装备部驻北京地区第二军事代表室 北京 100076)

基于宽带AD、DA以及FPGA的数字化平台,对连续波应答机的接收解调以及相参转发方案作了详细介绍。对于主载波采用FFT实现快速捕获,二阶锁频环辅助三阶锁相环实现精确跟踪。测试结果表明,相参连续波应答机测速精度可以达到0.01m/s,测距精度可以达到1m。

连续波应答机;数字化平台;全相参;高精度测量

引 言

连续波应答机设备转发主要有三种体制:相参体制、非相参体制及相参非相参结合的混合体制[2]。全相参体制是三站都以相参的方式进行测量,测速定位精度较高。但是应答机设备复杂,模拟化平台锁相环以及倍频链较多,三路之间容易互相干扰,体积、功耗、重量较大,不符合通常的航天产品“上宽下严”的原则,所以目前采用较少。非相参体制虽然精度低,但是应答机设备简单,适合于中精度系统应用。而对于混合体制,通常来说其中一站为相参,其他两站为非相参,这样设备结构简单,相参站实现高精度测量,而非相参站采用抵消技术实现双向相参测速,精度也较高,目前大部分设备采用该种体制。

随着航天任务需求的发展,应答机也朝着小体积、轻重量、低功耗、高精度的方向发展,所以数字化平台正逐渐替代原有的模拟化平台,成为连续波应答机的优选方案。数字化平台的应用也解决了全相参体制设备复杂、三站信号相互干扰的问题,使全相参高精度测量的应用成为可能。本文基于高速AD、DA以及FPGA软件无线电数字处理平台,采用主载波粗捕获转细跟踪,然后相参转发,实现全相参连续波应答机的高精度测量。

1 连续波应答机测量原理

1.1 测距测速体制

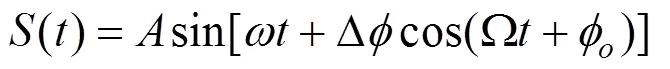

连续波应答机采用音码混合与扩频体制,由PN码对低速率的解模糊码进行扩频,解模糊码的码元时间宽度等于PN码的重复周期,PN码再对1MHz高侧音进行BPSK调制,调制后的高侧音对载波进行调相。主载波用于测速,PN码主要利用地面站发射与接收相位差进行测距,信号如式(1)所示[3]。

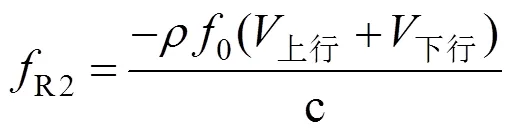

1.2 测速原理

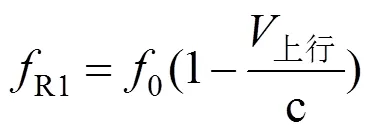

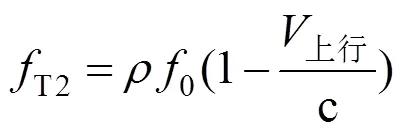

地面站发射的上行载波频率为T1,由于目标相对运动,到达航天器的上行频率为R1。

地面站接收频率为

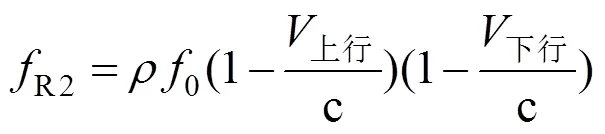

可以得到

由式(6)可以看出,相参测速精度很大程度取决于地面发射频率稳准度,符合“宽上严下”的原则。

2 总体方案设计

为了提高和保证外测体制的测速定位精度,地面雷达系统布站数量应保证应答机跟踪测量带内有3个或3个以上的雷达站有效测量数据。因此,应答机必须同时并且独立转发3个地面雷达站的信号。应答机接收的上行信号如式(7)所示。

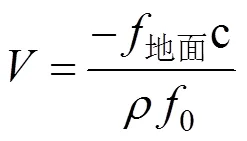

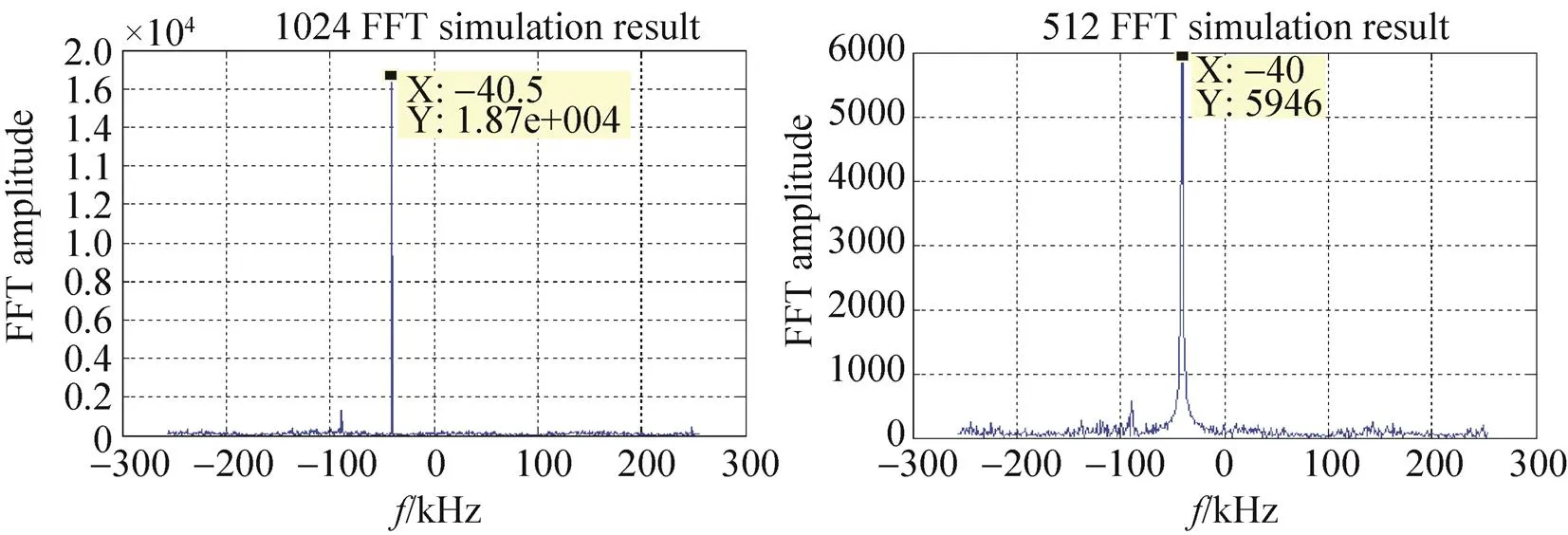

本文基于高速AD、DA以及FPGA软件无线电数字处理平台的方案展开,如图2所示。上行信道单元完成射频信号功率控制、下变频、滤波、AD采样等功能;下行信道完成中频信号DA转换、上变频等功能。数字处理单元完成三路信号提取,然后分别进行主载波信号捕获跟踪,将三路测距信号根据转发比进行中频转发,以实现三路全相参测量功能。

图1 三站信号频谱

3 数字处理平台方案设计

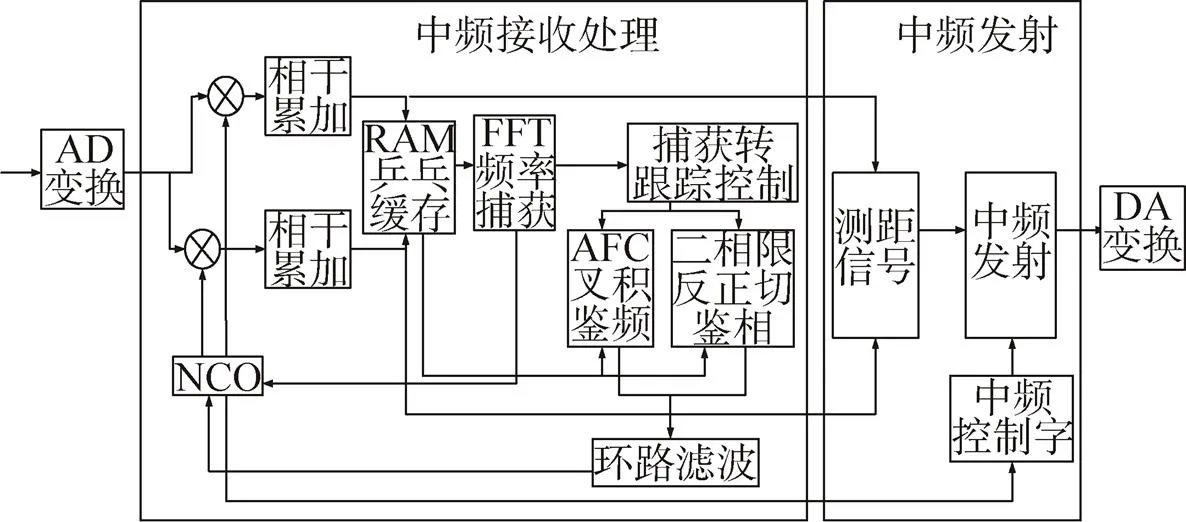

本文基于FPGA数字化处理平台,针对连续波应答机主载波同步问题,提出了捕获跟踪方案:载波捕获使用FFT方法,跟踪采用二阶锁频环辅助三阶锁相环;实现主载波同步后,提取测距副载波信号[4],转发调制至DA中频输出,如图3所示。

图2 三路全相参连续波应答机方案设计

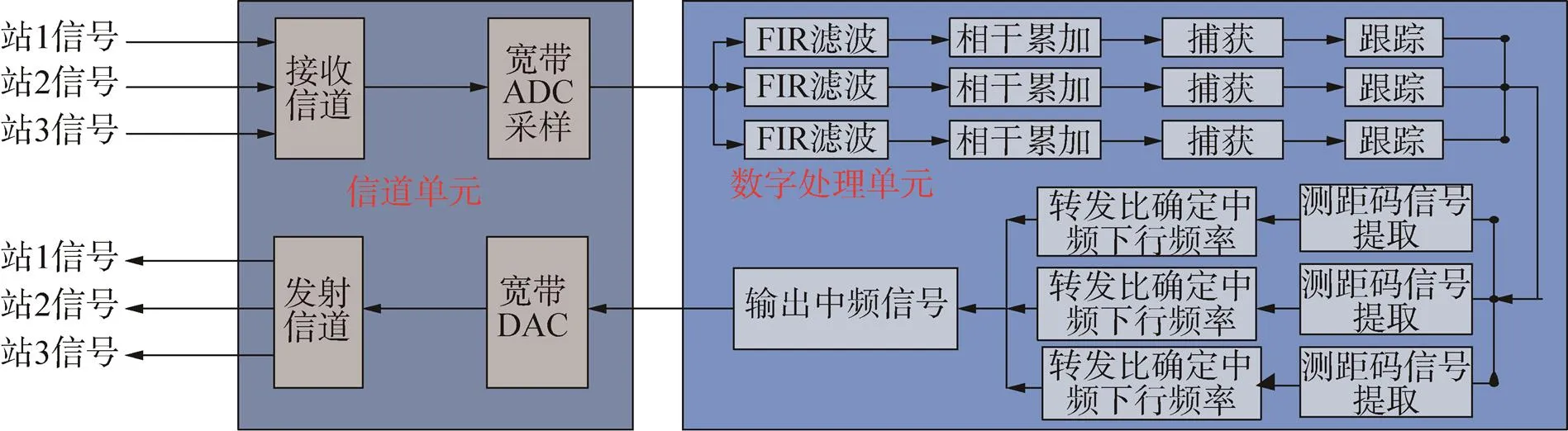

3.1 FFT实现载波捕获

从图3中可以看出,中频模拟信号经ADC采样量化输入数字处理单元,经过数字下变频操作,将主载波变频到零频附近。低通滤波器可以实现单路信号提取,同时滤除带外噪声,提高信噪比。除此之外,还需要滤除副载波信号,以便实现FFT分析主载波单频信号,防止FFT分析结果出现频谱扩展。

图3 数字化处理平台方案

假设多普勒频率为41.8kHz,AD采样速率为524MHz,采样数据量太大,可以采用相干累加来降低采样率。设置相干累加后的采样率为512kHz,则可以分析的多普勒范围为(–256kHz,+256kHz),512点FFT分析的多普勒分辨率为1kHz,而1024点FFT分析多普勒分辨率为500Hz。同时相干累加可以滤除1MHz的副载波信号。

图4 FFT捕获仿真结果

3.2 载波跟踪

为了实现高精度测量,通常锁相环采用较窄的环路带宽,从而能够高精度跟踪信号的相位误差,在高动态多普勒频移下,锁相环不能够快速稳定的跟踪信号,需要锁频环的辅助,锁频环具有较宽的环路带宽,能够快速调整反馈的相位,从而使相位误差落在锁相环的快捕带中。因此在本方案的跟踪环节,采用二阶锁频环辅助三阶锁相环实现,原理如图5所示[5]。

图5 二阶锁频环辅助三阶锁相环结构

图6 FPGA处理示意图

图7 连续波应答机功能测试结果

4 FPGA实现

中频信号处理采用数字化处理,由FPGA实现。高速AD采用524MHz采样时钟,在FPGA经过并串转换以及相干累加实现降速处理,FPGA处理主时钟降为52MHz。

乒乓缓存RAM主要作用是提高相关累加和FFT之间的接口速率;FFT分析后完成主载波捕获,然后转入频率跟踪模块,二阶锁频环辅助三阶锁相环完成主载波的高精度跟踪;载波同步后发射模块将提取副载波测距信号,根据上行跟踪频率控制字以及转发比得到中频频率字,调制测距信号,完成下行信号中频发射。

为验证本方案功能,在FPGA数字平台上实现此功能后,在同体制某型号应答机综测仪设备上进行了测试验证,在静态测试环境下,侧音、PN测距码、巴克码锁定正常。测距精度优于1m,测速精度优于0.01m/s,测试结果见图7。

5 结束语

本文基于FPGA数字化处理平台,给出了连续波应答机的接收解调方案,采用FFT捕获主载波,二阶锁频环辅助三阶锁相环实现主载波精确跟踪,并根据转发比完成测距信号的相参转发,实现了测距测速功能,给出了测试结果。结果表明,该数字化连续波应答机测距精度小于1m,测速精度小于0.01m/s。相比于传统模拟数字化平台集成度更高,功耗更低,精度更高。

[1] 赵业福, 李进华.无线电跟踪测量系统[M].北京: 国防工业出版社, 2001:103–104.

[2] 漆家国.3RṘ测量系统的高精度新型应答机设计[J].电讯技术, 2006,46(5):127–130.QI Jiaguo.Design of a novel and high precision transponder based on 3RR instrumentation system[J].Telecommunication Engineering,2006,46(5):127–130.

[3] 黄成芳, 何平.新型应答机和它的测量系统[G].北京: 航天测控技术研讨会, 2005.

[4] 石启亮, 陈东, 陈方涛.USB系统多副载波调制对测距性能的影响[J].遥测遥控, 2011,32(4):59–63. SHI Qiliang, CHEN Dong, CHEN Fangtao. Effect of multi-subcarrier modulation to the performance of ranging in USB system[J]. Journal of Telemetry, Tracking and Command, 2011,32(4):59–63.

[5] 谢钢.GPS原理与接收机设计[M].北京: 电子工业出版社, 2009:301–302.

[6] 葛雄强, 张祥金.导航信号载波跟踪环路的研究[J].电子测量技术, 2011,34(2): 14–17. GE Xiongqiang, ZHANG Xiangjin. Research in navigation signal carrier tracking loop[J]. Electronic Measurement Technology, 2011,34(2): 14–17.

[7] 王宇舟.三阶锁相环环路滤波器参数设计[J].电讯技术, 2008,48(9): 51–55.WANG Yuzhou. Parameter design for loop filter of third-order PLL[J]. Telecommunication Engineering, 2008,48(9): 51–55.

Digital FPGA implementation of continuous wave transponder with coherent phase

FANG Shuixun1, YANG Shuhua2, MENG Mingzhu1, SUN Xin1, DU Ling1

(1. Beijing Research Institute of Telemetry, Beijing 100076, China; 2. The Second Military Delegate Office of the PLA Rocket Force Armament Department in Beijing, Beijing 100076, China)

In this paper, a digital implementation of the receiving demodulation and coherent transmitting is introduced, which is based upon ultra high-speed AD, DA and FPGA platform. The FFT is used for fast acquisition of the main carrier and the second-order frequency-locked loop assists the third-order phase-locked loop to achieve accurate tracking. The static test result shows that the velocity precision can reach 0.01m/s and the ranging precision can reach 1m.

Continuous wave transponder; Digital platform; Coherent; High precision measurement

TN914.3

A

CN11-1780(2019)04-0029-04

方水汛 1990年生,硕士,工程师,主要研究方向为测控通信和数字基带处理。

杨述华 1984年生,硕士,工程师,主要研究方向为测控通信系统总体。

孟明珠 1987年生,硕士,工程师,主要研究方向为测控通信和数字基带处理。

孙欣 1984年生,硕士,工程师,主要研究方向为无线通信电路与系统。

杜玲 1974年生,硕士,研究员,主要研究方向为测控通信系统总体。

Email:ycyk704@163.com TEL:010-68382327 010-68382557

航天预研项目支持

2019-05-16

2019-07-11