语音端点检测算法研究及其VerilogHDL设计概述

2019-10-21庞盼段圆梦

庞盼 段圆梦

摘 要 本文以语音端点检测算法为基础,着重研究了基于短时平均能量以及过零率的语音端点检测算法原理及其实现,并且对其算法进行测试,基于该算法使用verilogHDL对其进行硬件设计,最后对该算法在硬件设计模块上的性能进行了仿真,取得了较好的效果。

关键词 语音端点检测;短时能量;VerilogHDL

Abstract Based on the speech endpoint detection algorithm, this paper focuses on the principle and implementation of speech endpoint detection algorithm based on short-term average energy and zero-crossing rate, and tests its algorithm. Based on this algorithm, verilogHDL is used to design hardware. Finally, The performance of the algorithm on the hardware design module was simulated and good results were obtained.

Keywords Voice activity detection; Short-term average energy; VerilogHDL

1语音端点检测背景及其研究现状

语音端点检测(voice activity detection)又称VAD,是指在一段语音中准确检测出语音的起止点和终点,这种技术广泛应用于语音识别和语音增强技术中,例如在语音识别中,先检测出端点再进行语音识别,这样不仅能提高识别准确率,并且可以降低功耗,通常来讲,语音端点检测就是各种语音信号系统研究中的预处理。

语音端点检测的发展历史最早可以追溯到1950年左右,经过几十年的研究发展,VAD相关的算法研究已经比较成熟,甚至有相当的算法经过人们改进之后可以设计为硬件模块或者IP核,这也提高了VAD检测的速度,本文将基于一种VAD算法的研究,并且将其硬件设计实现[1]。

2VAD相关算法

VAD算法的应用基本是处于两个背景下的,一种是基于中高信噪比的VAD算法,一种是基于低信噪比的VAD算法。

基于短时平均能量及其过零率的VAD算法实现简单,稳定性强,是一种经典的VAD算法[2];基于频带方差法的VAD算法着重研究语音和噪声在频谱中的差异特性,效果较好,衍生出来有子带频带方差VAD算法,频域BARK子带方差的VAD算法;低信噪比条件的VAD算法处理思想要先进行增强处理然后再结合频带方差或者短时能零率进行检测,对于低信噪比的信号处理效果较好,但缺点是算法复杂,常用算法有谱减法结合子带方差法等。

3基于短时平均能量和过零率的VAD算法原理研究

基于短时平均能量和过零率的算法是VAD中最经典的算法,其原理是根据汉语发音中韵母中有元音,能量较大,而声母是辅音,其频率较高,总会在零点经过,所以根据这两个特点找出声母和韵母,就可以准确检测出语音段[3]。

假如输入一段采样率为16KHZ的语音信号为x(n),对语音进行归一化和分帧处理,假设帧长为framelen,通常为几百个采样点,这里设置为256个采样点,同时帧移设为frameinc,长度为64个采样点,处理后的语音设为xi(m),其中i表示第i帧,总帧数设置为fn语音分帧处理的原因是可以观察语音的短时特性[4],同时也有利于语音的平滑处理。

经过上述处理,计算每帧信号的短时平均能量,设AMP为每帧信号的短时平均能量,则:

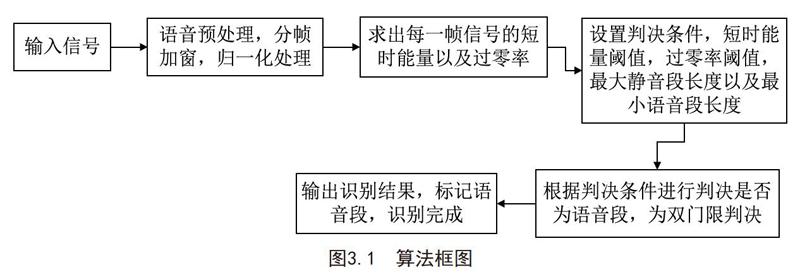

执行每帧信号的短时平均能量和过零率计算的函数如上所示,接下来根据语音段和非语音短时平均能量和短时过零率的差异特性进行检测即可,整个算法的框架如下:

语音预处理的目的在于消除信号直流分量,分帧可以更好地观察信号的短时特性,根据公式可以求出短时平均能量及其过零率。

对于判决条件中阈值的选择,我们可以设置一段前导无话段来提前估算噪声的能量,然后根据此段设置短时平均能量和过零率阈值即可。

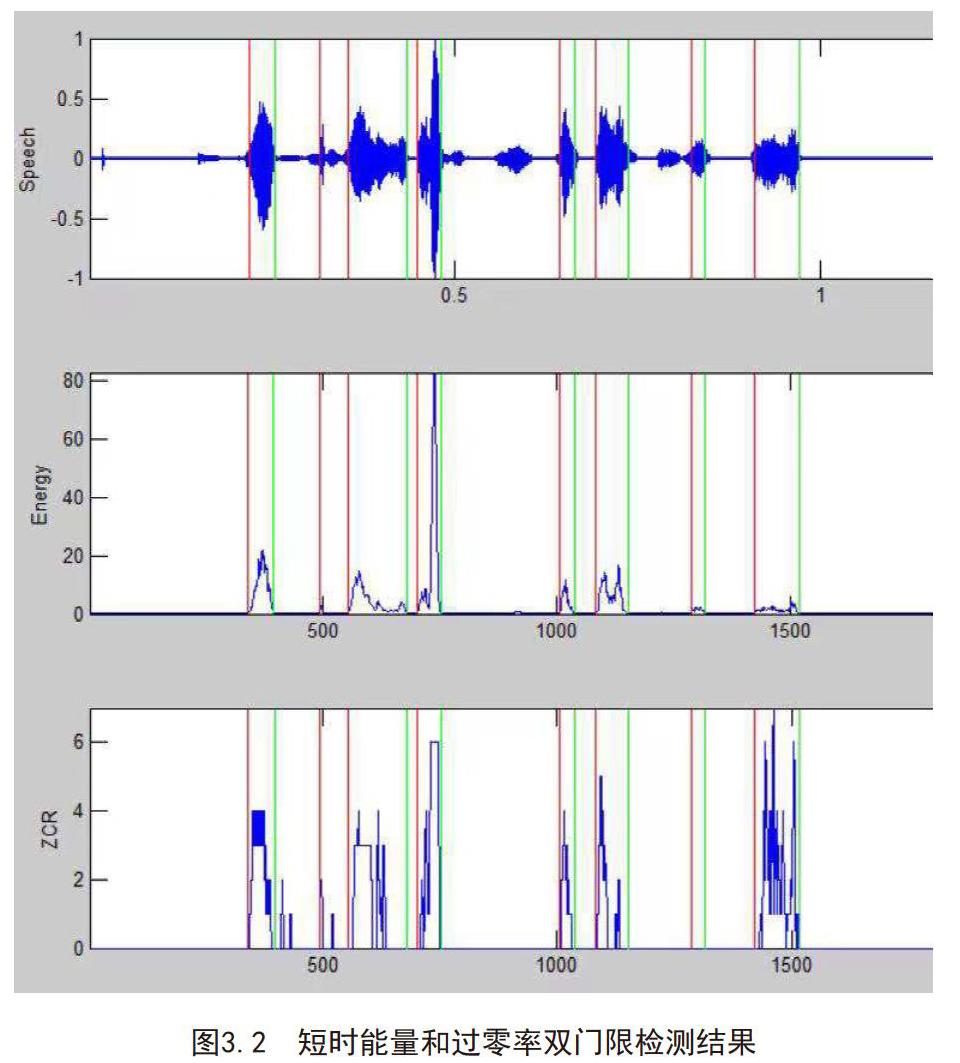

如上图所示为其中一段测试结果,Speech为带噪声语音,Energy为短时平均能量,ZCR为过零率,两边红绿色线截取即为语音段,也就是检测结果,可以看出测试结果正确率较高。该算法对中高信噪比的信号检测比较有效且算法复杂度低,易于实现,下一节将以该算法为基础研究算法的硬件实现。

4VerilogHDL设计仿真

这一节主要设计将matlab实现的算法转化为硬件层面的算法,使用的语言为VerilogHDL硬件描述语言,后期使用的仿真工具为VCS,dump波形工具为Verdi,对于该设计将采用VCS+Verdi联合仿真[5]。

首先对VAD模块端口简单设计,主要有时钟输入端口,复位端口,信号选择端口,数据输入端口,有效信号端口,还有输出端口。

整个模块数据采用16KHZ采样率采样的信号,数据为16bit定点化有符号数。首先对整个数据使用寄存器缓存两拍,对于verilogHDL实现语音分帧可以采用计数器,首先256个采样点为一帧信号,其实是4*64个采样点组成,可以对计算出的能量进行累加,计数器计数至64清零,之后重新计数,定义4个寄存器,将累加的64个能量值依次赋值到新定义的寄存器中,四个寄存器的值相加即可得到每帧256个采样点,帧移为64 的信号处理结果。

对于短时平均能量的计算,matlab通常可以直接相除,但是在verilogHDL设计中不建议直接相除,因为这样会导致仿真验证后综合难以完成或者综合产生的模块面积或者功耗过大,所以在初步设计时候,分帧的采样点和帧移尽量设置为2的次方,这样除法可以直接采用移位完成操作,假如不是2的次方,对于除法仍然可以采用移位相加的形式来完成。

对于短时能量的计算,直接相乘即可,对于过零率的计算,采用同步状态机(FSM)设计,状态机编码采用二进制码或者格雷码,状态机的转移图如图4.1所示:

短时平均能量和短时过零率计算完成以后可以根据其前导无话段计算出来的阈值进行逐帧判决,判决结果输出为0或者1。

设计完成之后编写testbench进行仿真验证,采用vcs和verdi联合仿真,dump出模块中的各个情况的输出波形查看是否符合预期结果,经过验证,结果符合预期,det为输出,输出为1则表示语音段,输出为0则表示非语音段。

5结束语

本文以VAD算法为基础,综述当前比较常用的VAD算法,着重研究了短时平均能量以及过零率的算法,并且将其用verilogHDL设计成为硬件模块,可以看出,该算法检测效果较好,但是测试阶段显示该算法在低信噪比条件下性能不佳。

随着神经网络[6]的发展,现在已经有比较成熟的神经网络算法应用在了VAD算法上,今后的VAD也肯定向这个方向发展,希望未来可以有更好的算法应用于语音端点检测上。

参考文献

[1] 宋知用.MATLAB语音信号分析与合成[M].北京:北京航空航天大学出版社,2018:118-119.

[2] 汪鲁才,曹鹏霞,姜小龙.一种改进的含噪语音端点检测方法[J].计算机工程与应用,2016,52(15):165-167.

[3] 朱明明,吴小培,罗雅琴.基于子带能量的语音端点检测算法的研究[J].工业控制计算机,2013,26(9):44-45.

[4] 韩立华,王博,段淑凤.语音端点检测技术研究进展[J].计算机应用研究,2010,27(4):1220-1226.

[5] 蔡觉平,翁静纯,褚洁,冯必先. VerilogHDL数字集成电路高級程序设计[M].西安:西安电子科技大学出版社,2015:346-462.

[6] 张梅.一种基于模糊神经网络的语音端点检测方法[J].计算机工程与应用,2012,48(16):133-134.