一种全集成的麦克风可编程增益放大器设计

2019-07-08阮剑剑魏聪陈铖颖

阮剑剑 魏聪 陈铖颖

摘 要: 针对麦克风应用,设计一种全集成、高精度的可编程放大器电路。该电路采用电容增益以及高通滤波器的设计方法,无须片外去耦合电容,实现可编程增益放大器的单片集成。可编程增益放大器电路采用SMIC 0.13 ?m 1P8M CMOS工艺实现。完成后仿真结果表明,在电源电压1 V,增益18 dB,输入信号频率2 kHz,峰峰值50 mV时,可编程增益放大器动态范围达到73 dB,总谐波失真64 dB,整体功耗206 ?W,满足麦克风全集成、高精度的应用需求。

关键词: 麦克风; 全集成; 高精度放大器; 可编程增益放大器; 晶体管; 数字信号处理

中图分类号: TN433?34 文献标识码: A 文章编号: 1004?373X(2019)13?0173?04

Design of a fully?integrated programmable gain amplifier for microphone

RUAN Jianjian1, 2, WEI Cong1, CHEN Chengying1, 2

(1. School of Opto?electronic and Communication Engineering, Xiamen University of Technology, Xiamen 361024, China;

2. Fujian Key Laboratory of Optoelectronic Technology and Devices, Xiamen 361024, China)

Abstract: A fully?integrated, high?resolution programmable gain amplifier (PGA) circuit is presented for microphone application. The circuit adopts capacitor?gain and high?pass filter design method, and does not need the external input?decoupling capacitors, which can realize the monolithic integration of PGA. The PGA circuit is implemented with SMIC 0.13 ?m 1P8M CMOS process. The simulation results show that the power supply is 1 V, the gain is 18 dB, the input frequency is 2 kHz, the peak?to?peak value is 50 mV, the dynamic range (DR) of PGA is 73 dB, the total harmonic distortion (THD) is 64 dB, and the total power is 206 ?W, which can meet the full integration and high resolution application requirements of microphone.

Keywords: microphone; full integration; high?precision amplifier; programmable gain amplifier; transistor; digital signal processing

0 引 言

在移动通信电子设备中,电路规模和芯片面积是设计中需要重要考虑的因素。在手机系统中,降低主板上各芯片的有效面积,不但意味着所需成本的降低,也意味着在同样面积的印刷电路板中可以添加更多的芯片,丰富系统功能。在传统的手机主板中,以电阻、电容和电感为代表的无源表贴器件以直接焊接的形式占据了大量的系统面积。近年来,归功于SIP(System In a Package)系统级封装技术,工程师可以将这些无源器件与芯片封装在一个管壳内[1?2]。然而在麦克风至模拟前端放大器的通路中,往往需要较大的去耦合电容,而这些大容值的电容由于面积过大,很难实现SIP封装。

一个典型的麦克风至可编程放大器需要利用片外去耦合电容消除麦克风中的直流分量[3?5]。去耦合电容的容值范围一般在几百纳法至几个微法之间,无法集成在片内。文献[6]介绍了一种无需去耦合电容的电流模可编程放大器电路,但受限于电路结构,无法实现70 dB以上的动态范围。

本文采用高通滤波器设计思路,完成一款将去耦合电容集成于片内的全集成麦克风可编程增益放大器电路。该电路采用低压差线性稳压器(Low Dropout Regulator,LDO)提供稳定的1 V电源,在数字信号处理电路写入增益控制工作模式下可实现步长1.5 dB,总共20 dB的增益可调。同时在设计时进行了电路功耗优化,实现了大动态范围、高精度的信号输出。

1 可编程增益放大器电路概述

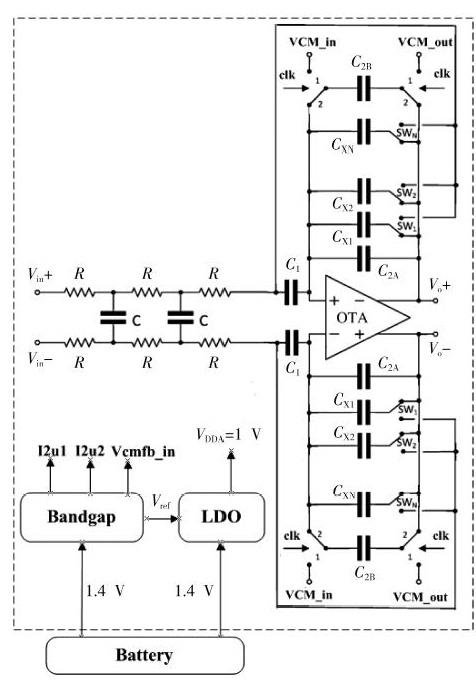

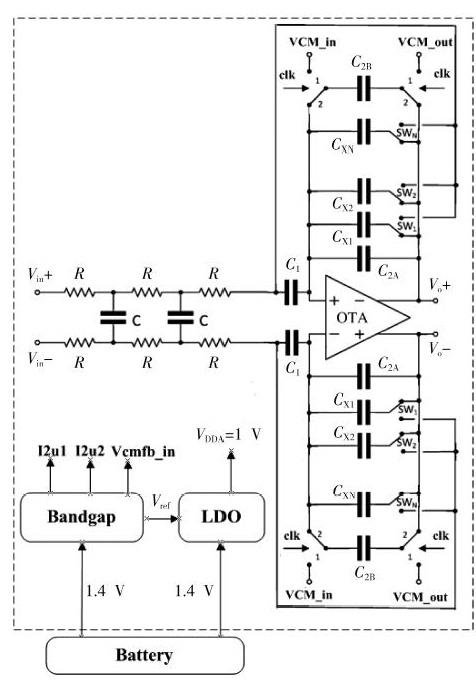

典型的麦克风信号模拟处理通路包括可编程增益放大器、抗混叠滤波器、开关电容Sigma Delta调制器以及数字滤波器。作为麦克风信号处理的第一级,可编程放大器一般需要提供0~20 dB的增益可调,更多的增益则可以在后续的数字信号处理电路中完成[7?9]。为了满足麦克风高品质输出的应用需求,可编程增益放大器的输出信号应该具有60 dB以上的动态范圍(DR)和总谐波失真(THD)性能,设计的可编程增益放大器电路框图如图1所示。

图1 可编程增益放大器电路框图

考虑到片上电容占据大量面积,本文设计在0 dB增益时,[C1]的电容值设为30 pF。由于人耳接收声音的最低频率范围在20 Hz以上,因此可以通过选择时钟频率clk和[C2B]的多种组合进行配置,这里取时钟频率[fclk=]140 kHz,[C2B]=20 fF,使得高通截止频率约为15 Hz,留出一定的频带裕度。带隙基准源在为LDO提供0.4 V参考电压的同时,也为跨导放大器提供两路2 μA的电流偏置以及0.5 V的共模反馈电压;LDO由片外提供1.4 V电源,并输入Bandgap的参考电压,为缓冲器、跨导放大器提供稳定的1 V电源电压。

2 模块电路设计

如图1所示,由开关SW1,SW2,…,[SWN]控制的电容[CX1,CX2,…,CXN]与电容[C2A]平行连接,实现1.5 dB的增益可调。为了驱动后级的Sigma Delta调制器,并实现较大的输出摆幅,本文设计了一款低压两级密勒补偿的Class?AB跨导放大器作为可编程放大器的核心[10],其电路如图2所示。

图2 整体跨导放大器电路

图2中,第一级放大器的负载晶体管被拆分为两对晶体管NM1a,NM2a和NM1b,NM2b。NM1a,NM2a被偏置在一个固定的电压值,而NM1b,NM2b由共模反馈电路进行驱动。这种方式的最大优势在于有效降低了共模反馈放大器電路的输出负载电容,有利于提高跨导放大器的相位裕度、稳定频率特性。PM3/NM3,PM5/NM5和PM4/ NM4,PM6/NM6组成的Class?AB输出级优化了输出静态电流,同时实现了较大摆幅的输出电压。

为了优化跨导放大器的噪声性能,选择PM1和PM2作为跨导放大器的输入级。根据噪声理论[11],跨导放大器的等效输入噪声为:

可编程增益放大器中的带隙基准源电路如图3所示,主要包括电压偏置电路、主电路和上电启动电路三部分。当电源为零时,PMOS晶体管PM9栅极电压为零,PM9开启;随着电源电压升高,从电源到跨导放大器输入端形成一条电流通路,此时跨导放大器开始工作,同时该导通通路也对NMOS电容NM1进行充电;当电源电压继续升高,PMOS晶体管PM8逐渐开启,形成一条PM8到电阻[R5]的电流通路,当PM9的栅极电压持续升高,满足过驱动电压绝对值大于漏源电压绝对值的条件时,PM9关断。此时MOS电容充电过程结束,MOS电容上的电压可以维持跨导放大器的输入直流偏置电压,带隙基准源进入稳定工作状态。

图3 带隙基准源电路

本文设计的LDO电路采用传统的两级误差放大器电路结构[12?14],同时加入密勒补偿电容稳定电路频率特性。LDO输出晶体管的宽长比设计为600 ?m/300 nm的大尺寸,增强了输出级的电流驱动能力。

3 电路后仿真结果

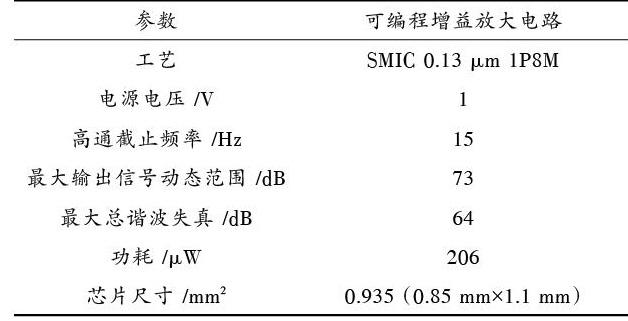

可编程增益放大电路基于SMIC 0.13 ?m 1P8M CMOS工艺设计实现,整体电路版图如图4所示,所占面积为0.935 mm2 (0.85 mm×1.1 mm)。

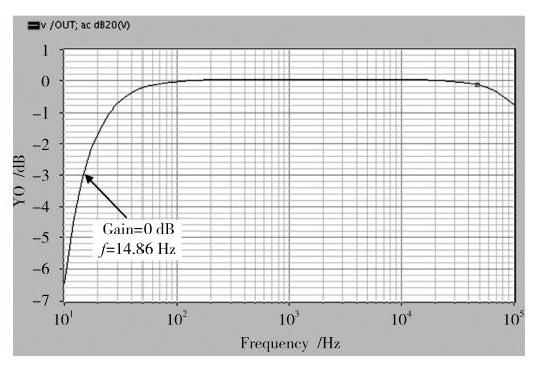

完成版图后,首先进行频率响应特性仿真,仿真结果如图5所示,可见在0 dB增益时,高通截止频率为14.86 Hz,符合设计要求。

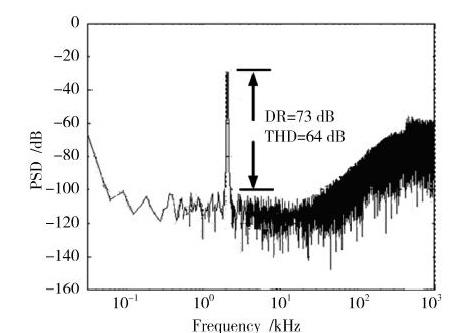

在不同的输入信号幅度下,对输出信号精度进行仿真,在输入信号频率为2 kHz,峰峰值幅度为50 mV,增益为18 dB时,输出信号动态范围为73 dB,总谐波失真为64 dB,输出信号的频谱如图6所示,可见在1 V电源供电时,PGA电路仍保持了较高精度的信号输出。

图4 可编程增益放大电路版图

图5 可编程增益放大电路频率响应

图6 输出信号频谱

表1 可编程增益放大电路性能总结

表2 可编程增益放大电路性能比较

4 结 语

本文设计一款无片外去耦合电容的全集成麦克风可编程增益放大电路。该电路在DSP控制下可实现1.5 dB线性步长,总范围20 dB的增益可调。可编程增益放大器采用SMIC 0.13 ?m 1P8M CMOS工艺实现,后仿真结果表明,在电源电压1 V时,高通截止频率约为15 Hz;在输入信号频率2 kHz,增益18 dB时,输出最大动态范围为73 dB,总谐波失真64 dB,总功耗为206 ?W。与参考文献中的设计结果相比,在动态范围、总谐波失真以及功耗等参数指标上具有较大的可比性,总体性能相当,满足麦克风信号处理的精度应用需求。

参考文献

[1] 李振亚,赵钰.SIP封装技术现状与发展前景[J].电子与封装,2009,9(2):5?10.

LI Zhenya, ZHAO Yu. The status and future prospects of system?in?package technology [J]. Electronics & packaging, 2009, 9(2): 5?10.

[2] 李悦.数字处理器SiP封装工艺设计[J].电子工艺技术,2015(2):86?88.

LI Yue. Technology design of system in package of digital processor module [J]. Electronics process technology, 2015(2): 86?88.

[3] LI Fangyang, YANG Haigang, LIU Fei, et al. A current mode feed?forward gain control system for a 0.8 V CMOS hearing aid [J]. Journal of semiconductors, 2011, 32(6): 126?131.

[4] DAI Lan, LIU Wenkai, LU Yan. A 410 μW, 70 dB SNR high performance analog front?end for portable audio application [J]. Journal of semiconductor (English edition), 2014, 35(10): 113?116

[5] MOHIELDIN A N, MEKKY R H, EMIRA A, et al. A 0.9 mW microphone uplink system in a 65 nm CMOS [C]// 2009 IEEE International Symposium on Circuits and Systems. Taipei, China: IEEE, 2009: 1149?1152.

[6] BAKER M W, SARPESHKAR R. A Low?power high?PSRR current microphone preamplifier [J]. IEEE journal of solid?state circuits, 2003, 38(10): 1671?1678.

[7] MA Li, WANG Zhigong, XU Jian. A signal?summing programmable gain amplifier employing binary?weighted switching and constant?gm bias [J]. Journal of Southeast University, 2017, 33(2): 134?139.

[8] CARRERA A, De La ROSA R, ALONSO A. Programmable gain amplifiers with DC suppression and low output offset for bioelectric sensors [J]. Sensors, 2013, 13(10): 13123?13142.

[9] 赵亮.低功耗恒定带宽可编程增益放大器的设计[J].现代电子技术,2015,38(12):126?128.

ZHAO Liang. Design of programmable gain amplifier with low?power consumption and constant bandwidth [J]. Modern electronics technique, 2015, 38(12): 126?128.

[10] ESCHAUZIER R G H, KERKLAAN L P T, HUIJSING J H, et al. A 100 MHz 100 dB operational amplifier with multipath nested miller compensation structure [J]. IEEE journal of solid?state circuits, 1992, 27(12): 1709?1717.

[11] GRAY P R, MEYER R G. MOS operational amplifier design: a tutorial overview [J]. IEEE journal of solid?state circuits,1982, 17(6): 969?982.

[12] SHEN Liangguo, YAN Zushu, WANG Zhao, et al. Analysis and design of a high?stability, high?accuracy, low?dropout voltage regulator [J]. Journal of semiconductor (English edition), 2007, 28(12): 1872?1877.

[13] Liu Zhiming, Fu Zhongqian, Huang Lu, et al. A 1.8 V LDO voltage regulator with foldback current limit and thermal protection [J]. Journal of semiconductor, 2009, 30(8): 136?140.

[14] GAO Leisheng, ZHOU Yumei, WU Bin, et al. A full on?chip CMOS low?dropout voltage regulator with VCCS compensation [J]. Journal of semiconductor, 2010, 31(8): 132?136.

[15] JAWED S, CATTIN D, GOTTARDI M, et al. A 828 ?W 1.8 V 80 dB dynamic range readout interface for a MEMS capacitive microphone [C]// 2008 European Solid?State Circuits Confe?rence. Edinburgh: IEEE, 2008: 442?445.

[16] JIANG X, SONG J, BROOKS T L, et al. A 10 mW stereo audio CODEC in 0.13 ?m CMOS [C]// 2010 IEEE International Solid?State Circuits Conference. San Francisco: IEEE, 2010: 82?83.