高压陡脉冲发生器的设计与实现

2019-03-06郭蒙召张建勋

陈 穗,郭蒙召,张建勋

(1.南开大学 人工智能学院,天津300350;2.天津市智能机器人技术重点试验室,天津300350)

目前,全球癌症负担不断加重,癌症已经成为威胁人类生命和健康的主要疾病之一[1]。 近年兴起的电脉冲消融是通过电脉冲诱导肿瘤细胞凋亡而消灭肿瘤的一种治疗方式[2-4]。 研究表明,上升沿为ns 级别、脉宽为μs 级别、幅值为kV/cm 的脉冲电场作用于肿瘤细胞时,细胞将发生不可逆电穿孔凋亡。

自发现高压脉冲电场对肿瘤具有杀伤作用以来,国内外许多机构高度关注高压陡脉冲发生器的研究。 美国AngioDynamics 公司在2012 年研发了“纳米刀”,电脉冲消融首次用于临床治疗。 在国内,文献[5]在电脉冲消融的理论研究和试验等方面都有较大突破,其研发的ps 脉冲细胞试验装置可将脉冲沿缩短至ps 级别, 但装置尺寸限制了脉冲功率;文献[6]通过磁开关技术极大地缩短了脉冲前后沿时间,但磁特性限制了脉冲宽度的可调范围。

在此设计了一种脉宽、周期和幅值大范围可调的高压陡脉冲发生器。 脉冲发生器工作电压为0~3000 V, 工作电流为0~60 A, 控制器采用DSP+CPLD 架构, 在接口电路设计中采用多种抗干扰措施,保证电路工作的稳定性。 目前高压陡脉冲发生器正在天津市智能机器人技术重点试验室进行相关试验。

1 高压脉冲发生器整体结构设计

高压陡脉冲发生器通常是将巨大能量存储在电容、电感等储能器件中,再通过高压开关实现能量的断续输出,得到极高瞬时功率的高压脉冲。 高压陡脉冲发生器整体结构如图1 所示。

图1 高压陡脉冲发生器结构Fig.1 Structure of high-voltage and steep pulse generator

脉冲发生器采用高压直流电源作为初级能源,电容组作为储能器件,IGBT 作为高压开关, 通过高压继电器隔离各个高压模块。 高压陡脉冲发生器采用DSP+CPLD 架构的控制器完成充放电流程的控制。

2 主电路结构及特点

2.1 充电模块

大容量电解电容具有储能大,放电电压平稳的特点,可以瞬间释放大电流[7-8]。 在此使用大容量电解电容作为高压陡脉冲发生器的储能器件,多个电容串联提高储能电压。 电路设计中引入电压均衡与过压保护电路,高压继电器作为隔离开关,多个继电器配合完成充电/放电通道的选择。充电时断开放电通路, 保证高压电源与患者间没有电气连接;放电时,电容组与高压电源断开,消除高压电源对脉冲发生器的干扰。

充电模块的部分电路如图2 所示。 电容组由8个电容串联构成(图中给出2 个电容),每个电容的容值为C=1000 μF,电容组等效电容为C′=125 μF,充电过程为恒流充电。 设定高压电源输出电流为5 mA,则电容组电压为

图2 充电电路Fig.2 Charging circuit

式中:U 为电容组电压;t1为充电时间。 电容组电压达到1000 V 需要20 s,2000 V 需要40 s,3000 V 需要60 s,充电速度较快。 从能量的角度来看,电容组充电到3000 V 时,储存的能量为

kJ 级别的储能使脉冲发生器具有释放大功率脉冲的可能。 放电过程电容组电压为

式中:T 为放电回路时间常数;t2为放电时间。 当放电负载为R,脉冲宽度为t′,放电脉冲个数为N 时,放电过程中电容组电压为

式中:U0为电容组初始电压。 假设具有治疗效果的脉冲最小值电压为Umin,令u≥Umin,可得

式中:N 为充电一次最多可以释放的有效脉冲个数。假设放电电流约为30 A,放电电压约为3000 V,脉冲宽度约为125 μs 时,从能量的角度分析得脉冲瞬时功率为

式中:u 为放电电压;i 为放电电流。巨大的能量输出对癌细胞具有巨大的杀伤作用。

2.2 脉冲发生模块

根据电脉冲消融的治疗要求,脉冲幅值要求达到kV/cm 级别,脉冲上升沿时间为ns 级别,脉冲宽度为μs 级别。 为达到kV 级的脉冲幅值,常采用多电子开关串联形式以得到较高的耐压值,但使用多开关串联结构时,非完全同步的驱动信号易使某个电子开关两端电压超过耐压值,而引发其他安全问题。 故在此采用大功率单管IGBT 结构作为陡脉冲发生器的高压开关,提高了整个系统的安全性。

所使用的36 级拓扑结构IGBT 驱动电路:控制器产生幅值为0~5 V 的脉冲信号;信号经过光电隔离和功率放大后输入IGBT 驱动厚膜, 输出0~12 V的脉冲信号;信号通过一级推挽电路产生-12~15 V的IGBT 驱动信号。

通过控制器可以设定脉冲宽度、脉冲周期和脉冲个数;IGBT 驱动厚膜可产生最高可达10 A 的驱动信号,并带有短路保护、过电流保护和故障反馈等功能;功率场效应晶体管构成的推挽电路具有更强的电流输出能力,进一步增强驱动能力。 同时,推挽电路的引入将关断电压降低至-12 V,有效地加快了IGBT 的关断时间,保证了IGBT 的可靠导通和关断。 3 级拓扑结构的驱动电路设计已经被证明是稳定可靠的[9]。

3 控制模块结构及特点

3.1 控制器整体架构设计

高压陡脉冲发生器控制器结构如图3 所示,模块采用DSP+CPLD 的主控架构。 DSP 作为下位机,接收上位机发送的治疗命令,转化为硬件的动作指令,并将底层硬件的部分信息反馈回上位机。 CPLD具有强大的并行处理能力和更稳定的输出能力,因此用CPLD 实现与底层硬件电路的接口。 DSP 和CPLD 之间通过外部存储器接口EMIF(external memory interface)相连,采用异步方式通信。 所使用的DSP 为TI 公司的TMS320F28335,该芯片具有很强的抗干扰能力,常作为电力电子设备控制器主控芯片。在脉冲发生器引起的强干扰环境中,28335 型芯片具有显著优势。 所用CPLD 芯片是Altera 公司的EPM3256ATC144, 其内部集成单元数量满足控制器要求,底层接口电路包括数字信号接口电路和模拟信号接口电路。 其中,数字信号接口电路用于输出继电器和IGBT 控制信号, 接收IGBT 故障信号;模拟信号接口电路用于高压电源控制和电压电流反馈,其电压通道反馈负载两端电压,电流通道反馈电流互感器的输出。

图3 高压陡脉冲发生器控制器的结构Fig.3 Structure of controller for high-voltage and steep pulse generator

3.2 DSP 模块

采用TI 公司的TMS320F28335 带有高性能的32 位CPU;150 MHz 的时钟保证其快速的运行能力和计算能力;高性能静态COMS 技术为芯片提供强大的抗干扰能力支持,适用于高压陡脉冲发生器所引起的强干扰环境中。 此外,芯片丰富的外设资源为底层电路的设计提供了多种可行方案。

DSP 模块主要包括电源电路、 时钟电路、JTAG接口电路、复位电路、UART 接口电路以及外部存储器扩展电路。

DSP 芯片使用外部30 MHz 有源晶振提供时钟信号,时钟信号通过芯片内部的锁相环电路、分频电路和多路开关后产生150 MHz 的CPU 时钟和其他频率的多种外设时钟。 DSP 由外部5 V 电压转化为3.3 V 后供电。

DSP 芯片内部提供了Flash 和SRAM,考虑到设计较为复杂的程序时,程序空间和数据空间相对不足,因此利用DSP 提供的外部存储器接口扩展了1片容量较大的Flash 和1 片高性能SRAM。 考虑到外接Flash 和SRAM 的容量不能完全占据DSP 的外部存储器区域2 MB 的地址空间,因此,扩展的存储芯片被设计接入DSP 的外接存储器区域6,通过地址线的最高位和外部存储器片选信号进行选通,选用了Altera 公司的EPM3202 实现扩展区域的选通逻辑。

3.3 DSP 和CPLD 异步通信接口设计

TMS320F28335 提供了种类丰富的内部存储器单元,包括512 kB 的Flash,64 kB 的SRAM 以及20 kB 的ROM。此外,C2000 系列DSP 提供了3 块地址空间用于外接扩展芯片,在此通过DSP提供的扩展接口实现DSP 和CPLD 的通信。

DSP 模块中,将外部存储器区域6 分配给扩展的Flash 和SRAM, 将外部存储器区域7 分配给CPLD。 DSP 的地址总线信号作为异步通信的地址,数据通过DSP 的数据总线在DSP 和CPLD 之间流动。CPLD 中使用2 个三态门控制数据流向。DSP 的系统时钟输出、读写使能信号用作异步通信接口控制信号。 其中,读写使能信号作为三态门的控制信号,总线上的读写速度与DSP 的系统时钟保持一致,为150 MHz。

3.4 CPLD 中各模块的实现

CPLD 中的模块主要包括地址译码模块、 继电器控制信号输出模块和脉冲信号发生模块。

地址译码模块根据DSP 地址总线信号产生相应的使能信号。 继电器控制信号输出模块根据使能信号分别输出3 组继电器的控制信号。

脉冲信号发生模块包括脉冲发生、脉冲计数以及故障处理等3 个逻辑模块。 脉冲发生逻辑模块连续产生给定参数的脉冲,其中脉冲参数包括脉冲周期和脉冲宽度。 所有参数保存在逻辑模块中构建的寄存器变量中,DSP 通过异步通信接口修改和获取CPLD 中的脉冲参数, 脉冲发生逻辑模块内部构建了1 个计数器,通过比较计数器的值与设定的脉冲参数而产生相应的脉冲输出。 考虑到理想的脉冲频率比CPLD 工作频率小, 将DSP 系统时钟80 分频后作为计数器时钟以节省CPLD 资源开销。 脉冲发生逻辑模块的使能信号和输出信号经过逻辑与作为脉冲计数逻辑模块的输入。 脉冲计数逻辑模块中存有脉冲个数信息,通过捕获脉冲发生逻辑模块输出脉冲的下降沿匹配脉冲个数,两者相等时,封锁脉冲输出。 脉冲计数逻辑模块中构建了延时逻辑用于解除封锁信号,为下一次释放脉冲做准备。 故障处理逻辑模块将底层电路反馈的状态信号和脉冲输出信号进行相应逻辑操作后作为CPLD 级的脉冲信号输出。

3.5 接口电路设计

3.5.1 抗干扰能力的实现

充放电过程中,主电路和控制器之间存在多种信号交互,故针对数字信号和模拟信号传输要求设计了底层接口电路。 考虑到控制器工作在强干扰环境中,抗干扰能力是底层接口电路最为突出的特征之一。

数字信号接口电路中, 传输线路上的能量损失、 终端开关器件引起的噪声都会降低通信质量,针对以上几点采取了多种措施,以保证信号传输的稳定性和抗干扰能力:

1)针对传输线路能量损耗而引起的通信质量降低的情况, 接口电路中使用3.3 V 转5 V 的电平转化芯片, 一方面解决CPLD 和底层电路的电平匹配问题,另一方面通过提高信号强度以增强信号的抗干扰能力。 另外,使用两级非门,保持逻辑不变的情况下提高信号驱动能力。

2)采用光电耦合器件隔离控制器和主电路,阻断噪声传输通道。 在信号频率较低的继电器控制信号传输电路中, 采用PC817 作为光电耦合器件,5000 V 的有效隔离电压高于主电路正常工作时能产生的噪声幅值范围,80 kHz 的截止频率也能满足继电器控制信号对传输速度的要求。 在信号频率较高的IGBT 驱动信号传输电路中, 控制器端采用光纤发射器将电信号转换为光信号,在主电路端使用光纤接收器将光信号转化为电信号,光纤的引入一定程度上增加了电路的复杂性,但更大程度地抑制了高频噪声对控制器的影响。

3.5.2 稳定性和可靠性的实现

模拟信号接口电路主要用于充放电过程中的电压电流反馈,信号更容易受到外界和系统内部干扰。 释放脉冲时,IGBT 开关瞬间产生的高压直接传回控制器将影响控制器正常运行,甚至造成DSP 的损坏。 另外,放电过程中由于高压产生的噪声信号也影响模拟信号传输质量。 故通过以下几方面措施提高信道的稳定性和可靠性:

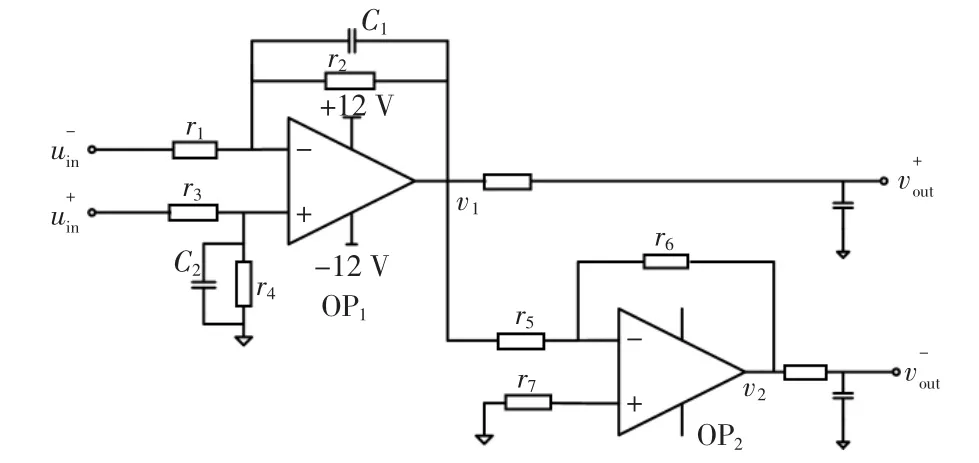

1)电路输入端通过运算放大器构成平衡传输电路,将信道中同向搭载的噪声信号抵消掉,只留下有效信号成分。 平衡传输电路的结构如图4 所示。

图4 平衡传输电路Fig.4 Balanced transmission circuit

该电路主要由2 个运算放大器构成,前一级采用差动电路结构将输入电压数值进行缩小,后一级采用反向比例运算电路结构。 运算放大器本身具有很强的共模抑制能力,共模抑制比为

式中:Ad为差动放大器的放大倍数;t 为电阻容差。假设在Ad=1/500,当t<5%时,此时KCMR,min=5 V/V(约为14 dB)。 它是输入级抑制共模干扰的常用方法。

电路中,运算放大器OP1和OP2输出幅值相等,方向相反,当外界或者系统内部引起的噪声作用于运算放大器或者传输线时,共模部分互相叠加而得到消除。 设r5=r6,电路的输入输出关系为

2)模拟信号传输电路中,也采用了光电隔离措施,以抑制主电路一侧干扰。 光电隔离电路如图5所示。

图5 光电隔离电路Fig.5 Optical isolation circuit

光电隔离电路主要由运算放大器和光电隔离器件TIL300 构成。 TIL300 支持交直流耦合,峰值隔离电压为3500 V,高于主电路3000 V 工作电压的幅值条件;带宽大于200 kHz,满足50~100 μs 脉冲的传输速度要求, 且其具有很高的传输稳定性,成为其模拟信号传输电路光电隔离的理想器件。 电路输入级通过差动电路将输入电压调理为DSP 的电压检测范围,通过运算放大器驱动TIL300,跟随器作为输出级,并在电路输出端使用双二极管形成双向稳压电路结构,抑制过电压,保护DSP 芯片。

4 试验分析

完成主电路和控制器的设计与搭建后,进行了一系列以电阻为负载的放电试验。试验中的波形是经过电阻分压再使用TDS1002 型示波器采样得到的。

图6 所示波形为放电电压3000 V, 脉冲周期180 μs,脉冲宽度60 μs,脉冲个数5 个,负载电阻100 Ω 时,1/100 负载电阻两端采集的电压波形。

由图6a 可见,在放电过程中,脉冲幅值略有减小,较为平稳,无振荡;图6b 为第1 个脉冲上升沿的放大图像,可见脉冲上升沿时间约为500 ns。由电阻试验可知,高压陡脉冲发生器产生的脉冲能达到电脉冲消融的治疗要求。

图6 放电电压Fig.6 Discharge voltage

电压、电流反馈通道采集到的数据,经过反馈通道的缩放系数换算得到的电压、 电流波形如图7所示。 由图可见,放电电压数值、放电电流数值、脉冲个数、脉冲周期以及脉冲宽度基本与设置参数一致。 其中电流反馈信号仍然伴有大量噪声,后续需通过软件做进一步滤波处理。

图7 电压、电流反馈通路波形Fig.7 Waveform of voltage and current feedback path

5 结语

设计了基于不可逆电穿孔治疗的高压陡脉冲发生器, 介绍了主电路和控制器的电路结构及特点。主电路中使用电容组储能,IGBT 作为高压开关,通过多级电路驱动IGBT 可靠产生给定频率和脉宽的脉冲。 控制器采用DSP+CPLD 主控架构, 其中DSP 负责接收上位机命令并负责充放电的流程控制,CPLD 作为DSP 的逻辑扩展模块,实现与底层电路的接口。 底层电路中,数字信号接口电路用于输出开关器件控制信号和接收故障信号,模拟信号接口电路主要用于输出高压电源控制信号和输入电压和电流反馈,电路中采用了多种抗干扰措施以减小主电路高压高频干扰对控制器的影响。 在放电试验中,脉冲发生器产生的波形平稳干净,各参数符合电脉冲消融的治疗条件,反馈电路检测到的放电波形良好,能起到良好的监测作用,所设计电路的性能满足电脉冲消融的手术要求,放电试验表明可以进行更深入的试验和研究。