基于FPGA的二维FFT图像边缘增强设计

2019-03-02任勇峰武昊男储成群焦新泉

任勇峰,武昊男,储成群,焦新泉

基于FPGA的二维FFT图像边缘增强设计

任勇峰,武昊男,储成群,焦新泉

(中北大学电子测试技术国家重点实验室,山西 太原 030051)

在处理图像类信息时,图像细节往往能传达更多信息,是人们较为关注部分。针对在光照不理想的条件下,传感器采集到的图像对比度低、细节难以分辨的问题,提出一种基于现场可编程门阵列(FPGA)的二维快速傅立叶变换的图像边缘提取及增强方法。通过模块化设计,完成4路并行512×512点快速傳里叶变换(FFT)运算处理器设计,并通过FFT模块复用减少FPGA内资源消耗,同时实现图像频谱的高通滤波算法及傅立叶逆变换算法。经过仿真与实验,确定该方法有效可靠,实时性强,可以满足工业上图像处理的需求。

现场可编程门阵列;快速傳里叶变换;边缘增强;频域;滤波

图像增强是数字图像处理的重要组成部分,其目的是增强图像对比度,从而优化视觉效果。人眼对灰度变化的敏感度不是线性的,就8 bit灰度图片而言,人眼只对灰度值位于[48,206]区间的变化较为敏感[1]。为提高灰度图像的人眼视觉效果,人们提出许多相应算法。传统的提高灰度图像的对比度和可视效果的算法有许多,大致可分为空域类和频域类。空域类包括Sobel、灰度变换、Canny等[2];频域类则包括小波变换、短时傅立叶变换、快速傅立叶变换等[3]。

通常情况下图像的特征在空域难以描述,但在频域却十分明显[4],且就提高图像对比度而言,时频分析与频域分析并无太大区别,因此选择快速傳里叶变换(fast Fourier transform,FFT)算法作为本设计的核心算法。通常图像的边缘及细节部分由灰度值相差较大的部分构成,在频域中表现为高频部 分[5]。因此用傅立叶变换的方法对图像进行边缘加强时,只需要提取图像频谱高频部分并加强即可。

所有的图像边缘增强算法有一个共同点——运算量巨大,通常处理时间较长,使用CPU进行运算耗时少则几百毫秒,多则几十秒,难以满足实时性的要求,而现场可编程门阵列(field-programmable gate array,FPGA)具有实时性强,数据吞吐量大的特点,非常适合处理图像类数据[6-7],并且由于其并行运算的特点,可以成倍地提高FFT的运算速 度[8-9]。因此,选择FPGA作为本设计的硬件平台,通过模块化设计,完成4路2D-FFT处理器的设计。

1 FFT算法的FPGA基础

1.1 一维FFT及IFFT

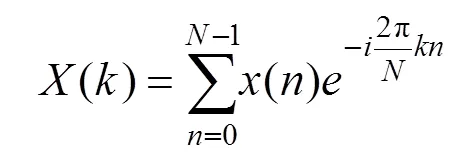

对离散信号() (0≤≤–1),其傅立叶变换为

从式(1)可以看到,()求傅立叶变换的过程即是对一组数据求积再求和的过程。FPGA中有大量的加法器资源,可以方便地实现求和过程。但是乘法运算却会消耗大量的布线和时钟资源。因此要通过FPGA实现高效的傅立叶变换,必须减少其中的乘法运算。

蝶形运算的提出解决了上述的问题。蝶形运算可以将点傅立叶变换转化为2个/2点的傅立叶变换,变换结果再求积与和的形式。如图1所示,将1个长序列分解为2个短序列的FFT运算被称为Radix-2 FFT。

对于=2点序列,进行傅立叶变换需要进行2次乘法与加法,如果进行次蝶形运算后,就可以将傅立叶变换转化为log2次求加法和乘法运算,极大减少了运算量。运算过程中任何一个节点的数值,仅与其前一级的2个节点有关,而与其他节点无关。因此点傅立叶变换过程仅需个寄存器,用来存储当前节点的数据,当下一个节点数据计算完毕后,覆盖寄存器即可。

图1 N点蝶形运算

IFFT是FFT的逆变换,即

对比FFT的定义式,只有旋转因子不同,并且多了一个系数。Radix-2 FFT序列长度是2的整数次幂,在FPGA里通过右移寄存器操作可以简单实现。因此,在FFT的基础上实现IFFT,只需要将逆变换的旋转因子更新进ROM中,再运算出结果后,将结果右移log2位即可。

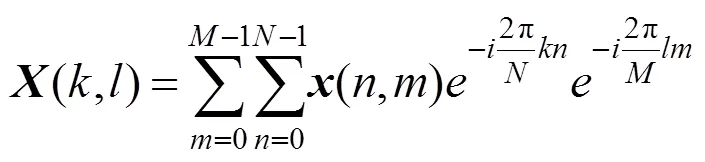

1.2 二维FFT

分辨率×的图像,可以用一个×的矩阵(,)表示,再经过二维FFT运算提取图像频谱。二维FFT可以看成2组一维FFT的组合,即

式(3)可以理解为先对像素矩阵(,)的每一行进行点FFT运算,运算次后得到(,),再对每一列进行点FFT运算,运算次最后得到(,)。二维FFT运算满足可分性,即先进行行变换与先进行列变换对FFT运算结果没有影响。

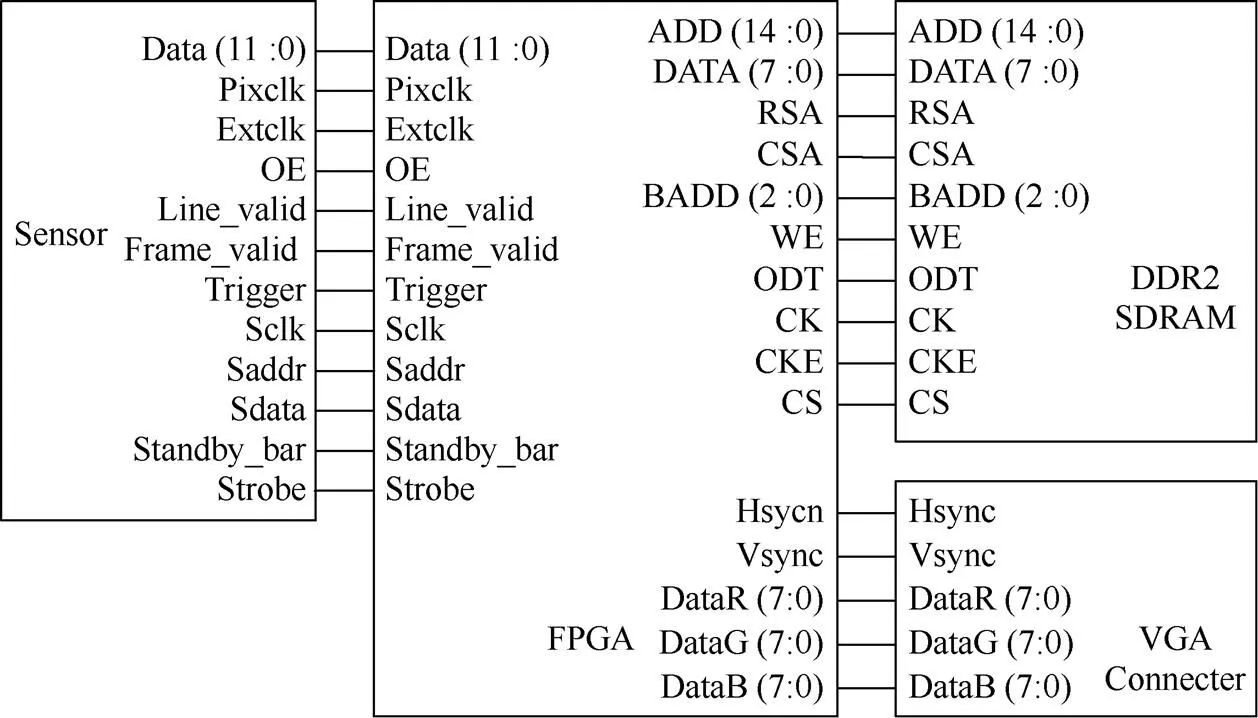

2 硬件设计

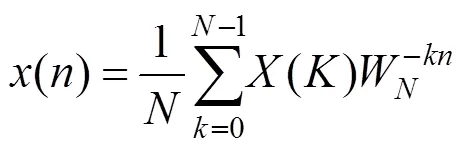

选择Xilinx XC6SLX150-3FGG676I FPGA作为主控芯片。一帧512×512分辨率的256阶灰度图像数据量为256 KB,图像缓存及运算中间数据缓存使用DDR2 SDRAM芯片MT47H256M8。该芯片内部分为8个Bank,每个Bank的容量为 256 Mbit,数据位为8位,地址位为15位。行列地址总线复用,行地址15位,列地址10位通过RAS和CAS信号激活行地址和列地址。部分电路如图2所示。

图2 整体硬件电路

3 逻辑设计

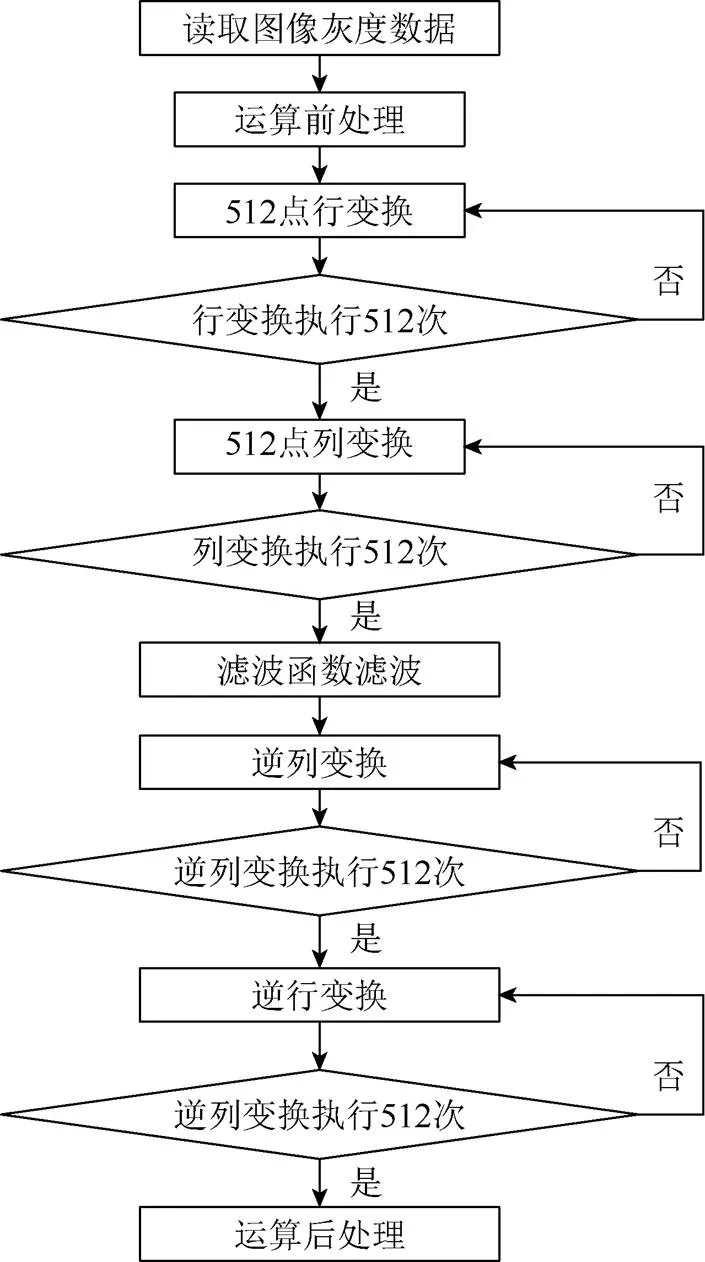

本设计使用模块化设计方案,针对512×512分辨率的256阶灰度图像进行处理。图像的灰度由深到浅用十六进制可表示为00~FF。图像传感器采集回一帧数据,由FPGA先存入SDRAM中,再读回FPGA进行处理,处理完毕后,直接通过VGA接口显示,流程如图3所示。

图3 流程图

3.1 图像数据处理及滤波函数设计

通常图像经过傅立叶变换后,频谱的零点集中在频谱图的四角,不利于后续的滤波处理。为了将频谱原点移至图像中心,可在运算前对图像数据按式(4)进行预处理。得到一组新的图像数据(,),即

该方法在FPGA中只需一个加法器即可实现。步骤如下:

(1) 读取一个8 bit图像数据(,)。

(2) 利用加法器计算+。

(3) 将加法器输出结果的最低位作为该8 bit数据的符号位。

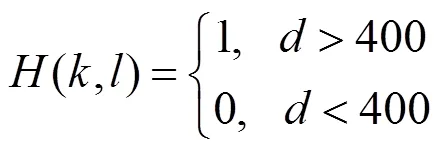

FFT运算完成后,对频谱进行滤波,使用滤波函数(,)乘以频谱,得到滤波后的频谱。

式(5)中为点(,)到频谱中心点的距离的平方。滤波函数逻辑电路如图4所示。

图4 滤波函数逻辑电路

3.2 FFT模块逻辑设计

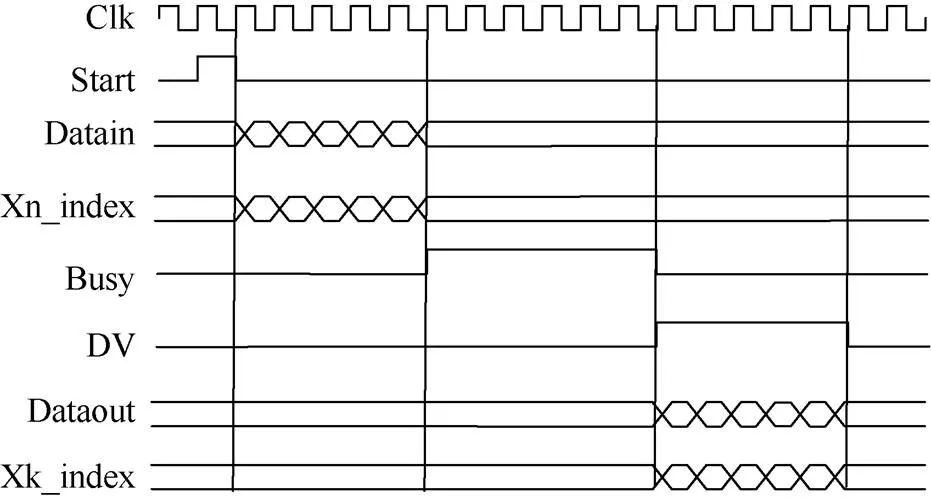

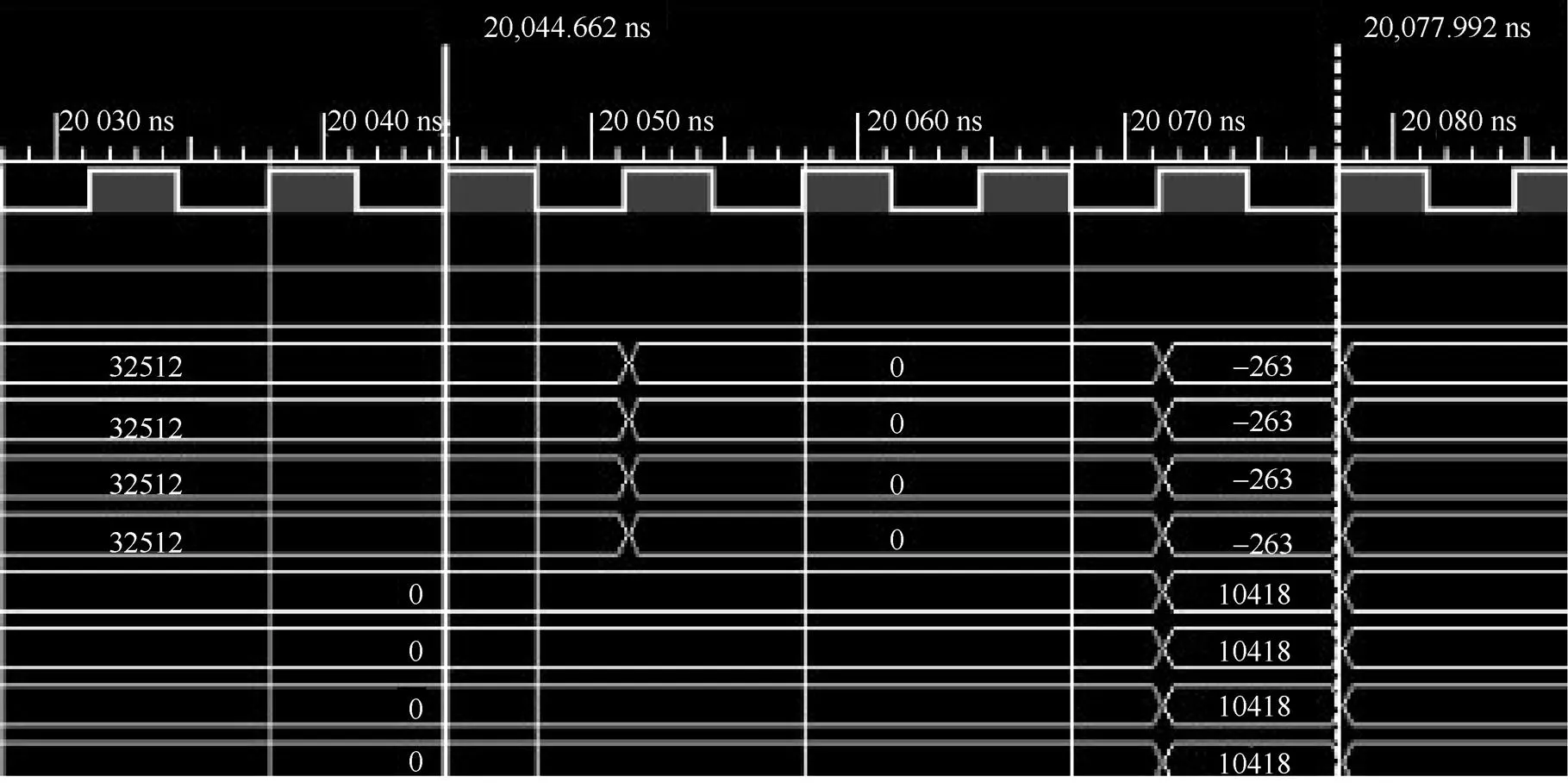

FFT运算单元主要控制信号及标志信号有Start、Busy、DV、及Xn_Index、Xk_Index。Start信号表示一行或一列图像数据开始输入;Busy表示FFT模块正在运算;DV表示开始输出有效数据;Xn_Index、Xk_Index信号是输入输出数据的计数,时序如图5所示。

图5 时序图

512点Radix-2 FFT模块需要进行9级的蝶形运算,用到256个旋转因子。由于旋转因子在数据运算过程中可造成数据位增加并且出现小数,因此需对每级蝶形运算结果进行修正,提取有效数据的整数部分。为防止数据溢出,每级蝶形运算完成后将运算结果乘以缩减因子,缩减因子设置以数据不溢出为标准。旋转因子的比特数是决定快速傅立叶变换精度的重要因素,但是过高的比特数同样会造成运算量的增加,从而减慢运算速度,应当考虑精度和速度折中选择,本设计使用16 bit旋转因子。采用查找表的方式将其存储在FPGA片内ROM中,系统上电时自动进行初始化。单通道FFT模块原理如图6所示。

图6 单通道FFT

4通道FFT由4个单通道FFT并行组成,4通道同步执行512点FFT运算,输入数据为64位,其中每路16位,8位实部、8位虚部,对图像原始数据来说,虚部对应数值为00。

当IFFT变换时,将IFFT的旋转因子加载入旋转因子ROM中。频谱数据乘以高通滤波函数后输入FFT模块,实现FFT模块的IFFT运算功能。极大节约了FPGA片内资源。在IFFT运算完成后,取结果的实部,进行后处理,处理方法与前处理相同,即可得到由频谱恢复后的图像。

3.3 DDR2模块逻辑设计

在HDL设计中生成8个宽度为8 bit,深度为512的BRAM作为待运算数据的缓存。8个BRAM分为2组,一组缓存待运算数据实部,一组缓存待运算数据虚部,8个BRAM由同一个使能信号控制,从而保证4路数据同步传输。并且由于数据缓存时间远小于FFT运算时间,每次BRAM中的数据输入FFT模块后立即从DDR2中读取下一行(列)的数据,用以节约时钟开销。

设计中FFT行与列变换处理单元复用,系统工作时先进行4路行变换,将计算结果(,)回传至DDR2中。128次行变换执行完毕后,通过控制DDR2读数地址,读取(,)列数据缓存入BRAM中,重复4次后,将4组列数据同步输入FFT运算单元进行运算。每次FFT运算完成后,将4路结果经由一个2 KB的FIFO缓存至DDR2中,覆盖对应中间变量(,),运算128次后得到二维FFT变换最终结果(,)。

总体逻辑设计如图7所示。

图7 总体逻辑设计

4 实验结果及分析

为验证本设计的正确性,利用ISE对4路FFT运算单元进行仿真。仿真中通过输入自加数,在控制信号配合下,输出变换后的结果。在Matlab上做相同的FFT运算,以确定FFT运算单元的缩减因子。最后通过实验,实现一帧图像的频谱提取、滤波及反变换。

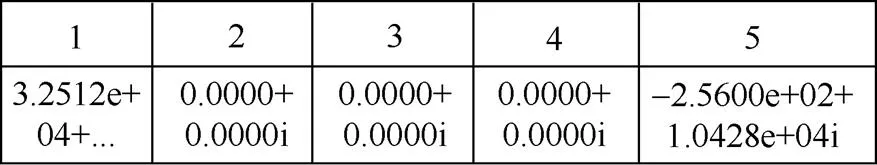

使用Matlab进行傅立叶变换,输入数据为0~127,重复4次共512个数据得到部分结果如图8所示。

图8 Matlab进行FFT运算部分结果

FPGA平台的仿真结果如图9所示,Matlab与FPGA的结果对比见表1。

图9 FFT运算单元部分运算结果

表1 部分运算结果

从表1可以看到FFT运算单元与Matlab的运算结果略有不同,这是因为FFT运算单元截断了运算过程中出现的小数。

通过Matlab的探查计时功能可以看到,进行一帧512×512像素图像FFT运算的时间约为2.019 s;而基于FPGA的4路并行FFT运算单元进行一次512点FFT运算需要3 505个时钟周期,工作频率经过PLL锁相环后倍频在150 MHz,进行一次FFT所需时间约为23.367 μs。进行一次相同运算只需要约7.013 ms远远快于Matlab的运算速度,实时性得到很大提高。运算时间对比见表2。

表2 运算时间

实验设计如下:利用FPGA平台对一帧指纹图像进行截止频率为20的数字高通滤波,输出频谱及其对应的图像。

将原始频谱进行高通滤波后,得到频谱高频部分,如图10(b)所示。再经过IFFT运算后,得到图像纹理特征,如图11(b)所示。

将图10(b)的频谱数据左移4位后,得到增强频谱,如图10(c)所示,反变换后得到边缘增强后的图像,如图11(c)所示。对比图11(a)和图11(c),可以看到处理过后的图像指纹清晰可辨,对比度明显提高。

图10 频谱对比

5 结束语

本文在FPGA基础上从底层实现了一种二维FFT处理器,并应用在图像边缘增强领域,动态提高图像对比度,实现图像的频谱提取、滤波及由频谱提取图像的过程。结果显示该方法实时性高、稳定可靠,而且处理过的图像更加符合人眼的视觉特性,可以满足对图像处理实时性要求较高场合的应用需求。

[1] 康牧. 图像处理中几个关键算法的研究[D]. 西安: 西安电子科技大学, 2009.

[2] 吴诗婳, 吴一全, 周建江. 基于NSST和改进数学形态学的遥感图像目标边缘提取[J]. 图学学报, 2017, 38(4): 523-530.

[3] 刘丽, 匡纲要. 图像纹理特征提取方法综述[J]. 中国图象图形学报, 2009, 14(4): 622-635.

[4] 张勇. 傅里叶变换在数字图像处理中的应用[J]. 廊坊师范学院学报: 自然科学版, 2015, 15(3): 25-27.

[5] 周浦城, 周远, 韩裕生. 视频图像去雨技术研究进展[J]. 图学学报, 2017, 38(5): 629-646.

[6] 杨军, 于艳艳, 陈成, 等. 基于FPGA的二维FFT处理器的研究与设计[J]. 云南大学学报: 自然科学版, 2013, 35(6): 750-755.

[7] 张丽君. 大点数FFT的二维算法FPGA并行实现[J]. 无线电通信技术, 2013, 39(3): 86-88.

[8] 刘冀川. 实数二维FFT及其改进算法的FPGA实现[J]. 无线电通信技术, 2014, 40(3): 94-96.

[9] NGUYEN N H, KHAN S A, KIM C H, et al. A high-performance, resource-efficient, reconfigurable parallel-pipelined FFT processor for FPGA platforms [J]. Microprocessors and Microsystems, 2018, 60(7): 96-106.

2D-FFT Image Edge Enhancement Design Based on FPGA

REN Yong-feng, WU Hao-nan, CHU Cheng-qun, JIAO Xin-quan

(National Key Laboratory for Electronic Measurement Technology, North University of China, Taiyuan Shanxi 030051, China)

When processing the information like images, we find that image details can often convey more information, and that is why people are more concerned with images details. However, under the condition of unsatisfactory illumination, the images collected by sensors are usually with low contrast and difficult to distinguish the details. To solve the above problems, an image edge extraction and enhancement method based on field-programmable gate array (FPGA) is proposed. Four parallel 512×512-point fast Fourier transform (FFT) processors are designed by modular design, and the resource consumption in FPGA is reduced by multiplexing FFT modules. At the same time, high-pass filtering algorithm and inverse fourier transform algorithm of image spectrum are realized. The simulation and experiment show that the method is effective, reliable and real-time, and it can also meet the needs of industrial image processing.

field-programmable gate array (FPGA); fast Fourier transformation (FFT); edge enhancement; frequency domain; wave filtering

TP 791

10.11996/JG.j.2095-302X.2019010137

A

2095-302X(2019)01-0137-06

2018-06-05;

2018-09-12

国家自然科学基金项目(61727804)

任勇峰(1968-),男,山西中阳人,教授,博士,博士生导师。主要研究方向为测试计量技术、电路与系统。E-mail:renyongfeng@nuc.edun.cn

焦新泉(1968-),男,江苏泰州人,副教授,博士,硕士生导师。主要研究方向为高速数据采集存储。E-mail:jiaoxinquan@nuc.edu.cn