绝缘体上硅金属氧化物半导体场效应晶体管中辐射导致的寄生效应研究∗

2018-12-02彭超恩云飞李斌雷志锋张战刚何玉娟黄云

彭超 恩云飞 李斌 雷志锋 张战刚 何玉娟 黄云

1)(工业和信息化部电子第五研究所,电子元器件可靠性物理及其应用技术重点实验室,广州 510610)2)(华南理工大学电子与信息学院,广州 510006)(2018年7月16日收到;2018年8月20日收到修改稿)

基于60Co γ射线源研究了总剂量辐射对绝缘体上硅(silicon on insulator,SOI)金属氧化物半导体场效应晶体管器件的影响.通过对比不同尺寸器件的辐射响应,分析了导致辐照后器件性能退化的不同机制.实验表明:器件的性能退化来源于辐射增强的寄生效应;浅沟槽隔离(shallow trench isolation,STI)寄生晶体管的开启导致了关态漏电流随总剂量呈指数增加,直到达到饱和;STI氧化层的陷阱电荷共享导致了窄沟道器件的阈值电压漂移,而短沟道器件的阈值电压漂移则来自于背栅阈值耦合;在同一工艺下,尺寸较小的器件对总剂量效应更敏感.探讨了背栅和体区加负偏压对总剂量效应的影响,SOI器件背栅或体区的负偏压可以在一定程度上抑制辐射增强的寄生效应,从而改善辐照后器件的电学特性.

1 引 言

随着绝缘体上硅(silicon on insulator,SOI)技术广泛地应用在航天领域,其辐射效应受到了广泛的关注[1−4].当电子元器件长期工作在辐射环境下时,伴随着辐射剂量不断累积将产生总剂量效应,表现为器件介质层中形成大量的陷阱电荷,最终导致器件性能的永久退化[5,6].由于SOI器件全介质隔离的结构,使得其对总剂量效应尤其敏感.

SOI金属氧化物半导体场效应晶体管(metaloxide-semiconductor filed-effect transistor,MOSFET)器件中主要的介质层包括栅氧、浅沟槽隔离(shallow trench isolation,STI)和绝缘氧化埋(buried oxide,BOX)层.研究表明辐射感应的氧化层陷阱电荷正比于氧化层厚度[7].在深亚微米工艺下,器件的栅氧变得非常薄(小于10 nm),总剂量辐照在栅氧层中产生的影响有限,甚至可以忽略不计.但是STI和BOX氧化层通常都很厚,对总剂量效应非常敏感[8].国内外开展了大量STI和BOX层陷阱电荷对器件性能影响的研究,但大部分工作都是针对体硅器件单独研究STI氧化层对总剂量效应的贡献[9−13],或者针对无边缘的SOI器件单独研究BOX层对总剂量效应的贡献[14−17],而且以辐照后器件电学性能退化的定性分析为主.实际上SOI器件的总剂量效应来自于STI和BOX层中陷阱电荷共同作用的结果,辐照后器件性能退化可能来自于两者的共同贡献,也可能仅仅来自于其中之一,对其加以区分将有助于开展针对性的加固措施.

SOI MOSFET器件中包含STI边缘寄生晶体管和背栅寄生晶体管.尽管半导体器件工艺会尽量削弱这些寄生效应[18],但辐射感应的陷阱电荷却会导致这些寄生效应的增强,从而对主晶体管的电学性能产生影响.本文重点研究了辐射对SOI器件中寄生效应的影响.针对不同尺寸SOI器件中观察到的不同性能退化现象,结合物理模型和TCAD器件仿真给出了详细的定性和定量分析,确定了导致SOI器件性能退化的机制;分别研究了背栅和体区加负偏压对器件总剂量效应的影响.

2 实验描述

实验样品采用130 nm部分耗尽SOI工艺制造,器件顶层硅厚度为80 nm,BOX层厚度为145 nm.因为在同一工艺下输入/输出器件比核心器件对总剂量效应更敏感,其性能退化更加明显,因此本文实验所用器件均为输入/输出N型金属氧化物半导体(n-channel metal-oxide-semiconductor,NMOS)器件,宽长比为10µm/10µm,10µm/0.35µm,0.15µm/10µm,0.15µm/0.35µm.其栅氧厚度约为7 nm,工作电压为3.3 V.场氧隔离采用高密度等离子体氧化物填充的STI.STI的底部与BOX层直接相连,构成全介质隔离结构.器件采用T型栅结构来实现体区引出.器件沿沟道长度和宽度方向的截面图如图1所示.该器件的源漏区贯穿整个顶层硅,与BOX层相连.由图1(b)可看到,除了前栅主晶体管MFG外,该器件结构还包含一个背栅寄生晶体管MBG和一个STI寄生晶体管MSTI.寄生晶体管MBG和MSTI分别以BOX层和STI氧化层为栅氧,与主晶体管有相同的沟道长度.

辐照实验采用60Co γ射线作为辐照源.剂量率为100 rad(Si)/s.辐照实验所有测试样品采用双列直插陶瓷封装.辐照过程中器件处于ON偏置状态,即栅端加3.3 V正偏压,漏端、源端、体接触端和背栅接地.辐照前后利用Keithley 4200半导体参数分析仪测试器件的转移特性曲线.所有测试在30 min内完成以避免辐照退火效应的影响;整个辐照和测试过程均在室温下进行.本文中所有的阈值电压均根据峰值跨导法提取,即器件阈值电压为

其中Vg和Id为跨导最大值对应的栅端电压和漏端电流,Vd为器件工作在线性区的漏端电压.

图1 SOI MOSFET器件结构 (a)沿沟道长度截面图;(b)沿沟道宽度截面图Fig.1.Device structure of SOI MOSFET:(a)Cross-section along channel length;(b)cross-section along channel width.

3 实验结果与讨论

3.1 辐射增强的寄生效应

图2显示了四种不同宽长比的SOI NMOS器件经ON偏置辐照后,前栅的转移特性和跨导特性随辐照剂量的变化.在转移特性测试过程中,器件背栅和体接触接地.经30 krad(Si)辐照后,器件关态漏电流(对应Vfg=0 V时的Ids)显著增加,特别是对于宽长比为10µm/0.35µm的器件.但此时的泄漏电流受到前栅电压的调制,表现为转移特性曲线的亚阈值区出现“驼峰”现象[19].在30 krad(Si)以上,泄漏电流随着总剂量的增加而继续增加,而且亚阈值区的“驼峰”现象逐渐消失,表现为泄漏电流几乎不受前栅电压的控制.图3显示了辐照后器件关态漏电流随总剂量的变化.在80 krad(Si)以下(对于10µm/0.35µm的器件为50 krad(Si)),关态漏电流近似随总剂量呈指数增加.而在80 krad(Si)以上,关态漏电流随总剂量缓慢增加,近似趋于饱和.当总剂量达到100 krad(Si)时,10µm/0.35µm,0.15µm/0.35µm,0.15µm/10µm和10µm/10µm四种不同尺寸器件的关态漏电流相比于辐照前分别增加了5.1×106,6.4×106,4.0×105和1.4×106倍.

图2 不同宽长比(W/L)SOI器件辐照前后的转移特性和跨导曲线 (a)W/L=10µm/0.35µm;(b)W/L=0.15µm/0.35µm;(c)W/L=0.15µm/10µm;(d)W/L=10µm/10µmFig.2.Transfer characteristics and transconductances of SOI n-MOSFETs with different width-length-ratio(W/L)before and after irradiation:(a)W/L=10µm/0.35µm;(b)W/L=0.15µm/0.35µm;(c)W/L=0.15µm/10µm;(d)W/L=10µm/10µm.

图3 归一化的关态漏电流随总剂量的变化,其中归一化的关态漏电流定义为辐照前后的关态漏电流之比Fig.3.Normalization o ff-state leakage current as a function of total dose. The normalization o ff-state leakage is defined as Idsat Vfg=0 after irradiation divided by the value before irradiation.

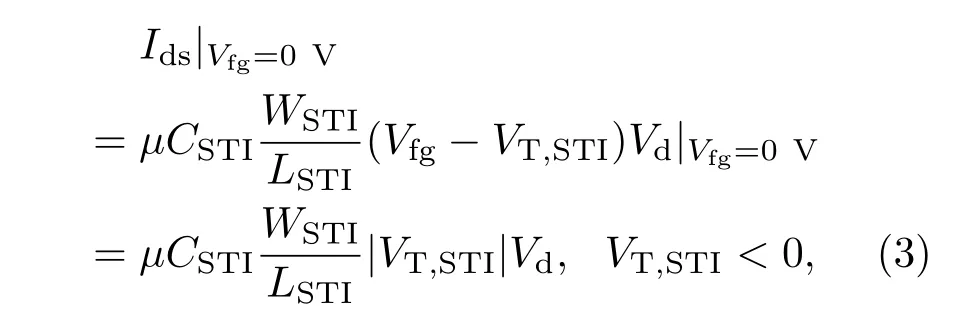

辐照后关态漏电流的增加与寄生晶体管的开启有关.如图1所示,一个SOI MOSFET可视为主晶体管MFG,STI寄生晶体管MSTI和背栅寄生晶体管MBG的并联.辐照在STI氧化层或BOX层中产生的正陷阱电荷会降低寄生晶体管的阈值电压,使得在Vfg=0 V时本来应该处于关断状态的寄生晶体管无法关断,从而产生较大的关态漏电流.由于本实验中观察到的关态漏电流明显受前栅电压控制,辐照后关态漏电流的增加更可能来自于MSTI的开启[19].这是因为器件多晶硅栅会覆盖沟道附近的STI氧化层区域,前栅电压的电场会延伸到STI氧化层,从而对STI寄生晶体管产生调制作用,但其对背栅寄生晶体管的影响可以忽略不计.当总剂量较小时,寄生晶体管MSTI的阈值电压漂移也较小,在Vfg=0 V时寄生晶体管还未完全开启,工作在亚阈值区.则此时器件关态漏电流可表示为[20]

当总剂量达到80 krad(Si)以上时,寄生晶体管MSTI完全开启,此时关态漏电流可表示为

其中VT,STI为STI寄生晶体管的阈值电压.可以看到,当总剂量较小、寄生晶体管未完全开启时,VT,STI随总剂量的增加而减小,关态漏电流表现为指数增加.当总剂量较大、寄生晶体管完全开启时,VT,STI随总剂量的增加而减小,关态漏电流表现为线性增加并趋于饱和.这与实验观察到的结果完全一致.

由图2的跨导曲线可以看到,10µm/0.35µm,0.15µm/0.35µm和0.15µm/10µm三种尺寸的器件出现了明显的阈值电压漂移.100 krad(Si)时,三种器件的阈值电压漂移分别为−41.1,−170.5和−83.8 mV.阈值电压的减小同时导致了跨导峰值的增加.值得注意的是,10µm/10µm的器件在辐照后没有出现类似的跨导变化,阈值电压的漂移几乎可以忽略.辐照导致的栅氧正陷阱电荷积累会导致器件的阈值电压负向漂移.10µm/10µm的器件辐照后没有出现跨导和阈值退化,证明栅氧中的辐射感应陷阱电荷可以忽略不计.由于四种器件具有相同的栅氧厚度,这也说明其他三种器件中观察到的阈值电压漂移不是来源于栅氧的辐射感应陷阱电荷.

在0.15µm/0.35µm和0.15µm/10µm两种窄沟道器件中观察到了最明显的阈值电压漂移.该阈值漂移可能来源于STI氧化层陷阱电荷导致的耗尽区电荷共享,如图4(a)所示.对于一个SOI器件,其导通时由前栅电压控制的耗尽区宽度为Xdm.辐照后,STI氧化层中的正陷阱电荷也会导致附近的有源区耗尽,该耗尽区宽度记为XSTI.在器件沟道宽度方向靠近STI的区域,两个耗尽区之间存在电荷共享,这意味着前栅耗尽区并不完全由前栅电压控制,有一部分受STI氧化层中的辐射感应陷阱电荷控制.假设无STI电荷共享时的栅控耗尽区为矩形区域,面积为(W×Xdm),耗尽区电荷量为Qb;共享耗尽区面积记为S0,考虑电荷共享时的有效栅控耗尽区面积则为(W×Xdm−S0),有效栅控耗尽区电荷量为Q′b.则有

辐照后,因电荷共享导致的阈值电压漂移可表示为

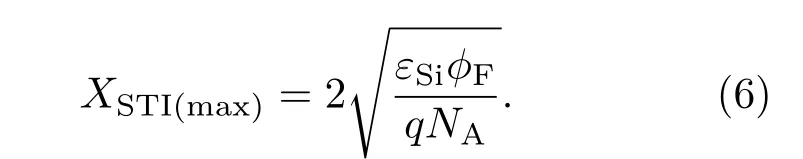

其中,W为器件沟道宽度;εSi为硅的介电常数;NA为器件体区掺杂浓度;ϕF为费米电势.XSTI会随着总剂量的增加而增加,因此辐射导致的阈值电压漂移也会随总剂量的增加而增加.当STI寄生晶体管完全开启时,XSTI达到最大值,可由下式计算:

图4 (a)STI氧化层陷阱电荷导致的耗尽区电荷共享;(b)BOX层陷阱电荷导致的背栅耦合Fig.4.(a)Depletion region charge sharing induced by STI trapped-charge;(b)back gate coupling induced by BOX trapped-charge.

实验器件的体区掺杂浓度NA近似为3×1017cm−3.根据(5)和(6)式,可计算沟道宽度W=0.15µm的器件中因STI电荷共享导致的最大阈值电压为−125.4 mV;对于沟道宽度W=10µm的器件则为1.9 mV,可以忽略不计.这与实验观察到的结果一致.0.15µm/10µm器件观察到的阈值漂移小于−125.4 mV,是因为其STI寄生晶体管还没有完全开启.0.15µm/0.35µm器件观察到的阈值漂移大于−125.4 mV,是因为除了STI电荷共享外还有其他机制导致阈值电压漂移,将在下文讨论.

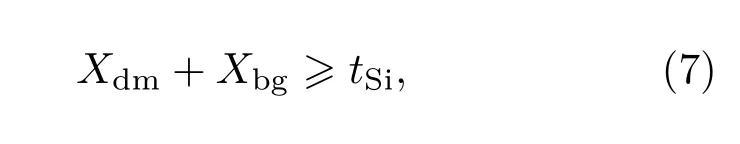

辐照后BOX层中的正陷阱电荷也会导致其附近的体区耗尽,形成背栅耗尽区Xbg,如图4(b)所示.在器件阈值附近,如果背栅耗尽区Xbg与前栅耗尽区Xdm重叠,则部分耗尽器件变为全耗尽器件,即

此时,BOX层中的正陷阱电荷会耦合到前栅,导致器件阈值电压负向漂移.对于本实验所选用的体区掺杂浓度为3×1017cm−3器件,前栅和背栅的最大耗尽区宽度约为62.2 nm.两者之和大于器件顶层硅厚度tSi(80 nm),理论上满足发生背栅耦合的条件.Xbg会随着BOX层中辐射感应陷阱电荷密度的增加而增加,直到达到最大耗尽区宽度.只有当Xbg增加到满足(7)式时,背栅耦合才会发生,即观察到阈值电压漂移.

图5(a)和图5(b)显示了ON偏置下不同栅长的SOI器件中辐射感生电荷密度在整个BOX层中的分布.该结果由Sentaurus TCAD仿真得到[21].图中黄色区域代表辐射感生电荷较多的区域.可以看到,辐射感生电荷主要集中在BOX层与硅的界面附近.其中沟道区以下BOX层与体区界面附近的陷阱电荷对器件总剂量效应的影响最大.相比于长沟道器件(栅长为1µm),栅长为0.35µm的短沟道器件中,BOX层辐射感应电荷更加集中在此区域.图5(c)显示了BOX层与体区界面以下10 nm处,BOX层中的辐射感生电荷产生率沿沟道长度方向的分布.对应短沟道和长沟道器件,沟道中心位置以下的BOX层中辐射感生电荷产生率分别为1.0×1014cm−3·s−1和4.0×1013cm−3·s−1. 在相同的总剂量下,短沟道器件BOX层中更多的陷阱电荷形成,导致了短沟道器件更易发生背栅耦合.这可以解释为何沟道长度为0.35µm的器件中观察到了背栅耦合导致的阈值电压漂移,而沟道长度为10µm的器件没有观察到.

图5 BOX层中辐射感应电荷密度分布 (a)栅长L为0.35µm的器件;(b)栅长L为1µm的器件;(c)不同栅长器件中对应于切割线位置处的辐射感应电荷密度对比,其中横坐标为归一化距离,0和1分别对应于靠近源和漏的位置Fig.5.Radiation-induced charge distribution in BOX:(a)Device with gate length of 0.35µm;(b)device with gate length of 1µm;(c)radiation-induced charge density at the cutting line for devices with different gate lengths.The x-axis is normalization distance,where 0 and 1 correspond to the positions near source and drain,respectively.

可以得到结论,10µm/0.35µm器件辐照后的阈值电压漂移主要来源于背栅耦合;0.15µm/10µm器件的阈值漂移来源于STI的电荷共享;而0.15µm/0.35µm器件受到两种效应的共同作用,因此出现了最严重的阈值电压退化.同样工艺下,小尺寸器件对总剂量效应更敏感.

3.2 背栅负偏压对寄生效应的影响

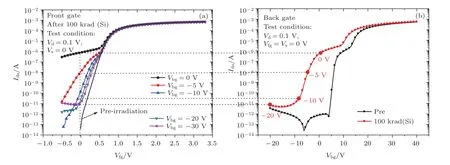

氧化层中辐射感应的正陷阱电荷导致了器件性能的退化,因此可以考虑在背栅施加负偏压来抵消正陷阱电荷的影响,从而削弱寄生效应的影响.图6(a)为经100 krad(Si)辐照后,10µm/0.35µm的SOI器件在不同背栅偏压下的前栅转移特性曲线.在转移特性测试过程中,器件体接触接地.辐照后,背栅负偏压能有效抑制辐照诱发的器件泄漏电流.在−10 V的背栅负偏压下,器件关态漏电相比于未加负偏压的器件下降了四个数量级.

图6(b)显示了该器件辐照前后的背栅转移特性曲线.在测试过程中,器件前栅和体接触均接地.该背栅转移特性曲线为背栅寄生晶体管和STI寄生晶体管转移特性曲线的叠加.由于STI寄生晶体管阈值电压更低,因此会先于背栅寄生晶体管开启,表现为背栅转移特性曲线上出现一个“驼峰”.辐照后,STI和BOX层中的大量正陷阱电荷分别导致STI和背栅寄生晶体管I-V曲线出现了明显的负向漂移.当总剂量达到100 krad(Si)时,正是因为STI寄生晶体管在Vbg=0 V时开启,其开启电流叠加到正栅主晶体管,使得主晶体管关态漏电流增加.由图6(b)可以看到,如果在−10—0 V范围内给背栅施加一个负偏压,可以使STI寄生晶体管由开启状态进入亚阈值状态,使得叠加到主晶体管的关态漏电流降低(如图6(a)所示).

图6 (a)100 krad(Si)辐照后不同背栅偏压下10µm/0.35µm器件的前栅转移特性曲线;(b)10µm/0.35µm器件辐照前后的背栅转移特性曲线Fig.6.(a)Front gate transfer characteristics of 10µm/0.35µm device with different back gate biases after 100 krad(Si)irradiation;(b)back gate transfer characteristics of 10µm/0.35µm device before and after irradiation.

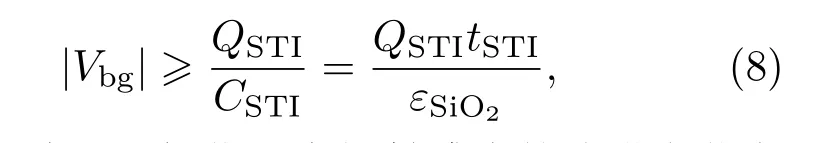

为了中和STI氧化层正陷阱电荷的影响,抑制STI寄生晶体管的开启,所加的背栅负偏压须满足以下条件:

其中QSTI为STI氧化层中辐射感应的陷阱电荷密度,CSTI为STI寄生晶体管等效栅电容,tSTI为等效栅氧厚度.由于STI氧化层的特殊形貌,STI寄生晶体管的等效栅氧厚度并不是恒定值.如图7所示,当背栅加偏压时,其产生的电场开始于背栅,终止于体区,可近似认为以图中O点为圆心呈圆弧分布[22].因此,STI寄生晶体管的等效栅氧厚度可以认为是沿电场方向的一段圆弧,如图7中的tSTI,则有

其中td为从O点到STI侧壁某点的距离,如图7所示.由(8)和(9)式可以得到:在靠近背栅的STI底部区域,td较小,为了抑制STI寄生晶体管的开启所需加的背栅负偏压也小;在靠近STI顶部区域,td逐渐增加,为了抑制漏电所需的背栅负偏压也越来越大.在本实验中,背栅加−10 V的偏压时,可以有效抑制STI底部区域的导电沟道.但背栅偏压对STI顶部区域的影响要小得多,靠近STI顶部区域的寄生晶体管仍然开启,从而产生泄漏电流.由于靠近前栅,该泄漏电流明显受到前栅电压的调制,因此表现为器件前栅转移特性曲线亚阈值区出现“驼峰”现象.该实验结果也从侧面证明,STI底部区域的寄生导电是导致大剂量下器件关态漏电流增加的最主要原因,因此背栅负偏压抑制了STI底部区域寄生晶体管开启时器件的关态漏电流大幅下降.

由图6(a)可以看到,在Vbg=−5 V下测试时,由于背栅耦合导致的阈值电压负向漂移也会消失.实验结果表明,可以利用背栅加负偏压来中和BOX层正陷阱的影响.根据背栅耦合发生的条件可以推导出,当所加背栅负偏压满足如下条件时,能完全抑制辐射导致的背栅耦合效应:

其中CBOX为背栅寄生晶体管的单位面积栅电容;QBOX为BOX层中的辐射感应等效陷阱电荷密度;Qc为导致背栅耦合发生的临界电荷密度,即当BOX层中的陷阱电荷密度为Qc时,SOI器件正好进入全耗尽状态,满足Xdm+Xbg=tSi.对于实验用器件,可计算Qc=8.54×10−8C/cm2.根据100 rad(Si)辐照后背栅寄生晶体管的阈值电压漂移,可提取出QBOX为1.19×10−7C/cm2.由(10)式可计算,经100 krad(Si)辐照后,在背栅加绝对值大于1.4 V的负偏压即可消除辐射导致的背栅耦合效应.

图7 背栅的STI寄生晶体管示意图Fig.7.STI parasitic transistor at back gate.

3.3 体区负偏压对寄生效应的影响

辐照后,STI寄生晶体管阈值电压负向漂移,最终导致器件关态漏电流增加.STI寄生晶体管与主晶体管共用体区,因此可以考虑在体区加负偏压,利用衬偏效应提高STI寄生晶体管的阈值,从而削弱总剂量效应的影响.

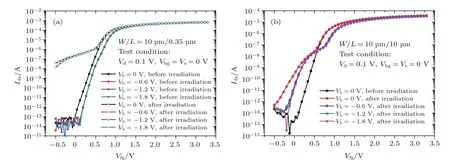

图8 辐照前和50 krad(Si)辐照后不同体区偏压下前栅器件的转移特性曲线 (a)器件尺寸10µm/0.35µm;(b)器件尺寸10µm/10µmFig.8.Transfer characteristics of the front gate device with different body biases before and after 50 krad(Si)irradiation:(a)10µm/0.35µm device;(b)10µm/10µm device.

图8显示了辐照前后不同体区偏压下SOI器件的转移特性曲线.对于10µm/0.35µm的器件,辐照前Vb<0时的I-V曲线相比于Vb=0时发生了正向漂移.由于衬偏效应的影响,体区加负偏压使得器件反型时的耗尽层宽度增加,从而导致了器件阈值电压增加.当Vb=−0.6 V时前栅耗尽区已经增加到与顶层硅厚度相等,器件处于全耗尽状态,|Vb|的增加无法导致耗尽区的继续增加,I-V曲线不随着|Vb|增加继续向右漂移.辐照后体区负偏压对10µm/0.35µm器件的转移特性几乎无影响.根据前面的分析,辐照后10µm/0.35µm的器件已经处于全耗尽状态,体区负偏压已经无法实现耗尽区宽度的调制,因此I-V曲线也没有出现类似辐照前的正向漂移.与短沟道器件不同,10µm/10µm的器件体区加负偏压会导致辐照后I-V曲线的正向漂移.这进一步验证了前面的结果,10µm/10µm器件的体区在辐照后没有全耗尽.因此能通过体区负偏压调制耗尽区的宽度,从而增加正栅主晶体管和STI寄生晶体管的阈值电压.STI寄生晶体管阈值的增加,导致50 krad(Si)辐照后器件关态漏电流减小了一个数量级.但由于SOI器件的顶层硅厚度(即体区厚度)为固定值且很薄,衬偏效应对STI寄生晶体管阈值电压的调制范围非常有限.

图9 (a)辐照后沟道宽度为10µm的器件体区接地和接负偏压时耗尽区的仿真结果;(b)体区接地和加负偏压时,沿着切割线A和B处的辐射感应反型层电子密度;切割线A对应于STI边缘,切割线B对应于远离STI边缘的体区内部,其中0µm对应于前栅沟道,0.1µm对应于背栅沟道附近Fig.9.(a)Simulation results of the deletion regions with body biased at 0 V and−1 V after irradiation;(b)electron density along cutting line A and B with different body biases.The cutting line A corresponds to the STI sidewall,cutting line B corresponds to the region far away from STI sidewall.Distance of 0µm corresponds to the front gate channel,and distance of 0.1µm corresponds to the BOX/body interface.

为了进一步验证体区负偏压对辐射效应的影响,图9(a)给出了辐照后沟道长度为10µm的器件体区接地和接负偏压时耗尽区的TCAD仿真结果.图中显示的仿真结构为沿沟道宽度方向的纵向切面二维结构.仿真过程中前栅和背栅接地.STI/体区和BOX/体区界面加上面密度为1×1012cm−2的固定正电荷用以模拟辐照感应的氧化层陷阱电荷.可以看到,STI和BOX中辐照感应的正陷阱电荷会导致STI边缘和背栅附近的体区耗尽甚至反型,从而形成寄生导电沟道.当体区加−0.6 V的偏压时,耗尽区展宽,导致此时中性体区消失,部分耗尽器件变成全耗尽.此时体区耗尽层宽度即为体区厚度,不受体区电压的调节.图9(b)显示了体区负偏压对STI边缘和背沟道附近感应电子密度的影响.可以看到,在相同的陷阱电荷密度下,STI边缘底部区域附近的电子密度远大于顶部区域和BOX附近的电子密度.这是因为STI底部尖角导致电场的聚集,较大的电场强度导致更多的反型电子形成.这也说明STI寄生晶体管更易反型,侧面验证了辐照后器件的关态漏电流增加主要是由STI寄生导电造成的.体区加−0.6 V偏压时,STI边缘顶部区域附近的感应电子密度有所降低,而底部区域附近的感应电子密度与体区接地时的相差不多,这证明在STI寄生晶体管完全开启(强反型)时,体区负偏压对STI寄生晶体管的耗尽区调制非常有限.相对而言,体区负偏压对背栅寄生晶体管耗尽区的调制作用更明显,因此背沟道寄生导电有明显的削弱.

4 结 论

本文针对不同尺寸的SOI器件开展了60Co γ射线总剂量辐照实验.所有尺寸的器件在辐照后都出现了关态泄漏电流的增加,这与STI寄生晶体管的开启有关.在总剂量较小时,STI寄生晶体管处于亚阈值状态,导致关态漏电流随总剂量呈指数增加;当总剂量足够大时,STI寄生晶体管完全开启,关态漏电流逐渐趋于饱和.辐射导致的阈值电压漂移呈现出明显的器件尺寸相关性.窄沟道器件因STI陷阱电荷共享产生明显的阈值电压漂移,短沟道器件的阈值漂移则来自于背栅阈值耦合,而大尺寸器件几乎无阈值电压漂移.SOI器件背栅负偏压能有效中和氧化层陷阱电荷的影响,对器件关态漏电流和背栅耦合导致的阈值电压漂移有一定的改善作用.体区负偏压也能对寄生晶体管的阈值电压进行调制,达到器件加固的目的,但受限于顶层硅的厚度,该调制作用非常有限.