基于动力学校对的三明治薄膜芯片设计制造*

2018-09-11叶佳佳凌新生袁志山

叶佳佳, 凌新生, 袁志山

(东南大学 机械工程学院 江苏省微纳生物医疗器械设计与制造重点实验室,江苏 南京 211189)

0 引 言

第四代基因测序技术通过在纳米孔传感器芯片两侧施加电压,使得DNA由负极向正极移动,在通过纳米孔时形成占位,使得其离子电流发生改变[1],再由膜片钳等设备测得电流变化,从而实现分子测序的目的。考虑到DNA分子在溶液中的热运动,以及纳米孔中复杂的流体运动,DNA的过孔过程不是单调或单向的,说明了在不抑制DNA扩散运动下,使用纳米孔实现DNA单碱基测序是不可能实现的,这是热力学第二定律在测序问题上的体现。除此之外,纳米孔技术还存在客观条件的限制:纳米孔的厚度[2,3]和现有膜片钳电流放大器的频率带宽的限制。在不降低DNA扩散系数的情况下,现行的纳米孔测序技术基本无法实现单分子测序[4]。Ling X S提出的利用纳米孔作为动力学校对的机理[5]来测量断链杂交探针,给基于固态纳米孔的DNA碱基序列的检测带来了新的希望。通过磁镊来克服热运动之后在双层纳米孔芯片进行短杂交探针校对实验,在理论上能满足单分子测序要求。本文基于动力学校对原理,设计制造出了三明治结构的双层纳米孔芯片,在双氮化硅纳米孔孔厚度满足DNA测序要求的同时,还增加了较厚的氧化硅层减小电容值,进一步控制噪声,便于后续的信号分析,且制造工艺简单、成本低,能实现芯片的大规模生产,为纳米孔DNA测序技术能满足日常使用提供了基础硬件保障。

1 多层薄膜结构设计

由于不同材料的热膨胀系数(α)不同,晶格不匹配,生长条件等因素,几乎所有的薄膜都会存在残余应力。因此,在设计薄膜材料和厚度时,必须要考虑到应力的影响,以期得到低应力、平整无缺陷的高质量薄膜。在微机电系统(micro-electro-mechanical system,MEMS)薄膜沉积工艺中产生的应力主要分为外应力和内应力两类。外应力中,由于热膨胀系数引起的热应力最为常见,称为双金属效应(bi-metal effect)[6]。薄膜中热应力的原因及其影响如图1所示。

图1 薄膜中的残余张应力和压应力

热应变的计算公式为

εth=(αf-αs)·ΔT

(1)

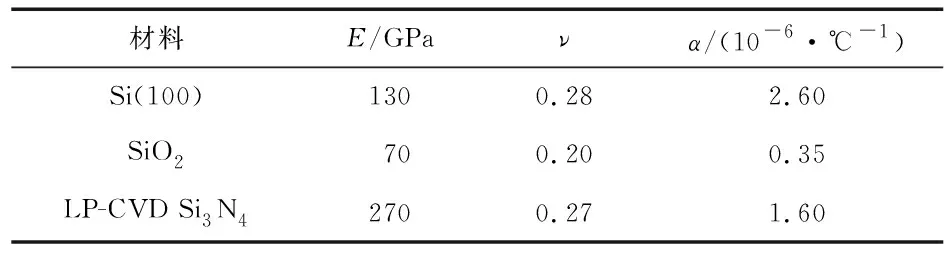

式中αf为膜的热膨胀系数,αs为衬底的热膨胀系数,ΔT为沉积温度与室温之差。σf<αs,预计会产生压应力,如果σf>αs,则会出现张应力。本文沉积温度为800 ℃,室温27 ℃。SiN,SiO均为各向同性材料,其力学性能参数如表1所示。

表1 MEMS材料的力学性能

基于以上,设计了在衬底厚度为430 μm的硅基片上沉积总厚度为600 nm的薄膜,共5层,从基体往上分别为Si3N4,SiO2,Si3N4,此3层为结构层,厚度分别为22,20,45 nm,用于测序和校对。在结构层表面沉积牺牲层SiO2,厚度为300 nm,这个厚度能有效地减小电容值,降低测序信号噪声,提高信噪比。在SiO2表面沉积 150 nm厚度的Si3N4牺牲层,作为后续腐蚀步骤的掩膜。由于两种材料的热膨胀系数不同,拉力和压力交替产生抵消,释放基体后能减小应力应变,减小弯曲变形。依据前述公式对各层薄膜进行应力计算分析如下:

第1层Si3N4:ε1=-7.73×10-4,σ1=-2.8×102MPa,负号为压应力,硅衬底表现出微凸形态,如图1(b)所示。因为衬底的厚度远远大于薄膜,因此这里可以看作衬底是水平的,没有发生形变。

第2层SiO2:ε2=-1.82×10-3,σ2=-1.6×102MPa。

第3层Si3N4:ε3=1.57×10-4,σ3=58 MPa。

第4层SiO2:ε4=-9.43×10-4,σ4=-82 MPa。

第5层Si3N4:ε5=-9.2×10-4,σ5=-3.4×102MPa。

和热应力相比,对内应力的研究比较缺乏,其在厚度方向产生的应力一般不均匀,会产生应力梯度[7]。对本征内应力产生的机理尚无明确的定论,大体上可用两种模型即体积变化模型和表面效应模型解释。内应力一般为张应力,且随着厚度的增加会进一步减小,可以通过退火消除一部分,但要完全消除需要极高的温度,这对于生产设备来说是难以承受的。

2 三明治结构薄膜制造工艺

三明治结构Si3N4薄膜制造工艺如图2所示。

图2 悬空三明治结构芯片工艺流程

图2(a)为芯片衬底硅基底,n型硅片,晶向面为(100);图2(b)为由低压化学气相沉积(low pressure-chemical vapor deposition,LP-CVD)方法制造出Si3N4/SiO2/Si3N4/SiO2/Si3N4结构多层薄膜;图2(c)利用反应离子刻蚀(reactive ion etching,RIE)转移掩模图形,得到基体释放窗口;图2(d)为由氢氧化钾(KOH)、氢氟酸(HF)湿法腐蚀得到悬空三明治结构薄膜。

2.1 五层薄膜沉积

LP-CVD在低压、高温的反应环境中加热衬底上通过气相成分沉积形成薄膜,气相成分是由含薄膜成分的气体构成,低压有利于提高质量转移系数,实现均匀沉积;而高温(一般为400~900 ℃)能保持大容量反应室内良好的真空密封。严格控制气体混合物,反应器压强和衬底温度等工艺参数来得到均匀致密,压力平均的薄膜。

σt=σe+σi=-804+125×3+200×2=-29 MPa

(2)

表2 LP-CVD沉积薄膜工艺参数

按设计的前三层薄膜的结构,结合沉积速率,各层薄膜的沉积时间分别为9 min 氮化硅,26 min 氧化硅,18 min 氧化硅。干涉仪测得拟合厚度为26.5(2.0) nm SiNx,18.1(2.8) nm SiOx,51.0(1.6) nm SiO。硅片炉中取出在洁净室内放置过夜后进行后两层薄膜的沉积,沉积时间分别为400 min氧化硅,150 min氮化硅,其余参数不变。沉积完成后同样用干涉仪或者椭偏仪测得,结果符合实验设计。

在LP-CVD过程中,由于夹持装置,使得源气体无法到达硅片的边缘部分,这部分的薄膜厚度无法达到实验要求,因此,在芯片整体版图的设计时要避开这部分,也避免了释放过程中边缘部分破裂而造成整体硅片的毁坏,版图设计中,一个cell表示一个独立纳米孔传感器芯片,芯片尺寸为3.5 mm×3.5 mm,可通过释放预留切片槽来分解芯片。

2.2 释放窗口制备

为了得到测序实验所需要的悬空三明治结构悬空薄膜,需要对沉积了5层薄膜的硅片正反面都进行其余结构的释放工艺得到所设计的结构,所以,在释放工艺之前要先制备版图所设计的释放窗口。

2.2.1 Si释放窗口制备

涂覆膜厚1.7 μm均匀光刻胶(LCA00A,2 000 r/min),进行前烘处理(110 ℃,90 s)增加光刻胶与衬底间的粘附性,增强胶的光吸收及抗腐蚀能力。通过紫外曝光(45 s),掩模图案和圆片沿X,Y,Z轴对准,对准之后紫外光将对一定区域的光刻胶进行曝光,光刻胶发生光学反应,内部分子产生变化,改变光刻胶在显影液中的溶解度。在显影液中水浴3 min,溶解掉光刻胶的感光部分,留下了与掩模一致的图形,烘箱坚膜(135 ℃,30 min)后完成光刻步骤。打完底膜后,用RIE刻蚀掉光刻暴露出的背侧窗口内的全部沉积薄膜,露出Si表面,设计厚度为8 000×0.1 nm,时间为3 min。用膜厚仪在刻蚀过的硅片表面选择测试点,测得SiN膜的厚度均为0 mm,即薄膜已刻蚀干净。注意一定要过刻蚀,避免在后续的工序中无法完全释放Si基体,清洗,去胶后进行正面释放窗口的制造。

2.2.2 SiO2释放窗口的制备

使用不同的掩模版重复上述步骤正反对准,光刻工序步骤及工艺参数不变,RIE刻蚀时间为1min,刻蚀厚度2 000×0.1 nm,刻蚀掉正面最顶层窗口中的SiN,露出SiO表面,同样注意要过刻蚀,因为SiN在HF中的腐蚀速率远远不及SiO2,SiN的存在会影响后续SiO2的释放。RIE之后同样进行金属前去胶处理。

2.3 湿法腐蚀释放工艺

2.3.1 Si基体释放

(3)

设计所需得到60 μm×60 μm 的悬空三明治结构薄膜,Si基体总厚度为430 μm,因此设计释放窗口D的尺寸为670 μm×670 μm,要求过刻蚀,保证背面槽内露出Si3N4表面。因为KOH会对正面暴露的SiO2产生刻蚀,因此要对硅片正面涂胶保护,随后将硅片置于50 ℃水浴温度的KOH溶液中,通过产生气泡来判断基体Si的腐蚀情况,28 h后检查硅片,测得腐蚀腔深度为319 μm,计算得腐蚀速率为11.2 μm/h。继续腐蚀,45 h后检查硅片的释放窗口透光,代表Si基体完全释放。清洗、去胶后进行正面加工。

2.3.2 SiO2释放

在稀释的HF溶液,进行SiO2湿法同向腐蚀。SiO2在HF腐蚀剂中为各向同性腐蚀,但对于Si3N4和SiO22种硅化物却有高度的选择比,SiO2的腐蚀速率远远高于Si3N4,在腐蚀液中发生的反应为:SiO2+6HF→H2SiF6+2H2O。其为络合反应,H2SiF6为可溶物,通过搅拌可离开硅片。在HF缓冲液中还配比一定的氟化铵(NH4F)作为缓冲液,以电离出H+补充随着反应推进而逐渐减少的H+,保证HF的腐蚀速率。将清洗后的硅片置于HF溶液中,缓慢晃动样品架,使硅片与HF溶液充分接触,3 min之后取出芯片用去离子水清洗,腐蚀速率约为2 nm/s。释放后得到三明治薄膜如图3所示,得到两面悬空,直径为9 μm的薄膜且薄膜完整,没有出现破裂、挤压等现象。

图3 三明治结构薄膜

3 双层Si3N4纳米孔制造

悬空三明治结构薄膜的总厚度理论设计为80 nm,用蔡司氦离子束显微镜(ORION NanoFab)测得悬空薄膜的厚度为100 nm左右,在预计的误差范围内,如图4(a)所示。由于透射电子显微镜(transmission electron microscopy,TEM)的电子束穿透力较弱,无法在此厚度的薄膜上直接制得直径小于10 nm的纳米孔,因此使用氦离子束(ORION NanoFab)轰击,在STEM模式下,施加电压为5 kV,曝光时间为6 s,得到直径小于5 nm的纳米孔,在TEM(JEM—2100F)下得到纳米孔照片如图4(b)。

图4 三明治结构悬空薄膜厚度和纳米孔的TEM照片

4 结束语

本文基于动力学校对的原理设计的三明治结构双氮化硅纳米孔芯片,在三明治结构层的基础上增加了双牺牲层提高测序信噪比,并通过应力的计算设计了各层薄膜的厚度,以期得到低应力的均匀薄膜。结合纳机电系统(nano-electro-mechanical system,NEMS)技术设计了此芯片的工艺流程,成功制造出了悬空三明治结构薄膜,利用聚焦离子束(focused ion beam,FIB),HF腐蚀制造了双纳米孔结构,理论上解决的固态纳米孔测序中的DNA分子扩散的问题。此外,此工艺简单,成本低廉,可以实现大批量生产,为未来进一步降低测序成本提供了保障。