定时同步信号产生电路的设计与实现

2018-06-13郭江宇李勇峰

王 斐,郭江宇,李勇峰,刘 健

(北方自动控制技术研究所,太原 030006)

0 引言

定时器是接收机系统的重要组成部分,它能够提供所需的各种主脉冲定时信号和波门定时信号。在最初的设计中,定时器大多采用纯硬件的实现方法,用分立元件搭建逻辑电路,电路复杂,工作量大,可读性差,可靠性低,根据特定的需求设计特定的电路,基本不具备通用性。近年来,以数字技术为基础的定时器得到了飞速的发展,性能指标达到了一个新的水平。现场可编程门阵列(FPGA)器件具有容量大、运算速度快、灵活可变等优点,使得许多复杂电路有了新的实现途径,越来越被广泛地应用于实际系统中[1]。因此,需要通过FPGA设计一种可以实现大量定时单元的定时芯片。

目前,对于定时电路的研究主要集中在可重构方面,所建立的电路较为复杂,难以工程实践。吴文博[2]的硕士论文中着重强调了定时电路的重要性,同时研究了现场可编程门阵列(FPGA)在雷达定时器中的应用,并且运用基于部分可重构方法的原理及设计思想,基于已有的逻辑层面之上,把设计程序进行进一步简化,使雷达定时器可实现局部动态再次构建。邹仕祥[3]对于定时电路在通信网络中的应用进行了广泛的研究,提出了其在通信领域的应用前景以及设计实现方法,但文中并未对实现的电路进行简化,导致工程实现方面缺少理论依据。彭兵[4]等对基于计数器的可编程定时电路进行了详细研究,分析了实践过程中的诸多问题,但未对相关难题进行解决。传统的定时器大多采用纯硬件的实现方法,根据特定的需求设计特定的电路,不具备通用性。而基于FPGA的定时器设计简单,集成度高,满足了接收机系统的工作要求,提高了定时器的工作效率和速度。

本文在分析定时器和电源功能的基础上,完成了定时同步信号产生电路的硬件平台搭建及调试,并编写了FPGA及其他模块的软件程序,实现了该电路的全部功能。

1 设计方案

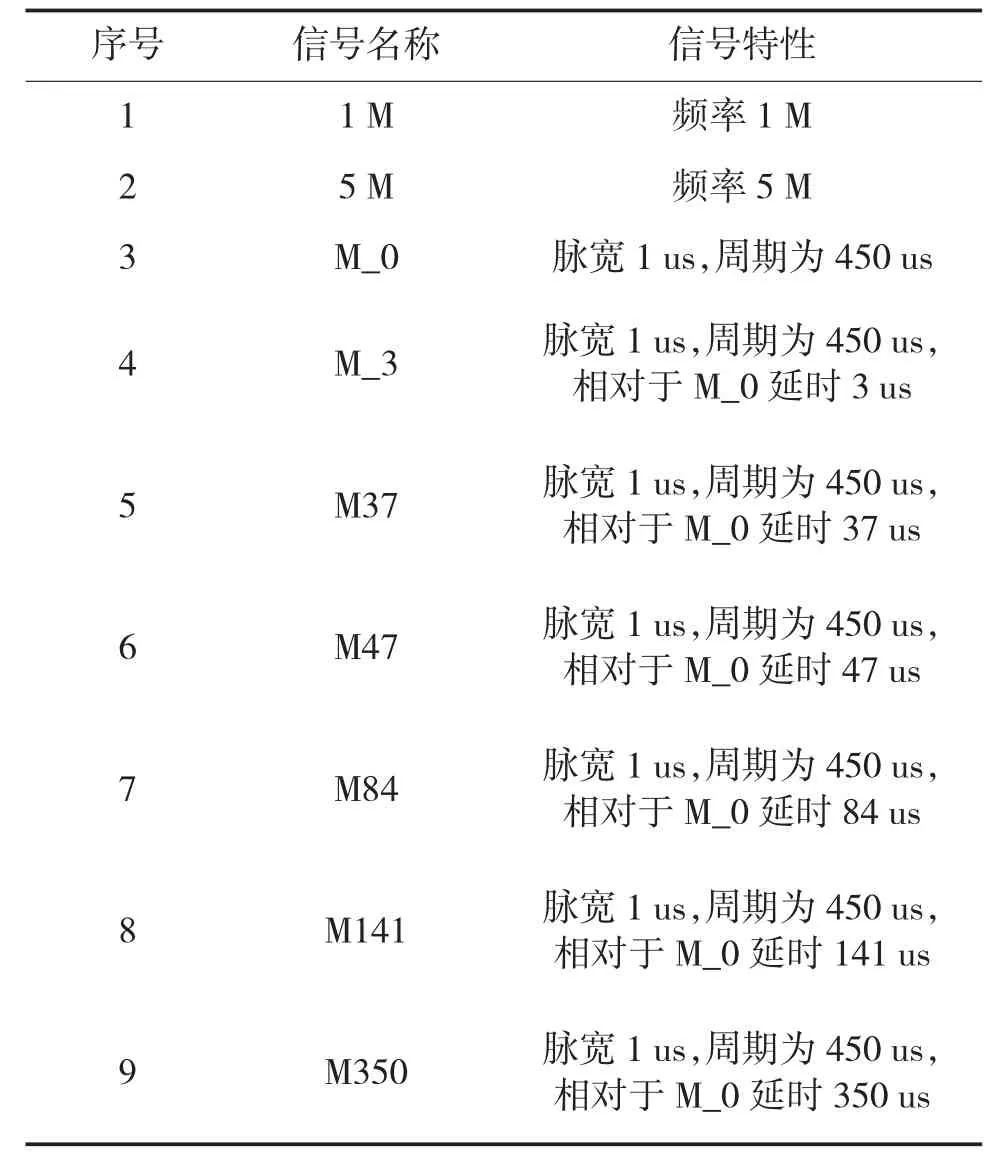

根据接收机运行环境,设计一种基于FPGA的定时器来满足要求。定时信号板为接收机系统提供必要的定时信号输入和频率控制信号,以实现接收机的正常工作激励。采用FPGA完成定时信号的生成,其中定时信号以外部晶振作为基准产生,基准信号是一个30 M时钟信号,经过分频产生5 M和1 M的时钟信号。再产生一个脉宽为1 us,周期为450 us的信号,在此基础上对信号进行超前和滞后3 us、滞后 37 us、滞后 47 us、滞后 84 us、滞后 141 us、滞后350 us等一系列的编程,最后再将程序安装在定时信号板上,输入一个30 M的时钟信号以便于检查输出的信号是否满足要求。在此过程中通过定时器对30 MHz时钟信号进行分频和延时等操作产生需要的各种信号如表1所示。

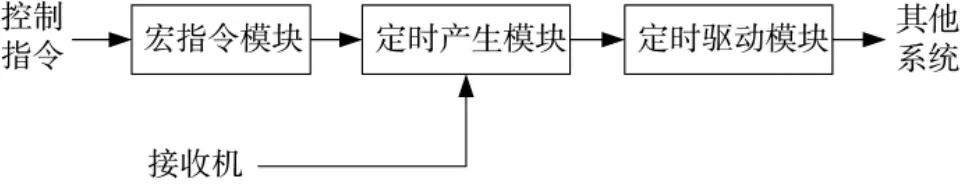

定时同步信号产生电路包括宏指令模块、定时产生模块、定时驱动模块等部分。宏指令模块通过网络或快速通信接口接收指令,并送往定时产生模块。定时产生模块采用FPGA构成核心的时序产生电路,可方便地对定时时序进行修改调试,产生各路定时信号,送往定时驱动模块,该模块根据各分系统的要求,将各路定时信号以不同的信号形式(如TTL、RS-422等)送往各分系统,这部分电路将留有冗余通道备用,并具有对送往不同分系统的信号延时进行补偿的功能,原理框图如图1所示。

图1 定时同步信号产生电路原理

经过分频和延时输出的各种信号会送到芯片上进行检验,最后输出频率或者输出定时信号。用定时信号控制继电口的开关,从而输出符合要求的信号。

表1 所需信号表

2 硬件设计

2.1 电路整体设计原理

定时信号以硬件外部晶振作为基准产生,其中基准信号是一个30 M时钟信号。硬件采用Altera公司EP1K系列的FPGA为数字平台,利用模块化设计和Verilog语言在FPGA中设计进行分频和延时,将30 M时钟信号,经过分频产生1 M和5 M的时钟信号。再产生一个脉宽为1 us,周期为450 us的信号,在此基础上对信号进行超前和滞后3 us、滞后37us、滞后 47us、滞后 84us、滞后 141 us、滞后 350 us等一系列的编程。

经过分频和延时产生的各种信号输入到芯片中,在芯片中进行一系列的处理,检验输入的信号是否符合要求,如果符合要求则输出信号以供使用,其原理如下页图2所示。

2.2 定时器模块设计

定时器模块设计采用大容量FPGA,尽可能在FPGA内部实现所有功能,减少外围器件,以达到统一板级设计、提高定时精度及可靠性、降低成本、实现硬件的灵活配置的目的。

定时器的时序电路设计主要分为主脉冲定时信号的时序电路设计和波门定时信号的时序电路设计两大部分[5]。产生主脉冲定时信号的时序电路,利用接收机的时钟,产生重频的方波、发射主脉冲、移相主脉冲等各种主脉冲导前或滞后信号。产生波门定时信号的时序电路则是根据距离码产生正常波门、移相波门、波门导前或滞后信号。移相主脉冲定时信号和移相波门定时信号只要分别将产生的正常主脉冲定时信号和正常波门定时信号移相半个周期即可得到。

FPGA具有可重复编程性,可以通过硬件电路的方式实现定时器功能,同时FPGA可以方便地进行调试和仿真[6]。在此设计中选用的FPGA型号是Altera公司的EP1K50TC144,该芯片功能强大,满足本设计的需求。

图2 硬件设计原理

2.3 分频模块设计

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂集成的锁相环资源。但是在对于时钟要求不高的设计中,自行设计所需的分频器能够达到更好的应用效果。

首先,这种方法可以节省芯片内部的锁相环资源;再者,可以控制FPGA中逻辑单元的使用情况。在具体的设计中,由于外部时钟的关系,常常需要对时钟进行分频,因此,根据实际情况会需要进行偶数分频、奇数分频、半整数分频和小数分频等不同形式的时钟分频,有时要求等占空比,有时要求非等占空比[7]。

2.4 延时模块设计

本文是利用FPGA中计数器模块来实现周期的延时功能,采用对一个已知频率的基准方波信号进行计数的方法实现时间的延时[8]。利用FPGA技术首先是从整体系统设计入手,经详细地规划后,完成控制系统行为方面的设计,并使用完全独立于具体物理结构的用户接口来表达功能模块。

在确定了实现产生延时时间的方法以后,实际上,整个电路的延时过程就计数器的计数过程,也就是说,当计数器计数结束后其延时时间过程也随之结束。显然,当触发信号到来时,计数器开始工作,当一个计数延时过程结束以后,为不影响下一个延时过程的开始,要求在前一个计数过程结束时,必须做好下一步的延时准备工作。

2.5 频率控制模块设计

经过分频和延时产生的各种信号输入到芯片中,在芯片中进行一系列的处理,检验输入的信号是否符合要求,如果符合要求则输出信号以供使用。

本文采用STM32F417。具体参数如下[9]:内核:ARM 32位的Cortex-M3 CPU,最高72 MHz工作频率,在存储器的等待周期访问时可达1.25DMips/MHz,单周期乘法和硬件除法。存储器:从64 K或128 K字节的闪存程序存储器,高达20 K字节的SRAM。时钟、复位和电源管理:2.0 V~3.6 V供电和I/O引脚,上电/断电复位、可编程电压检测器,4 MHz~16 MHz晶体振荡器,内嵌经出厂调校的8 MHz的RC振荡器,内嵌带校准的40 kHz的RC振荡器,产生CPU时钟的PLL。低功耗:睡眠、停机和待机模式。调试模式:串行单线调试和JTAG接口。多达7个定时器:3个16位定时器,每个定时器有多达4个用于输入捕获/输出比较/PWM或脉冲计数的通道和增量编码器输入,1个16位带死区控制和紧急刹车,用于电机控制的PWM的高级控制定时器,2个看门狗定时器,系统时间定时器:24位自减型计数器。CRC计算单元,96位的芯片唯一代码。

2.6 电路及接口设计

在串行通讯时,要求通讯都采用一个标准接口,使不同的设备可以方便地连接起来进行通讯。RS-232是目前最常用的一种串行通讯接口。RS-232总线标准设有25条信号线,包括一个主通道和一个辅助通道。在本设计中,利用RS-232实现芯片接收上位机控制单元信号。

在与上位机进行通信时,相对于RS-232,网络通信模块通信容量更大,通信速度更快,同时也利用网络通信模块与上位机进行通信[10]。

3 软件编程

3.1 分频模块编程

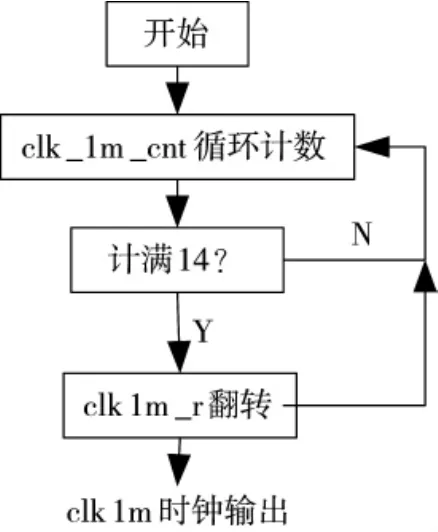

输入的信号是一个30 MHz的时钟信号,需要输出一个1 MHz和一个5 MHz的时钟信号,要产生两种信号就需要通过分频来实现,其流程图如下页图3和图4所示。

图3 5M时钟产生流程

图4 1M时钟产生流程

图3为5 MHz计数器的循环计数,当计数未满2时,继续循环计数,当计数满2时,时钟翻转。图4为1 MHz计数器的循环计数,当计数未满14时,继续循环计数,当计数满14时,时钟翻转。

3.2 延时模块编程

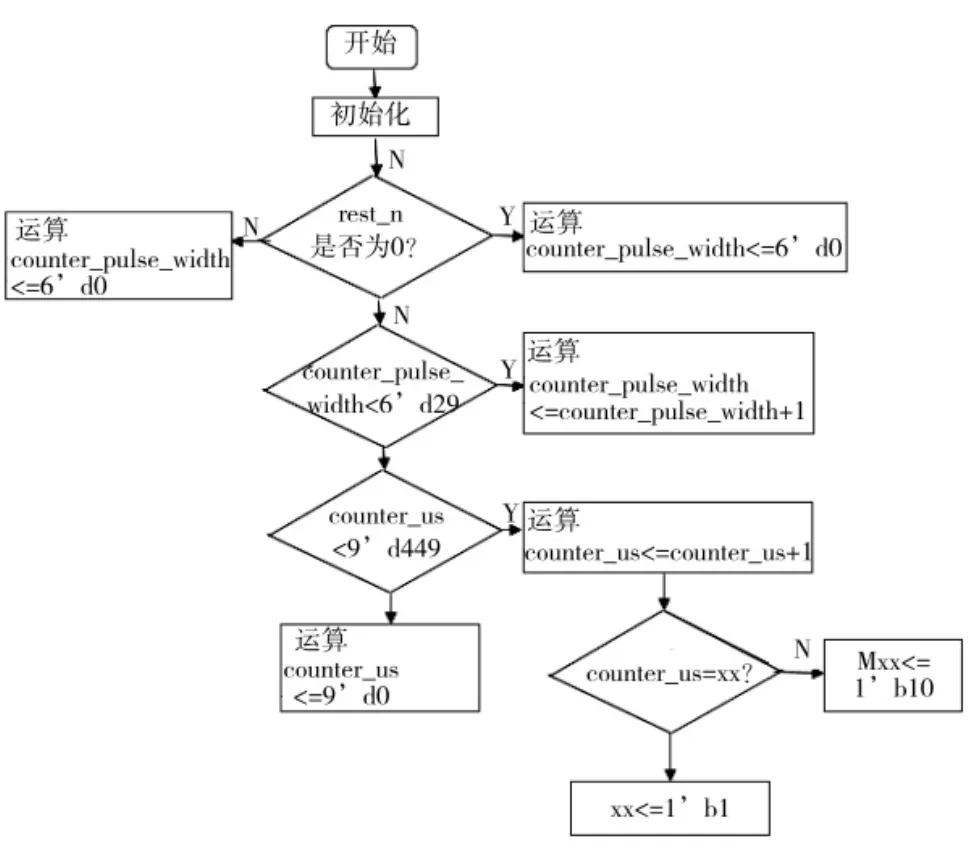

在30 MHz时钟信号下生成基准信号,需要计数30次才能达到1 us的宽度。在生成脉宽为1 us、周期为450 us的基准信号后,需要对这个基准信号进行延时处理,以生成所需要的其他信号。其中M_0是生成的基准信号,M_3是基准信号延时3 us,M37是在基准信号上延时37 us,M47是在基准信号上延时47 us,M84是在基准信号上延时84 us,M141是在基准信号上延时141 us,M350是在基准信号上延时350 us,如图5所示。

初始化后,低电平复位,没有复位进行计数,对信号进行分频,先得到1 us的时钟信号,再进行计数一个周期450 us,然后进行延时处理,其中XX是延迟时间,如果延时3 us,则XX=3。

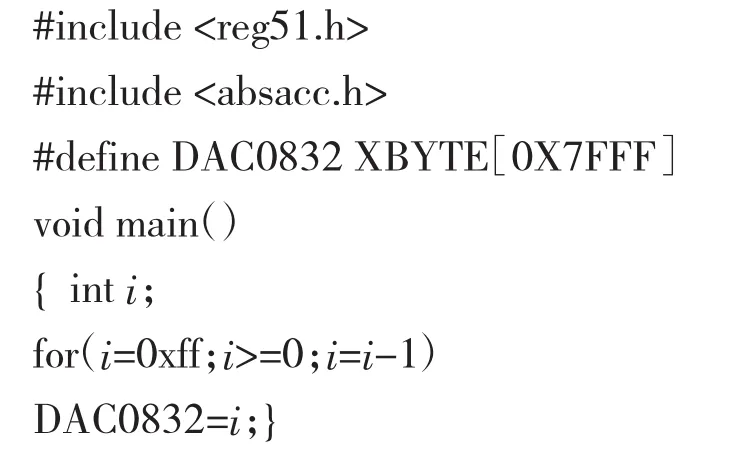

3.3 波形的实现

模拟定时器的的两路触发脉冲需要DAC0832芯片转化后经过放大器的放大倒相后才能实现。若让DAC0832芯片输出电压是脉冲电压,需让单片机从P0.0~P0.7引脚端输出不断增大或减小的数据即可。因此,可以采用由“ABSACC.H”头文件所定义的指令“XBYTE[unsigned int]”来实现对 DAC0832 的寻址。

图5 延时信号产生流程

xval=XBYTE[0X000F];//将地址“0x000F”中的数据取出送给xval。

XBYTE[0X000F]=0xA8;//将数据“0xA8”送入地址“0x000F”。

为得到有一定时间间隔的脉冲信号,可在让单片机从P0.0~P0.7引脚端输出不断增大或减小的数据之前或之后设置一段时间延迟。用C语言编写的输出波形主要程序为:

偏流脉冲信号由单片机本身产生,在编程过程中,只需在输入/输出口的电平设置为0或1(高电平电压的地址为0xff,低电平地址为0xfe,然后在经过放大器放大后通过示波器显示出来。

3.4 模拟定时器脉冲宽度的实现

模拟定时器的脉冲宽度也是通过编程实现的。信号所需的脉冲宽度在25 us和4 us~6 us左右,要求在模拟的过程中通过编程将延迟控制在这段范围左右。

CLR A;//将A 清 0。

C;0011 MOV R7,A;//将 0送给工作寄存 R7。

INC R7;//将 R7 加 1。

CJNE R7,ox64;

若 R7 不等于 ox64(6*16+4=100);则;转到 C:0011处执行。

根据循环条件,第03行和04行总共要执行100次(ox64=100)。所以,上述程序共消耗机器周期数:N=1+1+(1+2)*100=302。

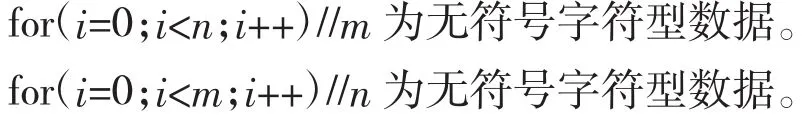

根据以上分析可知,一重循环:for(i=0;i<n;i++),所消耗的机器周期数N=3*n+2。其中N为消耗的机器周期数;n为设定的循环次数(n必须为无符号字符型数据)。在n远大于2时,可近似为N=3*n。同理可得,二重循环程序:

所消耗的机器周期数N=3*m*n+5*m+2。在n远大于5时,可近似N=3*m*n。

仿真过程中没有使用编程而是采用C语言。单片机的晶振频率为12 MHz,机器周期为1 μs。根据分析,仿真所需的延时应设置n=5左右,才能达到预期效果。非脉冲的延迟时间可适当加长。由于程序和仿真软件的精度的原因,所实现的脉冲宽度与实际的精度还有一定差距。

最终用C语言编写的延迟函数为:

其中,n的值决定脉冲宽度的大小。

3.5 模拟定时器脉冲幅度的实现

信号产生系统中对脉冲的幅度有很高的要求,利用编程可控制脉冲幅度在最大和最小的范围之内变化。单片机的引脚从P0.0~P0.7端输出不断减小的数据,其中由最大值决定幅度的大小。设计过程当中,编程设置为最大值,即当数据开始输出时就以5 V电压为基准,有次序地下降。

为了达到设计所要求的-22 V的触发脉冲信号,单纯靠单片机编程很难实现,因此,在单片机外围连接了运算放大电路,通过硬件设计来实现。运算放大器分为两级放大,两级的放大倍数分别为2倍~3倍。经过运算放大器放大后,基本就得到了设计所需要的电压幅度。

4 结论

本文针对接收机系统的定时同步信号产生电路进行了设计,完成了对接收机系统运行环境的构建,主要工作可以概括为:1)确定系统的定时同步信号,同时分析各信号的作用,为接下来的电路设计和程序的编写提供了依据;2)以ALTERA公司的FPGA为核心进行定时器的硬件设计,对关键模块的设计进行详细分析;3)在QuartusⅡ环境下采用Verilog语言进行软件编程,实现所需信号的产生。实验表明,本设计能够产生相应信号,满足设计要求,具有一定的实际应用价值。

[1]李辰.光电技术对提高高炮系统作战能力的研究[D].长沙:国防科技大学,2006.

[2]吴文博.基于FPGA动态局部可重构技术的雷达定时器设计[D].成都:电子科技大学,2016.

[3]邹仕祥.通信系统中大量定时器的设计与分析[J].计算机应用,2015,25(11):2715-2716.

[4]彭兵,韩克,敏韩勇.基于计数器的可编程定时电路[J].西北农林科技大学学报,2003,31(5):199-201.

[5]张岩,伍春,赵志坤.基于FPGA的多通道数据采集卡的方案设计[J].东北师大学报(自然科学版),2016,48(4):63-67.

[6]辛君君,黄松岭,刘立力,等.基于FPGA的超多通道高速数据采集系统设计 [J].电测与仪表,2008,45(10):34-36.

[7]肖祖胜,程明.基于FPGA的数据采集分析系统设计[J].电子技术应用,2009,35(3):49-50.

[8]周润景,图雅,张丽敏.基于Quartus II的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社,2007.

[9]王龙,杨承志,吴宏超,等.基于FPGA的数字基带多模雷达信号源设计[J].电子技术应用,2016,42(8):87-90.

[10]李红刚,杨林楠,张丽莲,等.基于FPGA的高速多通道数据采集系统的设计[J].计算机测量与控制,2016,14(10):1407-1409.