基于FPGA的图像翻转技术

2018-03-30吴琼

吴琼

摘要

近年来,随着大规模集成电路的发展,可编程逻辑阵列FPGA在当前嵌入式系统中得到广泛应用,同时,可编程逻辑阵列对数据并行处理,在片上操作系统和图像处理方面有很大优势,鉴于此,本文论述基于FPGA的图像翻转技术。本论文论述了在液晶显示器设计研发过程中用FPGA结合SRAM实现图像翻转的功能,考虑到实现成本及图像分辨率的多样性,我们使用RAM组对图像翻转进行设计实现,实现过程中考虑RAM的选取、硬件原理设计及FPGA对多RAM的控制等,图像翻转后画面显示清晰无干扰,且该技术可用于任意分辨率图像的翻转。

【关键词】FPGA 图像翻转 SRAM

多功能液晶显示器设计研发过程中对液晶显示模块的选择会受限于货架模块己有的结构设计,除此之外,正常情况下,液晶显示模块的起始点(0,0)位于模块左上角,在选择液晶显示模块时难免会遇到光学指标符合要求但结构安装翻转180°的情况,亦或是液晶显示模块的起始点(0,0)位于模块右下角的情况,如此,我们在图像显示处理过程中需对其翻转180°,通过FPGA操作SRAM对像素的存取,使其在画面显示时正立不变形,符合人眼正常视角观察习惯。而视频翻转由FPGA结合SRAM实现。

1 RAM选取

一般RAM的选取需考虑两方面的因素——存储容量和操作响应速度。

由于成本因素和国外禁运等因素,目前市场上使用较多的SRAM为Cypress公司产品,己CY7C1061为例,该SRAM为1M(地址空间)×l6位的静态RAM,也就是说每片RAM可存放1024×1024个16位数据。

图像翻转的前提是需将一帧完整的图像存放于存储器中并通过算法将像素逆序取出并显示,因此先考虑像素完整存放的问题。

现常用的较为简单的图像分辨率为1024×768@60Hz,若颜色位数R:G:B=6:6:6时,我们可权衡舍掉红色和蓝色最低位变为R:G:B=5:6:5,这样一个像素的颜色可由16位数据表示,存放于SRAM的一个地址中。一帧画面中有效的1024×768个像素数据可存放于1024×768个地址当中,其中行地址由十位地址位组成,分别指示0?1023行,我们需要用到的仅0?767行,列地址也由十位地址位组成,分别指示0?1023列。因此,该RAM一片可实现1024×768像素R:G:B=5:6:5图像存储需求。

若每色灰度级要求为256级,即R:G:B=8:8:8时,每个像素的24位数据需存放于两片RAM的同一地址中。这样需要在原有基础上对RAM进行扩展,变为1M×32位容量,将24位数据完整存放,保证图像不失真。

而在操作速度方面,要将每一个像素数据进行存取,RAM的响应速度不得低于图像像素时钟频率,即点频。根据VISA标准,对于1024×768@60Hz的图像显示而言,像素点频约为65MHz,因此FPGA对像素数据的存取速度以及RAM的响应速度均需大于65MHz。一般情况下,目前常用的FPGA的操作速度均在400MHz以上,完全可以满足要求,而SRAM的响应速度需小于1/(65×106),约15ns。

2 硬件设计

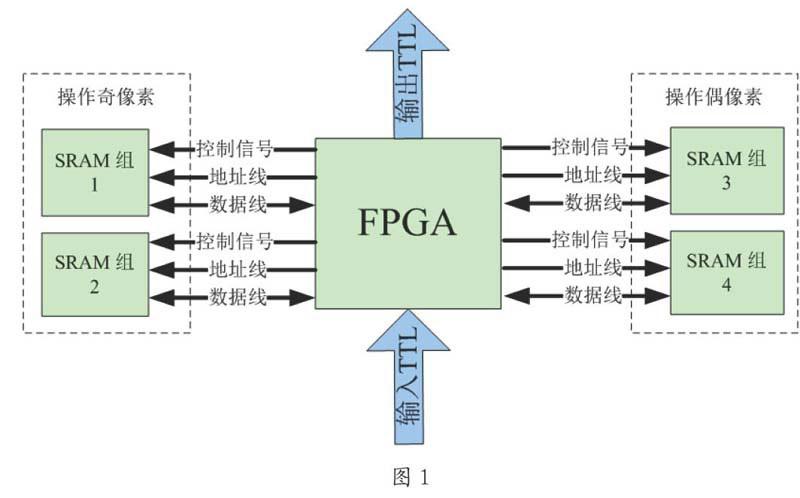

以1600×1200@60Hz,R:G:B=5:6:5图像为例,以双像素模式进行显示,奇偶场有效像素分别为800×1200,在视频翻转硬件设计时,存放一场奇像素或偶像素需要两片RAM,800×1024像素的16位颜色用一片,超出1024行像素的16位颜色需另外一片RAM予以存放,这样便于FPGA的操作。为保证图像刷新率不变,图像显示流畅,FPGA对SRAM采用“乒乓”操作,即场同步信号(VS)分频,将图像按帧轮流存放于两组RAM中,向一组写入时从另一组读取显示,原理图如图1,这样显示的图像与源相比仅推迟一帧的速度,即16ms。

为避免FPGA对RAM的操作冲突,FPGA对各组RAM的地址线、数据线以及控制线不进行复用,数据线为图像颜色数据,地址线为RAM的A0?A19共20位地址,控制线包括该RAM的使能信号/CE1、CE2,读写控制信号/OE、/WE,以及高八位数据和低八位数据的使能控制线/BHE、/BLE。由于RAM—直被FPGA进行读写操作,其中数据的使能控制线可在原理设计时直接接低,其余控制线可接至FPGA的IO引脚。

3 FPGA的程序实现

首先对场信号(VS)计数分频,当分频信号为高时,对一组RAM进行数据存放从另一组RAM组进行数据读取,存放数据的地址由行频计数和点频时钟计数组成,在图像使能(DE)有效时开始计数,行频计数和点频计数器分别定义为11位逻辑矢量和10位逻辑矢量,满足每行800个像素和1200行的数据要求,当行计数超过1024时,地址计数自动溢出,此时可开启下一片RAM的片選,将超出1024地址的部分存入同组第二片RAM当中。由此可将一帧的图像完整的存储在RAM组当中。因此行计数的最高位可控制一组RAM组中两片RAM的使能信号/CE1、CE2。

从另一组RAM中取出数据显示时,地址寻址与存储时相反,用每行像素总数800减去当前点频计数为需要操作的列地址,用总行数1200减去当前行频计数为需要操作的行地址,由这两个地址组合而成的20位地址逻辑矢量为当前要操作的RAM地址。用上述方式可将图像信号翻转180°,满足使用要求。

参考文献

[1]李洪革.FPGA/ASIC高性能数字系统设计[M].北京:电子工业出版社,2011:1.