基于有限状态机的PLC程序设计方法

2018-03-01范雄涛和淑芬

范雄涛 沈 勇 和淑芬

(云南民族大学电气信息工程学院,昆明 650500)

可编程序控制器(programmable logic controller,PLC)本质是一个微型计算机,在现代化工厂中大量采用PLC完成控制系统的逻辑控制[1]。根据是否与原来的状态有关,可将其分为组合逻辑电路和时序逻辑电路,时序逻辑电路的输出取决于当前的输入和原来的状态[2]。根据存储电路的状态变化时刻,可将时序电路分为同步时序电路和异步时序电路。同步时序电路的所有触发器的状态变化都在同一脉冲作用下发生[3]。

1 有限状态机

时序电路是状态依赖的,故称为状态机[4]。因输入和输出都是有限的,故称为有限状态机。有限状态机理论已经形成了一整套完整的体系,根据输出信号是否与输入信号有关,可将状态机分为Moore状态机和Mealy状态机[5]。

可将状态机归纳为4个因素:现态、次态、动作、条件[6]。其中,次态是指条件满足后执行动作要迁移的新状态。“次态”是相对于“现态”而言的,“次态”一旦被激活,就转变成新的“现态”。

作进一步归纳总结,“现态”、“次态”可以统一起来为“状态”,“条件”、“动作”可以统一起来为“迁移条件”,并可以用函数的表示方法更加直观地认识其中的关系。

状态:{现态×迁移条件→次态}状态机采用的表示方法有许多种,在此采用的是表格和图形的表示方法[7]。

2 同步时序电路

对异步时序电路进行分析,就必须考虑每个状态时刻触发器与时钟信号的关系[8],对于复杂性输入的电路来说,其设计的工作量较大,并且各存储单元的状态转换因受到时钟信号触发而存在时间差异从而可能造成输出状态短时间的不稳定,而这种不稳定有时可能是无法预计的,从而电路设计的复杂性以及调试的工作量。

时钟同步状态机所有触发器的状态更新是在同一时刻[9],其输出状态变化的时间不存在差异或者差异绩效,在时钟脉冲两次作用的间隔期间,从触发器输入到状态输出的通路被切断,也不会改变触发器的输出状态,所以很少发生输出不稳定的现象[10]。更重要的是,其电路的状态很容易用固定周期的时钟脉冲边沿清楚地分离为序列步进,每一个步进都已通过输入信号和所有触发器的现态单独进行分析,从而形成一套较系统、易掌握的分析和设计方法。

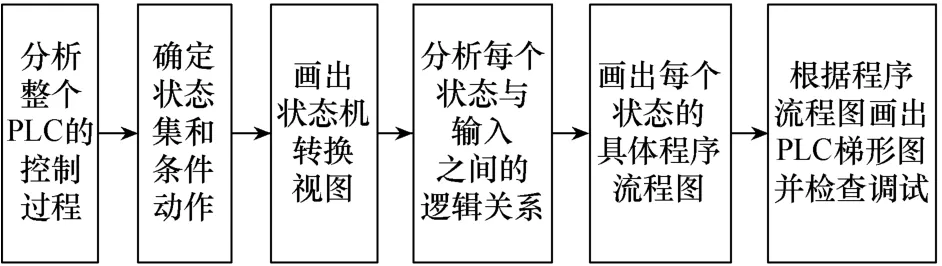

在启动PLC的CPU后,系统将循环执行主程序OB1,并可在执行过程中调用其他逻辑功能块,如FC、FB、DB、SFB和SFC等[9],将有限状态机理论应用于PLC程序设计。关键在于分析整个系统的状态集和迁移条件、现态迁移到次态的具体逻辑、迁移条件与系统的输入之间的关系。状态集包含了PLC系统的起始状态、现态与次态,输入对应于PLC系统的状态转换函数的动作过程,输出对应于整个PLC系统的状态与动作的响应。复杂型输入状态的PLC程序设计的基本思路如图1所示。

程序状态流程图是程序分析中最实用的分析技术,它是进行程序流程分析过程中最基本的工具。利用程序流程图与状态机视图的相结合。可以有效地描述PLC系统中状态、输入、状态转换之间的相互关系。

3 基于有限状态机的PLC程序设计的应用

本文以一个无浮点四则运算的计算器PLC程序设计为例,分析有限状态机理论在复杂PLC程序设计的应用。本计算器包括数字键0—9,操作码 + − */、=、清零键C在内的16个输入按键。计算器程序的复杂性在于:①输入操作数的程序设计;②计算时输入按键顺序的随机性强,并且输入的历史有关。而利用有限状态机理论分析该计算器程序的难点是如何合理划分整个系统的所有状态和输入属性,从而减少工作量。

对于输入操作数的程序,可做一个 FC的函数块,命名为DATA_IN,其输入操作数程序的核心是buff=buff*10+KeyData,其中buff代表按键缓冲区,KeyData为数字键。因输出与输入的历史有关,故只采用组合逻辑电路的设计方法不能解决记忆的问题,同样因异步时序逻辑电路设计的复杂性和不稳定难调试等缺点会给本程序设计增加困难,故采用同步时序逻辑电路的设计方法指导该计算器的程序设计。PLC主程序OB1扫描是自上而下、自左而右循环扫描执行的,故要使得系统的状态在一个扫描周期只改变一次,应在主程序OB1不应设计成一个触点驱动两个状态的情况,避免程序在一个扫描的过程中因一个触点驱动状态寄存器改变引起后面的程序运行的混乱,从而减少程序设计的复杂性[11]。

本文利用有限状态机理论分析整个计算过程的所有状态集和动作输入,能够全面地枚举所有的计算过程。显然,无浮点四则运算的计算过程通常为a?b=c,其中a表示第一操作数OP1,?表示操作OP,b表示第二操作数OP2,c表示a、b进行运算的结果,为了能再进行下一步的运算,可将计算结果放在OP1中。即可得到3个输入过程:输入第一操作数OP1、输入操作OP、输入第二操作数OP2。在进行运算时,根据输入的可能性会出现以下情况:上电初始化,输入第一个操作数并且能继续输入第一个操作数,接着输入操作,再输入第二个操作数,按下等号键,计算结果放在第一操作数中,接着等待操作码进行下一次运算,其中如果输入的操作数或计算结果有可能因溢出而导致出错或者按下清零键直接恢复初始化。根据以上分析并区分因输入的情况而使状态转换可得到以下6种状态。

Stat0:初始即上电程序初始化;

Stat1:输入第一操作数,并且还能继续输入第一操作数,如输入第一操作数“12”,并且接着按下“3”、“4”使得第一操作数为“1234”;

Stat2:有第一操作数和操作,如第一操作数“1234”和操作“+”;

Stat3:有第二操作数,如第二操作数“567”;

Stat4:有第一操作数,等待操作码,即前面计算的结果“1801”放在第一操作数OP1中,等待下一次计算;

Stat5:出错,如计算溢出导致出错等。

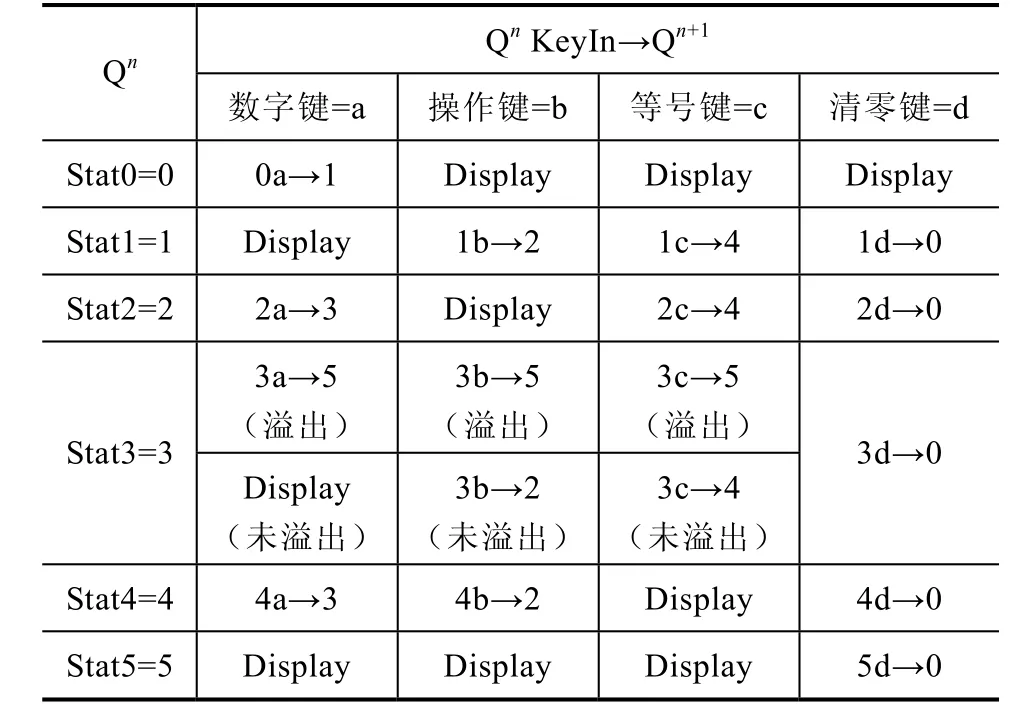

由此得出6个状态×16个输入按键=96种组合逻辑的情况,但因输入按键的特性可以分为4种按键属性,为了方便表示,可将PLC的I点对应赋值为 0—9数字键,10—13分别为+、−、*、/的操作键,14为=、15为清零键,一共4种按键属性。因此,可以化简6个状态×4种按键属性=24种组合逻辑。如表1所示Qn表示现态,Qn+1表示次态,KeyIn表示输入键,Display表示结果显示。

表1 组合逻辑表

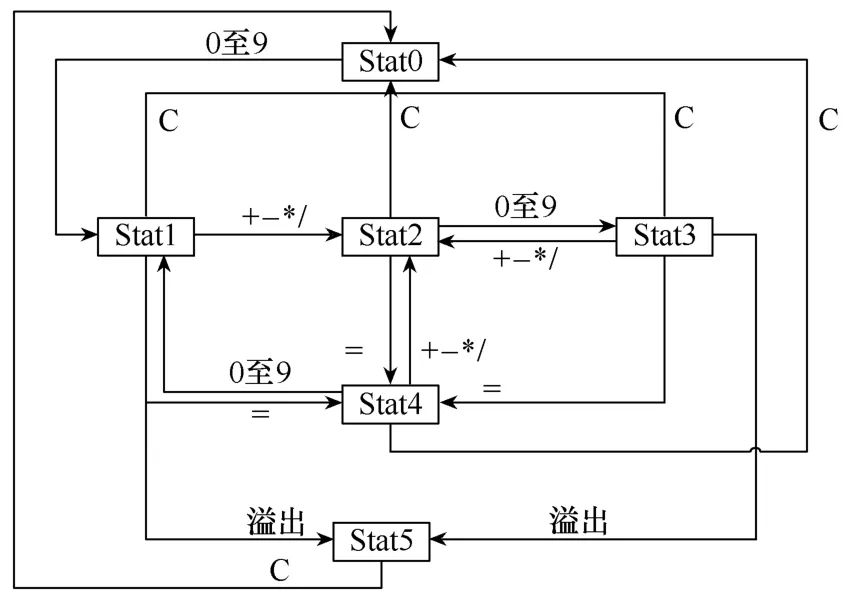

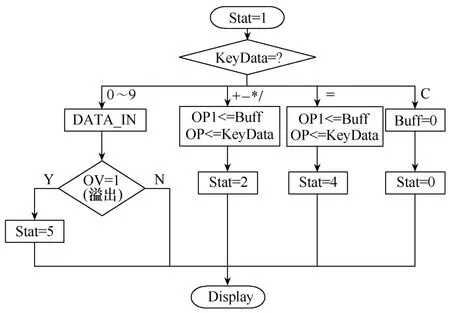

例如,上电初始化后→Stat0→数字键→Stat1→操作键→Stat2→数字键→Stat3→等号键→Stat4→计算溢出→Stat5;Stat1、Stat3→输入溢出→Stat5;Stat1、Stat2、Stat3、Stat4、Stat5→清零键 C→Stat0等,其中在输入操作数的过程中调用DATA_IN。完整的状态转换机如图2所示。

图2 完整的状态转换机

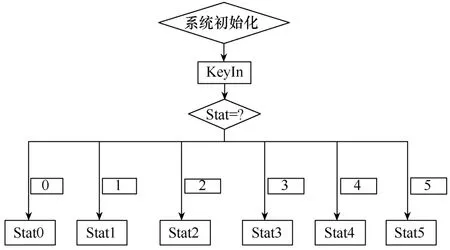

如图3所示,初始化后根据按键KeyIn判断整个系统的状态 Stat;根据状态转换视图来分析每个状态转换的具体流程图,如图4所示的Stat1的具体流程图;再根据具体流程图依次写出PLC梯形图,最后进行检查仿真验证,限于篇幅在此就不详细列出每个状态转换的具体程序。其优化方法在如下方面。

1)多级顺序条件控制策略

即将被控对象的控制按照条件分成多级控制,每一级之间都定义有对应的接口。如图4所示的Stat1的具体流程图,根据KeyData的值满足对应的转移条件时,继续进行下一步的动作。当出现故障时,可以在相应的控制级别查询,从而为系统的开发和调试带来了极大的方便。

图3 主程序框图

图4 Stat1的流程图

2)状态机逻辑控制方案

赋予每个状态一个状态字如0、1、2等,该状态字标志着当前系统处于何种状态。另外,对每个状态分配专用的状态查询单元,当检测到根据用户需要或系统运行情况需要改变状态时,便对状态位进行操作,修改对应的状态位,从而通过软件实现状态机的切换。

4 西门子S7-GRAPH编程语言结构

在西门子顺序功能图的S7-GRAPH的编程语言结构中,有步、转换条件、选择分支、并行分支等结构元素。根据功能将控制任务分解为若干步,其顺序用图形方式显示出来并且可形成图形和文本方式的文件[12]。其核心是根据系统逻辑结构分析每一步和步与步之间的转换条件,其中会根据实际转换条件相应嵌套选择分支和并行分支等。

这与有限状态机理论有异趣同工之效,其核心也是分析状态集和现态与次态之间的迁移条件,其中也会根据其实际逻辑结构和状态迁移条件存在多种状态与并行。

这种基于有限状态机程序设计的方法与常规的顺序控制设计、逻辑控制设计等有一定的关联性与相似性,但是采用有限状态机理论的方法使得分析程序的思路更加清晰,设计逻辑更加全面而又严格。分析清楚每个状态与每个输入之间逻辑关系后,根据所画的程序流程图,能因避免其他状态输入的干扰而更加快速而完整地编写梯形图程序。

5 结论

本文以传统的PLC设计方法为基础,并在时序逻辑电路的理论的指导下结合同步时序逻辑电路的分析方法和一般的设计步骤,参考和对比西门子S7-GRAPH编程语言,根据所学知识理解提出一种基于有限状态机理论的复杂PLC程序设计方法,能够较为清晰地分析整个PLC系统的所有状态,避免因为时序逻辑的复杂造成程序编程的混乱,从而有序地编写每个状态转换的程序,并且能在检查调试时更加方便,使得编程效率大幅度提高,并且能深化加强对S7-GRAPH编程语言学习和理解,达到由浅入深的效果。该方法思路能被有效地运用于到实际工艺控制系统中,有利于系统的维护和程序的扩展与修改。

[1] 鲍金艳, 蒋立军. 分散控制系统(DCS)和可编程控制器(PLC)应用技术[C]//2010年电站热工控制研讨会暨自动化信息化技术交流年会论文集, 上海, 2010:125-130.

[2] 黄丽晶. 基于 PLC的电梯控制系统设计分析[J]. 电气技术, 2016, 17(11): 125-132.

[3] 康光华. 电子技术基础数电部分[M]. 5版. 北京: 高等教育出版社, 2006.

[4] 聂旭中. 状态机设计研究[J]. 洛阳师范学院学报,2009, 28(2): 96-98.

[5] 张国庆, 霍国义. 有限状态机设计与实现方法[J].电脑编程技巧与维护, 2001, 12(12): 42-44.

[6] 李帛洋, 赵争鸣, 檀添, 等. 一种考虑死区与最小脉宽限制的 IPWM 算法[J]. 电工技术学报, 2014,29(12): 11-18.

[7] 黄招彬, 游林儒, 汪兆栋, 等. 后向离散状态事件驱动电力电子仿真方法[J]. 电工技术学报, 2017,32(12): 42-49.

[8] 齐耀辉. 异步时序逻辑电路分析方法的研究[J]. 现代电子技术, 2008, 31(6): 14-18.

[9] 陈云洽. 脉冲异步时序电路分析与设计中应注意的两个问题[J]. 电气电子教学学报, 2001, 23(3):50-52.

[10] 方振同, 梁长飞. PLC控制的剪式液压举升机设计[J]. 电气技术, 2015, 16(12): 128-130, 138.

[11] 张林, 陈洋. 基于西门子 STEP7设计平台的程序设计[J]. 黑龙江科技信息, 2015, 19(19): 146.

[12] 廖常初. S7-300/400 PLC应用技术[M]. 3版. 北京:机械工业出版社, 2012.