基于FPGA+DSP架构的数字音频处理技术研究

2018-01-15

(中国电子科技集团公司第十研究所,成都 610000)

引 言

音响中心是机载航空电子系统的重要功能单元,它完成飞行员机内通话、机外通话、指挥引导、飞行状态告警等任务,对飞机的安全和指挥控制起着关键的作用[1]。传统的音响中心采用模拟音频技术传输话音信号[2],由于模拟音频设备存在易受干扰、频带窄、可靠性差、设备体积重量大等缺点,已不再适用于有减重需求、电磁环境复杂的航空电子领域应用,因而数字音频处理技术[3]应运而生。数字音频技术是将模拟声音信号转换为数字信号,通过现代数字处理方法处理、传输话音,数字音频系统[4]具有抗干扰性强、设备体积小、重量轻、音频信号质量好等特点,因而本文提出了一种基于FPGA+DSP架构的数字音频处理系统。前端通过模拟音频电路完成模拟音频信号的A/D、D/A转换,后端通过FPGA和DSP构建数字处理平台,完成数字音频的抑制噪声、话音增强等处理。

1 系统架构

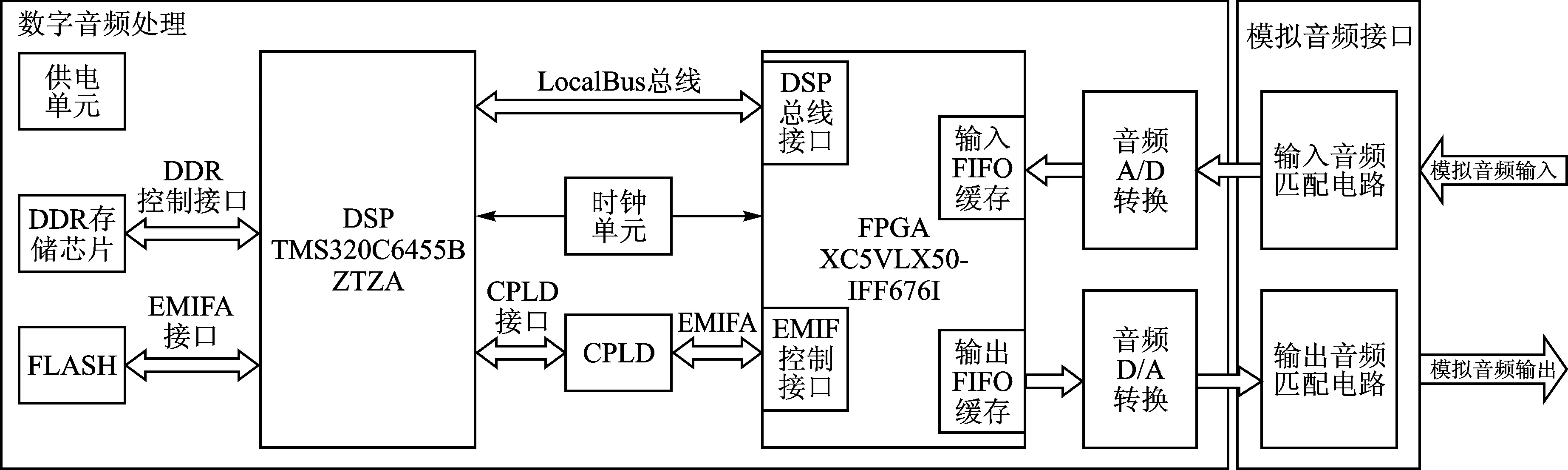

数字音频处理系统由模拟音频接口、数字音频处理两部分组成,系统框图如图1所示。其中模拟音频接口包括输入和输出两部分,输入部分完成输入模拟音频信号的阻抗匹配、信号采集、滤波和预放大,并将处理后模拟音频信号送入A/D芯片进行模/数转换;输出部分完成D/A芯片输出信号的滤波、隔直和放大,输出的模拟音频信号驱动耳机、话筒等音频设备。

数字音频部分由FPGA、DSP及外围存储控制电路组成。FPGA作为A/D芯片与DSP间通信的桥梁,对A/D或D/A数据进行缓存、组帧和串并转换,转换后的数据通过LocalBus总线接口传输给DSP进行数据处理,同时FPGA单元完成A/D芯片初始化配置、DSP时钟、复位信号输出控制等功能;DSP单元作为系统的核心处理部分,完成数字音频信号的混音、加权、编解码和音频处理算法等功能。

2 硬件电路设计

2.1 音频接口电路设计

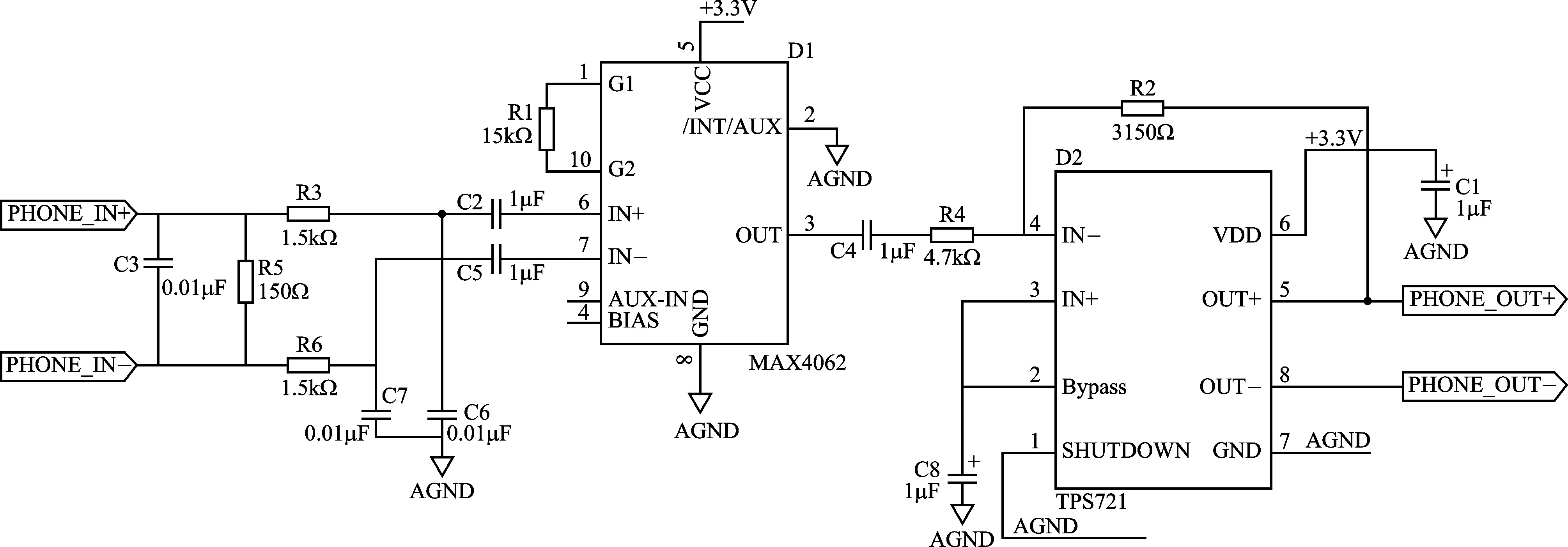

音频接口电路主要包括输入和输出两部分,输入部分如图 2所示。

图1 数字音频处理系统框图

图2 模拟音频输入接口电路

图3 模拟音频输出接口电路

前端设计RC低通滤波器(由阻容网络R3/C6、R6/C8组成),用于滤除音频信号中的杂波干扰。由于音频信号频率范围为300~3 400 Hz,为了有效滤除输入音频信号杂波并保证话音信号的平坦度,音频输入接口前端设计RC低通滤波器(由阻容网络R3/C6,R6/C7组成),截止频率设置为10 kHz左右,对输入的差分音频信号进行滤波,滤波后的信号经隔直电容(C2/C5组成)去除直流分量后送入芯片MAX4062进行预放大,放大后的信号送入TPS721芯片进行单端信号到差分信号转换,转换后通过双绞屏蔽电缆将差分信号传给后端设备进行A/D采样,这里采用差分信号传输有效降低了传输路径电磁辐射对模拟信号的干扰和衰减,减小了信号的失真。

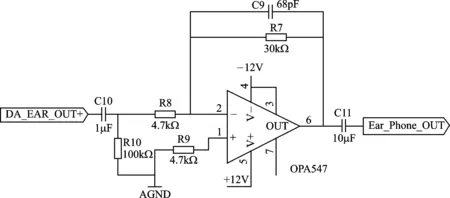

输出音频接口电路设计如图3所示,由于D/A器件采用插值算法将数字信号转换为模拟信号,D/A转换后的模拟信号中含有低频干扰和高频杂波,音频输出接口前端由低通滤波器(阻容网络C10/R10)和高通滤波器(阻容网络C9/R8)组成,两个滤波器叠加构建了带通滤波器,通带设置为200~4 000Hz左右,这样有效地滤除输出音频信号的杂波并保留了有用信息,滤波后的信号经放大器(型号为OPA547)进行负反馈放大,放大后信号经隔直电容(C11)除去直流分量后驱动耳机等音响设备。

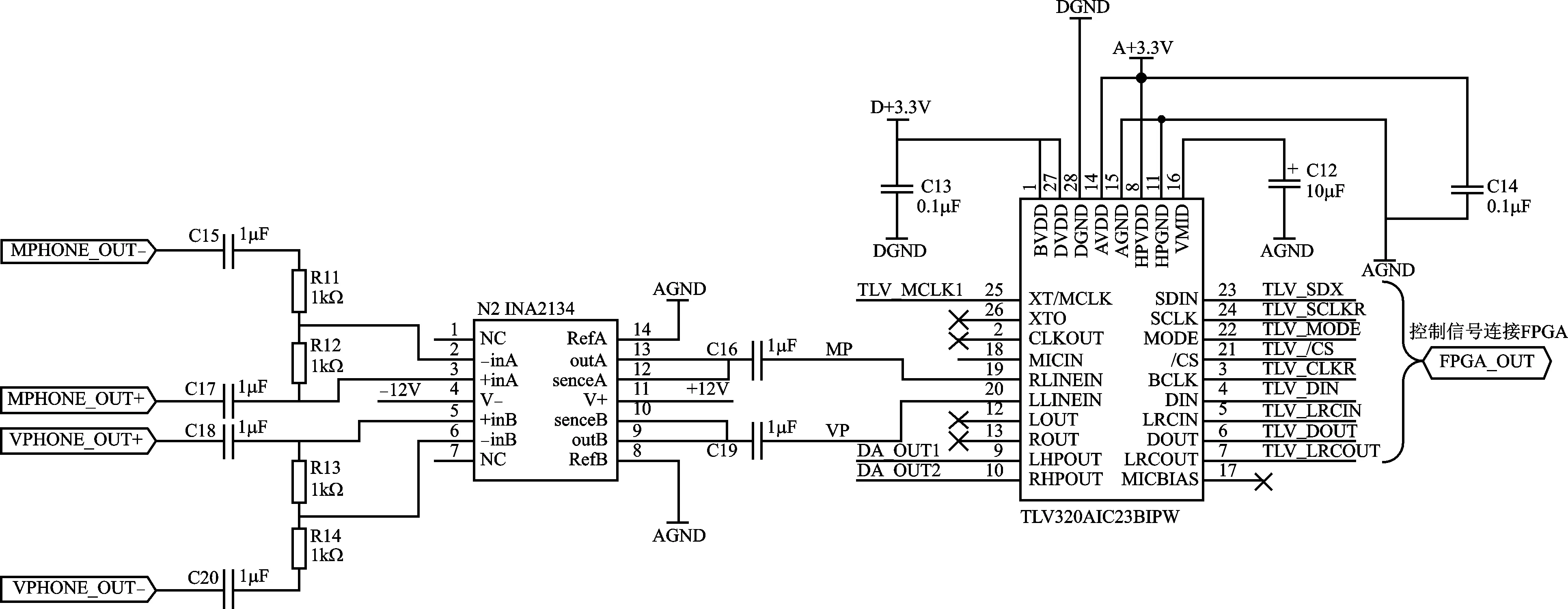

2.2 A/D及D/A电路设计

A/D和D/A转换电路完成模/数、数/模信号转换功能,如图4所示,采用TLV320AIC23B芯片完成A/D和D/A转换,TLV320AIC23B是一款高性能的音频编/解码器,该芯片内部集成A/D和D/A电路,由于TLV320AIC23B芯片由3.3 V电压供电,单端输入采样,前端设计匹配电路,采用芯片INA2134及其周围电阻网路完成信号匹配和差分单端转换;

转换后的单端信号送入TLV320AIC23B进行A/D转换;D/A电路为A/D的逆过程,FPGA端将数字信号送入TLV320AIC23B的控制端,经D/A转换后由TLV320AIC23B模拟输出引脚(9/10引脚)输出驱动后端音响设备。

图4 A/D和D/A电路

2.3 DSP和FPGA功能电路设计

DSP和FPGA功能电路框图如图5所示,DSP作为系统的处理核心,采用ADI公司的高性能处理器ADSP-21368BBPZ,该款DSP是SHARC系列浮点处理器的产品,最高主频为400 MHz,DSP最小系统包括时钟单元、供电单元、复位逻辑和外扩的SDRAM存储器和FLASH存储器,其中DSP外部片选0分配给FLASH存储器,用于存储DSP固化程序以及音频报警等,掉电不丢失数据;DSP外部片选1分配给SDRAM存储器,用于暂存程序代码和其他运行数据;DSP外部片选2分配给FPGA,用于对FPGA数据读写寻址;FPGA功能单元由时钟、配置单元和FPGA组成,时钟为FPGA工作提供时钟源,配置单元存储掉电不丢失的FPGA固化代码,上电时完成FPGA配置加载,FPGA加载完成后输出时钟、复位信号完成DSP初始化配置;FPGA与DSP间通过LocalBus总线接口通信,FPGA完成A/D数据的缓存、组帧、串并转换,并以中断方式通知DSP取数。

图5 DSP和FPGA功能电路框图

3 话音活动检测算法描述

话音活动检测算法原理是[5]:语音与噪声归一化自相关函数中极大值(即能量)的概率分布不同,因而可利用能量来对浊音及非浊音(包括清音和噪声)进行判断。由于话音信号本身具有短时平稳性,一般认为10~30 ms的时间范围是准稳态过程,在短时间内把话音信号当做一个稳态过程,采用短时能量对话音信号进行激活检测,假设第w帧话音信号Sw(n)的短时能量为Ew,计算短时能量公式如下所示:

其中N为帧长。预先设定一个阈值Y,当短时能量Ew>Y时,判断为话音;反之为噪声。

基于短时能量的方法在信噪比较高时准确性较高,但当信噪比较低时误差较高,需要结合其它方法综合判决,本文采用短时能量和过零率结合的话音端点检测方法。语音信号的短时过零率ZCR[6]是指单位时间内信号波形穿过横轴(零电平)的次数。抽样后的语音信号是离散的时间序列,其过零即是相邻两个采样改变符号的次数,定义为:

图7 音频处理仿真环境

其中sgn[.] 表示符号函数,即

研究表明信号过零率较噪声过零率低,当ZCR大于设定阈值Z时,认为是噪声;反之判定为话音。这样通过短时能量和过零率相结合的算法,能够准确检测话音端点,减少误判率和漏判率。

4 软件流程描述

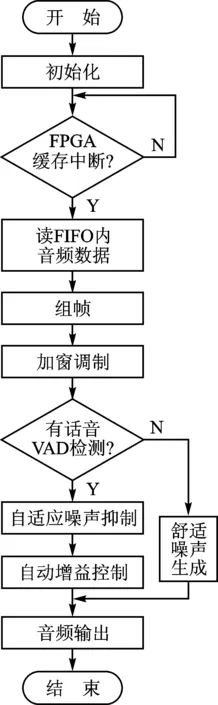

图6 音频处理算法 流程图

为了获得更好的通话效果,采用数字处理算法对话音信号进行处理。音频处理算法流程图如图6所示。

如图6所示DSP上电后运行初始化程序,完成A/D芯片、FLASH、SDRAM等硬件资源的初始化配置,同时设置中断函数实时监测是否有FPGA的缓存中断,当监测到有中断到来时调用中断响应函数,读取FIFO内音频数据。每次中断函数读取8 ms话音数据,为了满足音频准平稳信号特性,需将本次8 ms采集到的信号与前两次(16 ms)采集的信号进行组帧,构成24 ms音频数据,对组帧后的数据进行加窗,窗函数选择Hanmming窗,加窗调制后的信号送入话音活动检测模块,若检测到无话音活动送入舒适噪声生成模块重构背景噪声,噪声生成模块采用随机白噪声产生算法生成舒适白噪声,以填补话音信号中无音段。若检测到有话音活动送入自适应噪声抑制模块进行降噪处理,经噪声抑制模块去噪后的信号送入自动增益控制模块[7],经上述算法模块处理后的音频信号送入音频输出模块,对数字音频进行D/A变换、放大和匹配后输出模拟音频信号,驱动耳机、话筒等音响设备。

5 试验验证

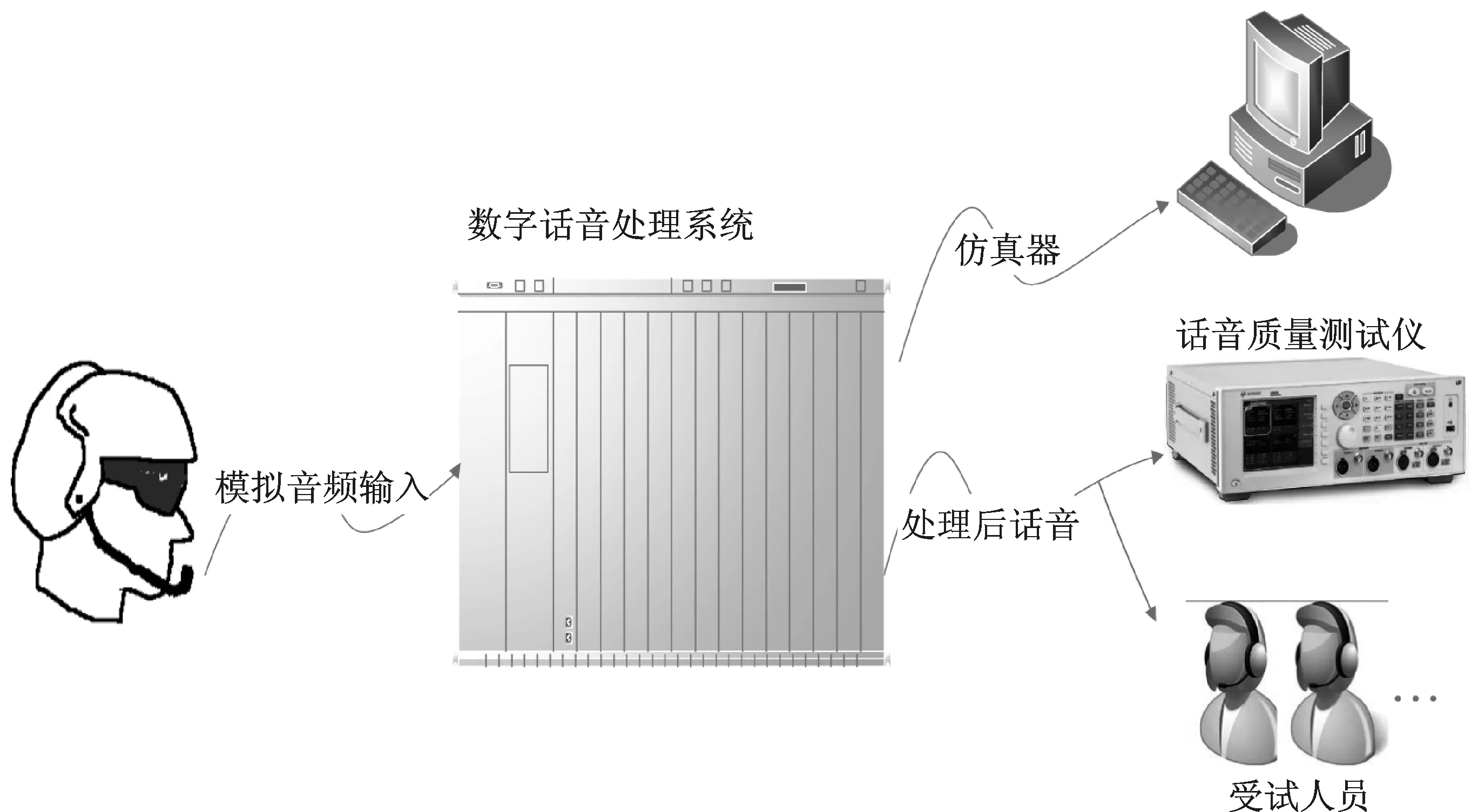

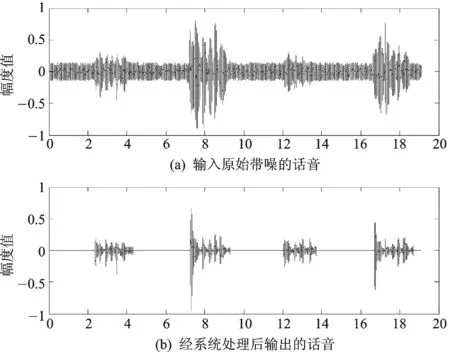

为了验证数字话音处理系统的功能和性能,搭建如图7所示验证环境。实录了一段在机载环境下信噪比为5 dB的飞行员话音信号作为输入测试激励,该信号是飞行员通话无线电设备和飞机发动机噪声叠加的带噪话音段,代表着一种常见、典型的机载音频信号。话音信号处理前与处理后的结果如图8所示。

图8 数字话音处理系统效果图

图8(a)为信噪比为5 dB的输入带噪话音段,经本系统处理后输出的音频信号如图8(b)所示,从图中可看出输入信号为带有强噪音的话音信号,经过系统处理后有音无音段被准确地识别出来,无音段的噪声信号被有效抑制,有音段的话音被明显增强。

为了进一步评价话音信号质量,采用主观和客观评价相结合的方法,其中主观评价采用ITU组织在ITU-T P.800和P.830建议书中制定的测试标准:MOS[8](Mean Opinion Score)评分测试;客观评价采用ITU组织推荐的语音传输质量测试标准P.862-PESQ算法[9],选用基于PESQ算法开发的商用话音质量测试仪进行测试,选取了10位受试者对不同信噪比的话音进行MOS评分和测试仪测试,测试结果如表1所列。

表1 话音质量评价表

从表1可看出,对比不同信噪比条件下处理前后的话音信号,处理前话音信号评分较低,话音质量较差;处理后话音信号评分有所提高,话音信号质量较好,特别是在低信噪比条件下,处理前后的评分差值更大,话音质量改善的效果更加明显。另外通过多人主观测试反映,输入信号含有强噪声的话音,音量强度忽强忽弱,舒适度差,处理后输出的话音噪声明显减弱,话音平稳,可听性好。试验结果表明,数字话音处理系统能够有效抑制噪声并改善话音质量,特别是对低信噪比条件下话音的增强起到了较好的作用。

结 语

[1] 李成文,杨军祥.新一代直升机综合核心处理机技术研究与实现[J].电子技术应用,2014(12):121-124.

[2] 杨坤.模拟音频技术与数字音频技术研究[J].科技传播,2015(7):90-91.

[3] 孙育红.数字多媒体数据采编系统设计与实现[J].现代电子技术,2017,40(15):122-125.

[4] 赵力.语音信号处理[M].北京:机械工业出版社,2016.

[5] Yonemori H,Maruyama R.A study on the Noise Suppression in High Frequency Acoustic Noise of IH Cooking Heater[J].Journal of the Japan Society of Applied Electromagnetics&Mechanics,2015,23(1):213-218.

[6] 纪振发,杨晖,李然,等.基于短时自相关及过零率的语音端点检测算法[J].电子科技,2016,29(9):52-55.

[7] Khing P P,Swanson B A,Ambikairajah E.The effect of automatic gain control structure and release time on cochlear implant speech intelligibility[J].Plos One, 2013,8(11):e82263.

[8] ITU-T Recommendation P.800. Methods for Subjective Determination of 17 Transmission Quality,1996.

[9] 陈晓翔,陆保体,林嘉宇.PESQ算法在军事语音评估中的性能分析[J].微处理机,2014,35(1):35-40.

李声飞(工程师),主要研究方向为航空机载音频信号处理、总线技术。