基于QuartusII的全加器的设计与仿真

2017-12-20于新颖

于新颖

(山西大学商务学院信息学院,山西 太原 030031)

基于QuartusII的全加器的设计与仿真

于新颖

(山西大学商务学院信息学院,山西 太原 030031)

QuartusII是Altera 公司研发的一款用于电路设计与仿真的软件。本文利用QuartusII软件自带的电路分析与仿真等功能,在QuartusII的图形开发界面进行半加器的设计,然后将其生成可调用的元件符号并用于全加器的电路设计中,对设计的全加器进行仿真,观察其运行效果。仿真表明,所设计的全加器运行效果良好,并可用于加法电路的级联当中,所以应用价值较高。

QuartusⅡ;FPGA;全加器

加法电路在信号的分析与处理领域应用范围广泛,所以对于加法器的设计与仿真就变得比较有实际应用价值;同时考虑到在电子系统的设计过程中,系统如何划分及子模块如何设计的这种层次化思想比较重要,所以本文也采用层次化的设计思路来完成一位全加器的设计[1]。即先设计半加器,然后用设计好的半加器来构建全加器。

所谓全加器,是用门电路实现两个二进制数相加并求出和的组合线路,当加数、被加数都为一位二进制数时,就称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,一位全加器实现的功能为:

{Ci,Si}=Ai+Bi+Ci-1.

(1)

其中,Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si,向相邻高位进位数为Ci。

而半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路,是实现两个一位二进制数的加法运算电路。

为了体现层次化的设计流程,我们用两个半加器来构建全加器[2]。

1 QuartusII软件的设计流程

1) 设计输入

①建立工程

A.在电脑上新建一个文件夹(注意命名不要有中文,文件夹路径不要有中文:比如文件夹直接建在D盘,命名为DOOR);

B.QuartusII中,File→New Project Wizard…(选择工程库时,加载创建的文件夹D://DOOR;工程名和顶层模块名要一致,比如命名为ANDDOOR)。

②建立设计文件

A.File→New→Block Diagram/Schematic File(图形输入)/Verilog HDL File(代码输入);

B.输入图形设计文件或者代码设计文件;

C.保存(注意工程名、顶层模块名、文件夹名要一致,一般保持默认命名即可)。

2) 编译综合

Processing→Start Compilation.

3) 仿真

①建立波形文件

A.File→New→Vector Waveform File;

B.Edit→Insert→Insert Node or Bus→Node Finder→List (注意在Pins:all条件下)→选中要观察的管脚→OK→OK.

②编辑输入管脚波形

A.仿真时间设置:Edit→End time(如设置成50us);

B.编辑输入管脚波形:

a:单击选中→ clock→设置时钟周期(如10us);

b:单击选中→ clock→设置时钟周期(如5us);

C.保存。

③生成功能仿真网表文件

Processing→Generate Functional Simulation Netlist.

④仿真模式设置

Assignments→Settings→Simulator Settings→Simulation mode:Functional →Simulation input:右侧“…”按钮加载波形文件→OK.

⑤开始仿真

Processing→Start Simulation.

4) 适配

注意:选中开发界面里器件型号,右击→Deviec→单击 Device and Pin Options→Unused Pins→选择As input tri-stated→确定→OK;下载线的USB端接电脑,方形一端接编译器,编译器SOPC端插入下面的插针里。

Assignments→Pins→Location指定到通用IO接口→关闭界面→编译综合。

5) 下载

接线→上电→Programmer→Hardware Setup→USB-Blaster→单击.sof文件→Start.

6) 硬件调试

2 全加器的设计

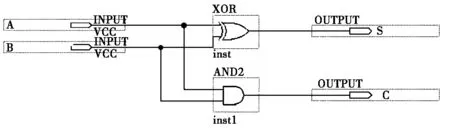

按照以上开发设计流程,在QuartusII里建立半加器的图形文件[3],如图1所示。

图1 QuartusII中半加器的设计文件

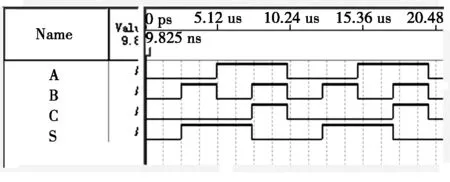

为了验证以上设计的半加器是否正确,在QuartusII中建立波形文件进行仿真,观察仿真结果和理论值是否相符,其仿真结果如图2所示。

图2 半加器的仿真结果

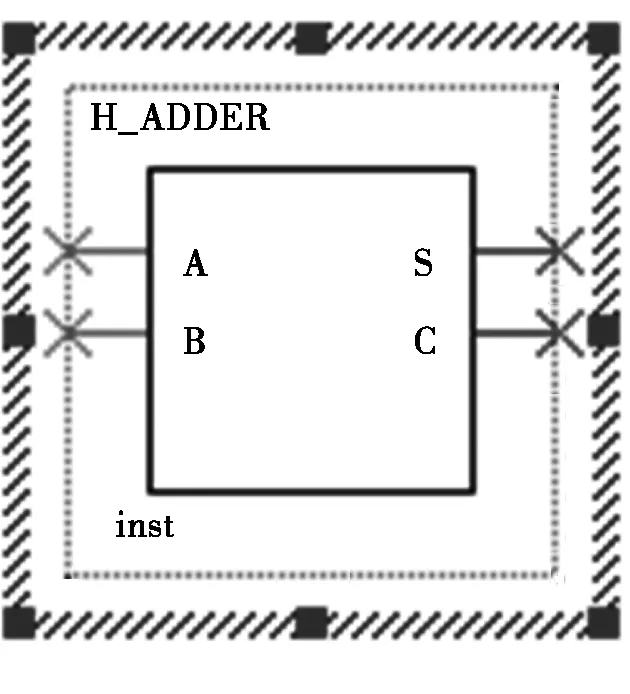

通过File→Create ∠ Update→Create Symbol Files For Current File将上述半加器生成可调用的元件符号,用于一位全加器的设计当中[4],其中生成的半加器符号如图3所示。

图3 生成的半加器元件符号

用以上生成的半加器来构建一位全加器[5],其图形设计文件如图4所示。

图4 QuartusII中一位全加器的设计文件

为了验证以上设计的一位全加器是否正确,在QuartusII中建立波形文件进行仿真,观察仿真结果和理论值是否相符,其仿真结果如图5所示。

图5 一位全加器的仿真结果

3 结果分析

通过以上设计流程,最终在QuartusII软件中完成了一位全加器的层次化设计和仿真。仿真结果表明,所设计的半加器和一位全加器的运行结果都和理论上的功能表一致,并且存在着是否存在低位进位的区别,这正体现了半加器和全加器原理上的不同。

4 结论

QuartusII软件自带电路分析和仿真等功能,所以对于电路的设计、分析及仿真等整体开发流程是非常适用的。本文通过先设计半加器,然后借助波形仿真验证其正确性;之后将验证无误的半加器生成元件符号以供顶层电路调用;最后利用半加器符号来构建一位全加器。这种设计方法体现了层次化的设计流程,而且生成的一位全加器还可以继续用于其他多位全加器的设计中。除此之外,设计的电

路还可以通过QuartusII软件自带的编程下载功能,下载到硬件芯片里,实现既定的电子系统的功能。

[1] 肖祖胜,程明.基于FPGA的数据采集分析系统设计[J].电子技术应用,2009(3):49-51.

[2] 卫星,苏先海.基于FPGA的全加器硬宏设计及优化[J].通信技术,2010(10):155-157.

[3] 江耀曦,高剑.基于多数决定逻辑非门的低功耗全加器设计[J].现代电子技术,2010(16):72-73.

[4] 陆浩,王振占.基于FPGA的高速采样电路设计与测试[J].微电子学与计算机,2011(7):106-109.

[5] 马敬敏.基于全加器的逻辑判别电路设计[J].电子设计工程,2016(2):99-100.

TheDesignandSimulationofFullAdderBasedonQuartusII

Yu Xinying

(SchoolofInformation,BusinessCollegeofShanxiUniversity,TaiyuanShanxi030031,China)

QuartusII is the software developed by Altera for circuit design and simulation. This paper designs a half adder in the graphics development interface with the circuit analysis and simulation functions of QuartusII software, and then generates the callable symbol for the file and uses it in the circuit design of the full adder to simulate the design of the full adder and observes its operating results. The simulation shows that the designed full adder works well and can be used in the cascade of the addition circuit, so it has a good application value.

QuartusII; FPGA; full adder

2017-10-09

于新颖(1987- ),女,河北唐山人,助教,硕士研究生,自适应信号处理方向。

1674- 4578(2017)06- 0022- 03

TN791

A