高能效、高可靠性和高功率密度的同步降压稳压器的设计

2017-11-21

一、前言

同步降压稳压器是一种常用的电源 ,随着各类应用要求的不断提高,行业越来越趋向于追求高能效、高可靠性、高功率密度的设计方案。比如 应用于无线局域网的负载点(PoL)电源,输入电压越来越宽,工作频率、功率密度也越来越高,随着技术的发展,甚至可将整个电源系统集成在单个封装中。

同步降压稳压器其电路结构本身非常简单, 但要完成高效可靠的同步降压稳压器的设计,还是有着不少的技术挑战,必须对稳压器电路的各种工作状态有着非常深入、透彻的了解,同时还需完成大量的计算工作。

本文将介绍快速设计出高效可靠的同步降压稳压器的技术和方法, 以及安森美半导体的 Power Supply WebDesigner在线设计工具,以便 解决所面临的技术挑战。

二、动态性能的设计

设计一个可靠的同步降压稳压器,首先必须满足其动态性能指标,如负载响应能力。而输出电感、电容的选择会直接影响到稳压器的动态性能,所以同步降压稳压器的功率电路设计通常是从选择输出电感和电容开始。

1、选择电感

从电路设计的角度,为实现快速瞬态响应, 必须选择尽可能小的输出滤波电感和最小的输出电容。然而小的电感值会增加电感电流纹波,导致电感中有效电流值增加而使得导通损耗增大,同时所导致的峰值电流的增加,也会大大增加控制管的开关损耗。

使用大电感,可减小电感中的电流纹波,从而降低稳态输出电压纹波,所导致的低峰值电流也有助于降低MOSFET的开关损耗,但电感太大不仅会导致相对较大的直流阻抗,产生较高的电感损耗,还会降低稳压器的负载响应能力,从而降低稳压器的动态性能。

为选择适当的电感,通常可假定电流纹波为电感平均电流的30%,然后根据下面的公式直接计算出合适的电感值:

其中,ΔILO—电流纹波;

fSW—开关频率。

2、选择电容

最小输出电容的选择必须考虑到两个因素,一是稳态下输出电压纹波的要求,二是当负载从满载到空载突变时所允许的最大输出过冲电压。

但输出电容也不是越大越好,太大的输出电容及电容本身的寄生串联电阻会影响到稳压器输出电路的性能以及当负载突变时稳压器的瞬态响应能力。

通常,输出电容应首选:有较小等效串联电阻(ESR)的电容, 以便降低交流损耗和输出纹波; 有较小等效串联电感(ESL)的电容, 以便在负载突变时抑制输出偏差。

三、能效设计

作为控制管和同步整流开关, 功率MOSFET广泛用于降压稳压器中,其功率消耗占稳压器功率损耗的大部分,通常决定了稳压器的整体能效。

1、选择最佳的MOSFET

针对不同的设计要求,比如是想要成本最低,还是想要损耗最低,又或是想要封装尽可能小等等,需要选择不同的MOSFET。

考虑到额定电流通常与MOSFET成本成正比,有的设计会根据额定电流的大小来选择MOSFET,希望以此来控制产品成本;为最大限度地降低导通损耗,有的设计则会选择具有最低导通电阻RDS(on)的MOSFET;还有的根据质量因数(FOM)=RDS(on)×QG(TOT)来进行选择,希望能平衡导通损耗和开关损耗……这些依赖于参数的选择方法其实都有不足。使用额定电流及电压的方法没有考虑具体的开关损耗;而最低RDS(on)法,成本可能会佷高,且MOSFET寄生电容可能导致更低的能效;FOM法则不能预测能效或成本。

因此,无论是为了降低成本,提高能效,还是为了设计更紧凑的产品,必须完整计算出电路损耗及工作温度,才能确保设计出的产品能工作在可靠的工作温度范围,达到最佳的能效。

2、计算MOSFET的损耗

在计算损耗前,需要先了解MOSFET在同步降压稳压器中的工作机制。图1所示为简化的稳压器的功率电路原理图,其中Q1为控制管,Q2为同步管。

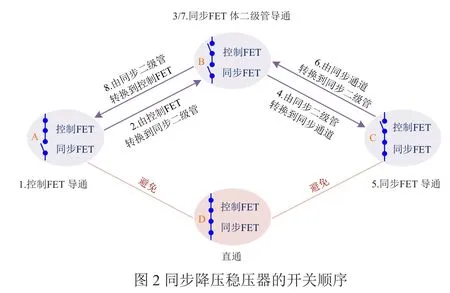

同步降压稳压器主要有3种工作状态,其开关顺序是A-B-C-B-A,如图2所示。

状态A:控制管导通,输入电流经过控制管、电感传送到输出端;

状态B:控制管和同步管同时关断,电感储能通过同步管的寄生二极管放电,传送到输出端;

状态C:同步管导通,电感储能通过同步管放电,传送到输出端。

MOSFET的功耗包括控制管和同步管的导通损耗PCOND、开关损耗PSW、栅极驱动损耗PRgate。在140kHz频率下导通损耗几乎占总功耗的70%。随着频率升高,总功耗中逐渐以开关损耗PSW为主。

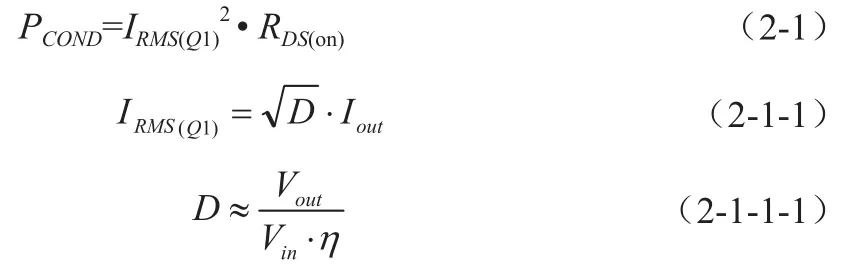

(1)控制管Q1的损耗计算

Q1工作在硬开关条件下,在小占空比或高频(〉MHz)时以开关损耗为主,开关性能受同步管Q2影响:快速di/dt可导致反向恢复损耗增加,快速dv/dt有可能引起Q2误导通,造成Q1、Q2直通现象,导致额外的损耗。另外,值得注意的是,由Q2体二极管导致的反向恢复损耗、Q2输出电容导致的输出电容损耗主要耗散于控制管Q1上[1,2]。因此,在计算Q1的开关损耗和温度时必须综合考虑到Q2的影响。另外,Q1的导通阻抗随结温上升而上升。结温越高,导通阻抗越高,导通损耗就越高,使得结温进一步上升。因此,对Q1的导通损耗必须循环反复计算,直到管子的温度计算结果稳定下来。

对于高频应用(〉MHz),控制管Q1的选用应针对降低开关损耗进行优化。图3为Q1开关损耗PSW和栅极开关电荷QG(SW)计算示意图,Q1总损耗的计算公式如下:

其中,PCOND—导通损耗;

PSW—开关损耗;

PRgate—栅极驱动损耗。

其中,IRMS(Q1)—流过MOSFET的有效输入电流值;

RDS(on)—导通阻抗;

η—期望效率;

其中,PGDRV—储存在栅极电容的能量;

RGATE—外部栅极阻抗;

RDAMP—连接于驱动器与MOSFET栅极间的外加电阻,用于防止MOSFET开通过快时可能造成的栅极信号高频振荡;

RDRV(SRC)—当Q1导通时Q1驱动器的内部阻抗;

RDRV(SNK)—当Q1关断时Q1驱动器的内部阻抗;

QG(TOT)—栅极总充电电荷;

VGATE—栅极电压。

其中,PCoss—输出电容损耗,Q2输出电容损耗主要耗散于Q1上;

PQrr—Q2体二极管导致的反向恢复损耗,主要耗散于Q1上;

ILval—电感谷底电流,即控制管开通瞬间时输出电感中的电流;

ILpk—电感在一个线性周期内的最大峰值电流;

IDRV(SRC)—当Q1导通时Q1驱动器的内部电流;

IDRV(SNK)—当Q1关断时Q1驱动器的内部电流;

ts(on)—Q1导通时间;

ts(off)—Q1关断时间;

Qrr—Q2体二极管反向恢复充电电荷;

QG(SW)—栅极开关电荷;

QGD—栅漏充电电荷;

QGS—栅源充电电荷;

Coss—Q2输出电容;

gFS—MOSFET的正向跨导。

Q1的导通损耗PCOND随输入电压Vin增加而降低,开关损耗PSW随Vin增加而增加,栅极驱动损耗PRgate与Vin无关。当Vin为最大或最小时,Q1的总损耗最大。

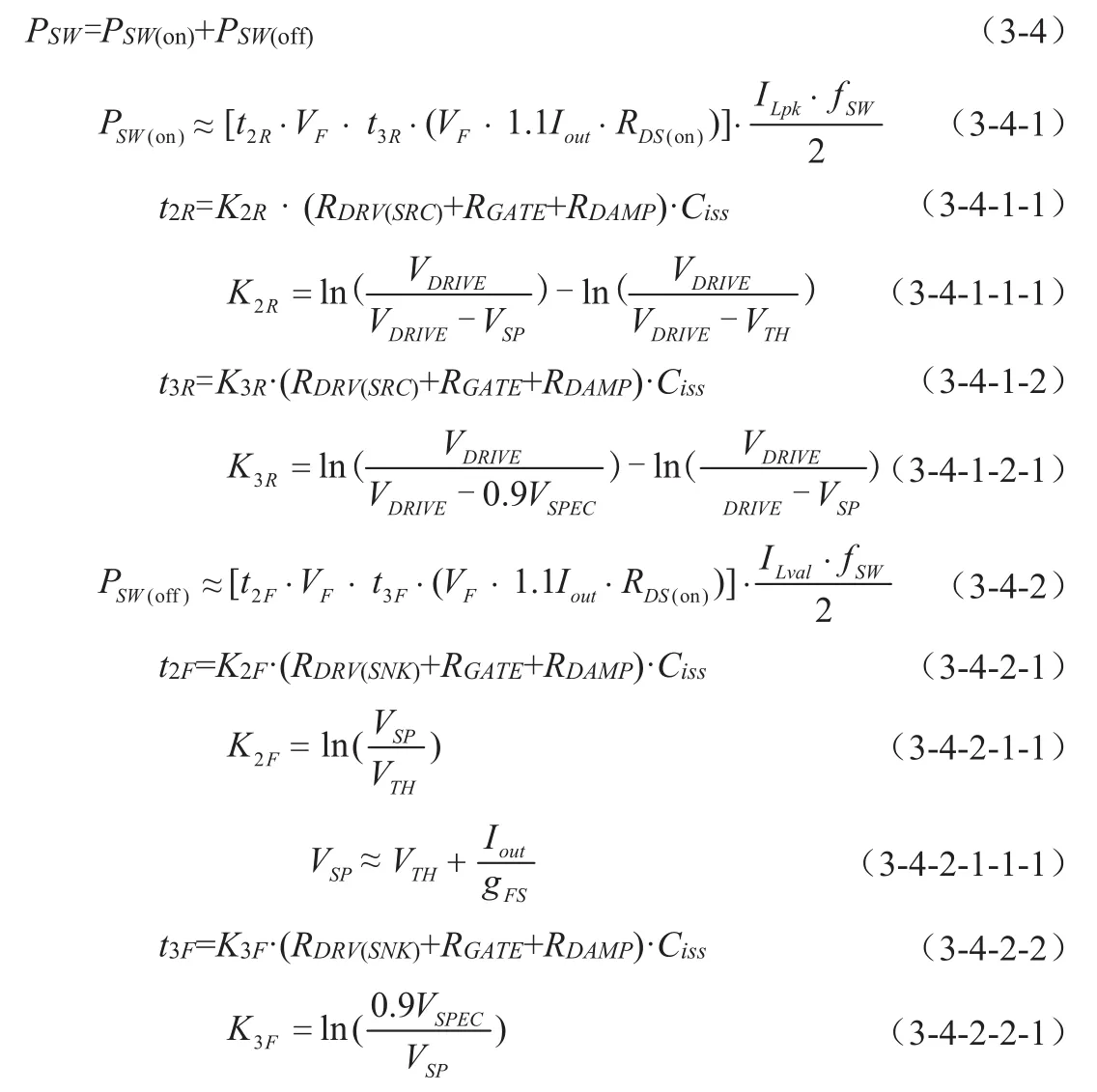

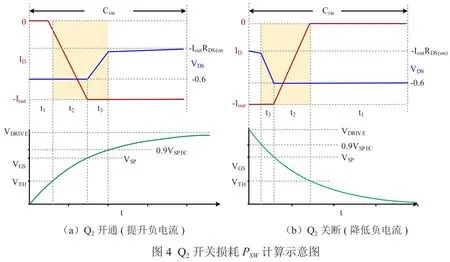

(2)同步管Q2的损耗计算

Q2工作在零电压开关(ZVS)条件下,当fSW〈1.5 MHz时通常以导通损耗为主,在选择Q2时,建议选用具有低FOM(低RDS(on)×QG(TOT))的MOSFET,以降低Q2的总损耗,或者低QGD/QGS比率(〈1)以防止快速dv/dt引起Q1、Q2的直通现象。对于高频应用,选用集成肖特基体二极管的MOSFET,以降低反向恢复损耗以及二极管导通损耗。

图4 为Q2开关损耗PSW计算示意图,Q2的损耗计算公式如下:

其中,PDcond—Q2二极管导通损耗,在死区时间,MOSFE都是关断的,体二极管(或并联的肖特基)在传导电感电流;

其中,tdead(on)—在检测到Q1栅极关断和Q2的栅极驱动电压VGS达到阈值之间的总的死区时间;

tdead(off)—在检测到Q2栅极关断和Q1导通之间的总的死区时间;

tdelay(on)—导通延迟时间,在检测到Q1栅极关断和Q2开始导通之间,驱动器的内部调节的或可编程的延迟时间(自适应死区时间);

tdelay(off)—关断延迟时间,在检测到Q2栅极关断和Q1开始导通之间,驱动器的延迟通常远远超过tdelay(on)以避免误触发Q2;

VDRIVE—栅极上的电压幅度;

VTH—阈值电压。

其中,RDRV(SRC)—Q2导通(源电流)时Q2驱动器的内部阻抗;

RDRV(SNK)—Q2关断(汲电流)时Q2驱动器的内部阻抗。

其中,t2R—Q2开通时沟道电流上升时间段t2;

t3R—Q2开通时沟道电流上升时间段t3,在此期间体二极管关断;

t2F—Q2关断时沟道电流下降时间段t2;

t3F—Q2关断时沟道电流下降时间段t3,在此期间体二极管开通;

K2R、K3R、K2F、K3F—为简化计算公式而引入的变量;

Ciss—当VDS接近0V时的输入电容,约为数据表中Ciss典型值的1.25倍;

VF—肖特基二极管的压降,约为0.6V;

VSPEC—当MOSFET阻抗为RDS(on)时的栅极电压;VSP—米勒平台电压。

其中,TJ—工作结温

RθJA—结 -环境热阻;

TA—环境空气温度。

Q2的导通损耗PCOND随Vin升高而增加,开关损耗PSW只是随着Vin升高而略微增加。而Q2的寄生二极管导通损耗PDcond和栅极驱动损耗PRgate都与Vin无关。因此,当Vin为最大时,Q2损耗最大。

综上所述,当Vin为最大或最小时,Q1+Q2总的损耗最大。进行计算时,必须同时考虑Q1和Q2的相互影响。

四、设计示例

以下通过一个设计示例, 演示如何完成控制管Q1和同步管Q2的优化选择。如果要设计一个输出为5V、10A的同步降压稳压器,其输入电压Vin=8~16V,工作频率fSW=350kHz。考虑到20%的安全裕量及开关节点的电压振荡,可初步选择额定电压30V以上、额定电流IDCONT额定值≥定值≥T电流关的MOSFET。然后,根据具体的应用要求,确定MOSFET的封装要求。为简化演示,我们选择采用5×6mm PQFN (Power 56) 封装的器件。

综合以上选择条件,安森美半导体的产品阵容中有超过150个器件供选择,我们需再进一步从中挑选出合适的Q1和Q2。同样为简化演示,我们将列出用于Q1和Q2的各12个器件。

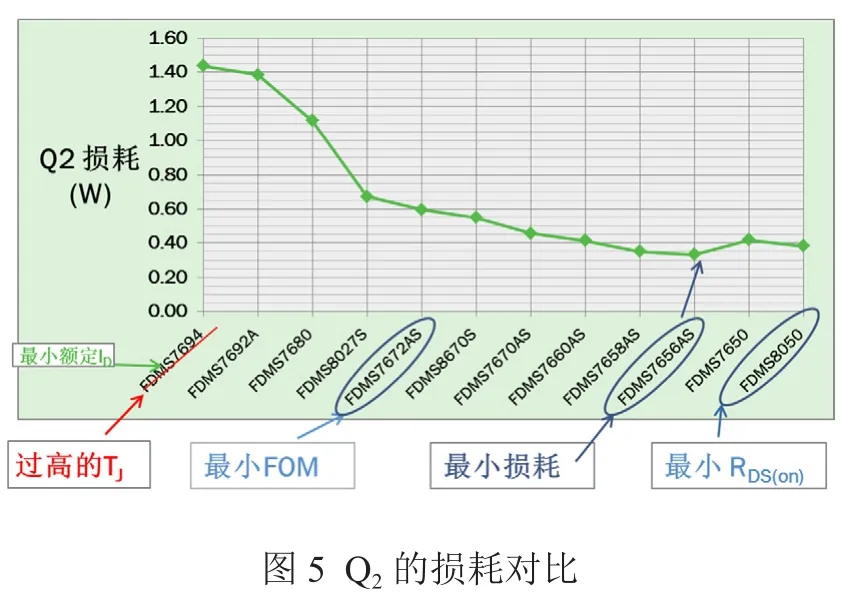

对 于Q2,Vin=Vin-max时损耗最大。图5所示的12个器件中,FDMS7656AS有最低的最大损耗。但由于Q2寄生参数会影响Q1的 开关损耗,最小Q2损耗通常并不意味着最佳的总能效。必须比较Q1及Q2的总功耗来找到最佳的Q2以实现最高能效。

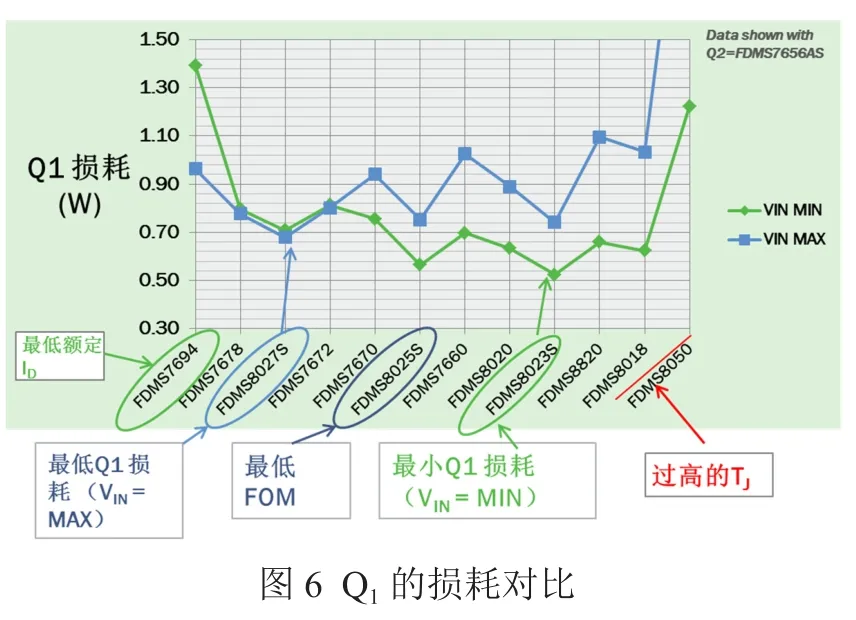

对于Q1,Vin=Vin-max或Vin-min时损耗最大。图6所示12个器件中,FDMS8027S和FDMS8023S分别在Vin=Vin-max或Vin-min时有最低的最大损耗的Q1。

为优化转换器能效,首先根据Vin选择损耗最小的Q1,然后选择产生损耗最小的Q2。本例中,无论Vin最小或最大,最佳的Q2是相同的,都为FDMS7658AS(但并不总是如此,特别是具有宽Vin范围或高fSW时),见表1。

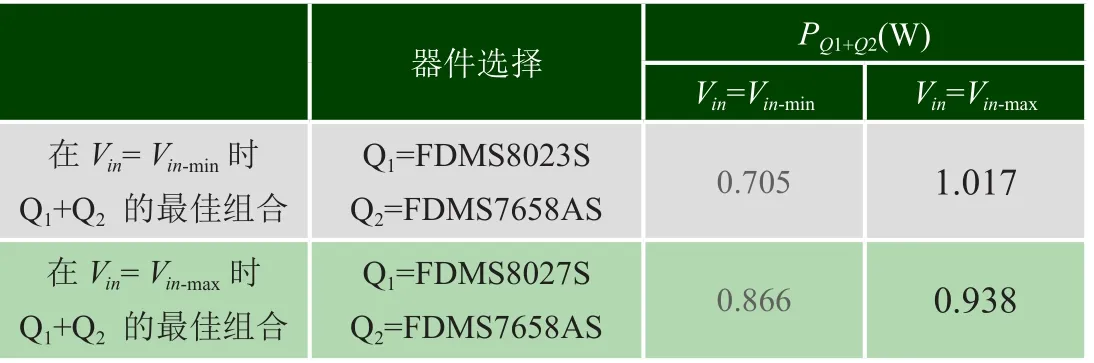

表1 优化组合Q1和Q2

由于当Vin=Vin-max或Vin-min时,Q1+Q2总的损耗最大,我们需对总的损耗进行对比,选择最大损耗最低的最佳组合。如表2所示,选用FDMS8027S为Q1,FDMS7658AS为Q2时,Q1+Q2的最大损耗最低。

表2 优化组合Q1和Q2 —总的损耗PQ1+Q2 对比

上述设计示例表明,在设计同步降压稳压器时,为选择最佳的Q1和Q2需进行大量繁琐复杂的计算。为 更快速完成高效可靠的设计,可选用安森美半导体的在线设计平台Power Supply WebDesigner以加速FET优化,如图7所示 。

通过在线设计平台Power Supply WebDesigner里的Synchronous Buck功率回路损耗分析工具Power Train Loss,可轻松对比合格MOSFET器件的数据及性能,自动排除超过TJ限制的器件,选择设计裕量和工作温度范围,选择单个或双重封装的MOSFET,根据额定电压、电流或封装筛选器件,添加并联器件和栅极阻尼电阻, 立即计算出不同的Q1+Q2组合的损耗。

在完成选定Q1和Q2后,可获得输入电压笵围和负载笵围内功率回路的各类损耗和能效曲线,并根据各类曲线和功率回路能效汇总表针对不同的设计进行完整的分析、比较。

六、总结

为满足行业高能效、高可靠性和高功率密度的设计趋势,在进行同步降压稳压器的设计时,需从动态性能、能效设计等方面综合考虑。通过仔细调整元器件值,能够相对容易地实现优化的动态性能,但处理和优化MOSFET功耗的技术通常较为繁琐复杂。Power Supply WebDesigner可帮助简化设计流程,加速MOSFET优化选择。

(本文由安森美半导体供稿)