二维半导体过渡金属硫化物的逻辑集成器件∗

2017-11-10李卫胜周健王瀚宸汪树贤于志浩黎松林施毅王欣然

李卫胜 周健 王瀚宸 汪树贤 于志浩 黎松林 施毅 王欣然

(南京大学电子科学与工程学院,固体微结构国家重点实验室,人工微结构科学与技术协同创新中心,南京 210093)

二维半导体过渡金属硫化物的逻辑集成器件∗

李卫胜 周健 王瀚宸 汪树贤 于志浩 黎松林 施毅 王欣然†

(南京大学电子科学与工程学院,固体微结构国家重点实验室,人工微结构科学与技术协同创新中心,南京 210093)

(2017年9月11日收到;2017年10月3日收到修改稿)

过渡金属硫族化合物,晶体管,迁移率,逻辑集成

1 引 言

过去五十多年来,摩尔定律作为集成电路产业发展的黄金准则,指导着晶体管几何尺寸不断缩小,工艺不断创新,目前发展到14—10 nm节点[1,2].大量新技术[3]被引入半导体工艺,其中应变硅[4,5],高κ栅极电介质(κ为相对介电常数)[6]、金属栅极[7]、三栅(Fin-FET)结构[8]的引入使得晶体管性能不断提高,同时也使器件工艺变得越加复杂.随着器件尺寸进入亚100 nm尺度,短沟道效应带来的功耗问题使得全球半导体行业正面临着前所未有的巨大挑战.为了克服大规模集成带来的功耗问题,同时延续摩尔定律带来的成本优势,以新材料、新结构和新原理为主要特征的后摩尔时代新器件技术开始受到广泛的关注,并成为微纳电子科学的重要前沿.2016年,国际半导体技术发展路线图升级为2.0版本(International Roadmap for Semiconductors 2.0,ITRS2.0),对后摩尔时代微电子器件技术发展路线做了新的定义[9].在ITRS2.0中,将超越-互补性金属氧化物半导体晶体管(beyond complementary metal oxide semiconductor,Beyond-CMOS)器件列为重点研发领域,希望通过探索新的器件工作原理来实现超高性能和超低功耗.同时,异质集成技术受到广泛关注,一方面利用新材料提高CMOS和存储器件的性能,另一方面将不同功能的智慧器件与CMOS单片集成,以实现功能更丰富的集成电路产品.

二维层状材料是近年来国际学术界和工业界关注的前沿热点,这类材料层内一般由共价键组成,层间靠范德瓦耳斯力结合,单层厚度一般在1 nm以下.目前已知有500种以上的二维原子晶体[10].该领域的研究热潮从2004年单层石墨烯的成功剥离开始[11],由于其特殊的性质与广泛的应用前景,英国曼彻斯特大学的两位科学家Geim与Novoselov于2010年获得诺贝尔物理学奖.石墨烯的超高迁移率对于微电子器件来说无疑是一个巨大的研究动力,但是其零带隙极大地限制了逻辑器件应用.尽管研究人员发展了多种在石墨烯中打开带隙的方法,包括石墨烯纳米带[12]、双层AB堆垛[13]、氢化/氧化石墨烯[14]等,但都无法同时保持高迁移率和高开关比.目前,国际主流的观点认为石墨烯不适合做数字逻辑器件,更适合做模拟射频器件.

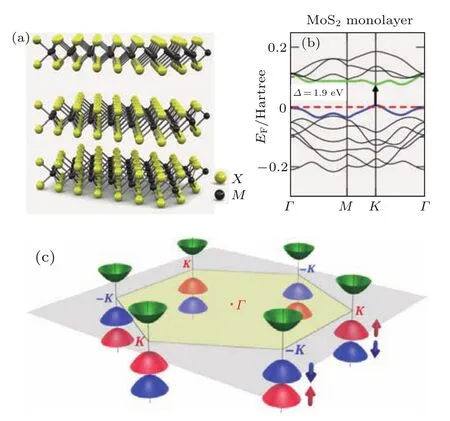

近几年,对于二维逻辑电子器件的研究逐渐由石墨烯过渡到二维半导体材料,它们具有非零带隙,解决了石墨烯的最大瓶颈.其中过渡金属硫化物(transition metal dichalcogenides,TMDC)是由过渡金属(M)以及硫族元素(X)以MX2为化学组分形成的层状三明治结构[15,16],单层厚度小于1 nm,如图1(a)所示.根据硫族元素(通常为S,Se,Te)和过渡金属元素的不同,存在超过40种不同的材料[17].表1展示了常见的TMDC及其物理性质[18],涵盖了半导体、金属、绝缘体、半金属、超导体等形态[19].随着研究的不断深入,人们还发现了带隙随层数可调控[20]、电子输运各向异性[21]、拓扑奇异性[22]、电荷密度波[23]等奇异物性,并发展出能谷电子学等新概念[24].此外,多种二维材料可以自由组合形成范德瓦耳斯异质结,不受传统半导体外延生长晶格匹配的限制.目前,科学家已经实现了基于TMDC范德瓦耳斯异质结的隧穿晶体管、光电二极管、光电探测器等原型器件[25].由于TMDC的结构和性质有望给微电子技术带来新的变革,美国国家科学基金会、半导体研究联盟和欧盟都投入了大量的经费,在材料制备、原型器件与系统集成等方面进行深入研究.

在TMDC中,VI族TMDC和硒化物(MoS2,WS2,MoSe2,WSe2)是半导体材料,具有1—2 eV的带隙、良好的空气稳定性和工艺兼容性,并可以由化学气相沉积(chemical vapor deposition,CVD)大面积合成,因此最适合逻辑器件集成(如果没有特殊说明,下文中的TMDC特指VI族TMDC和硒化物).利用半导体TMDC作为逻辑晶体管的沟道材料,有以下3个优势.

图1 (a)TMDC中,典型MX2结构的三维示意图[26];(b)单层MoS2的能带结构示意图[27];(c)单层MoS2的自旋特性[28],在MoS2的能带结构中,在K和K′(−K)点,价带的能谷和相反的自旋轨道分裂Fig.1.(a)Three-dimensional schematic representation of a typical MX2structure[26],with the chalcogenide atoms(X)in yellow and the metal atoms(M)in grey.(b)Band structures of monolayer MoS2calculated at the DFT/PBE level[27].The horizontal dashed lines indicate the Fermi level.The arrows indicate the fundamental band gap(direct or indirect)for a given system.The top of valence band(blue/dark gray)and bottom of conduction band(green/light gray)are highlighted.(c)Band structure of MoS2 showing six valleys and opposite spin-orbit splitting of the valence band at the K and K′(−K)points[28].The red and blue surfaces represent spin-orbit-split valence band maxima,each of which is associated with a particular electron spin.The green surfaces represent the conduction band minima or the valleys.

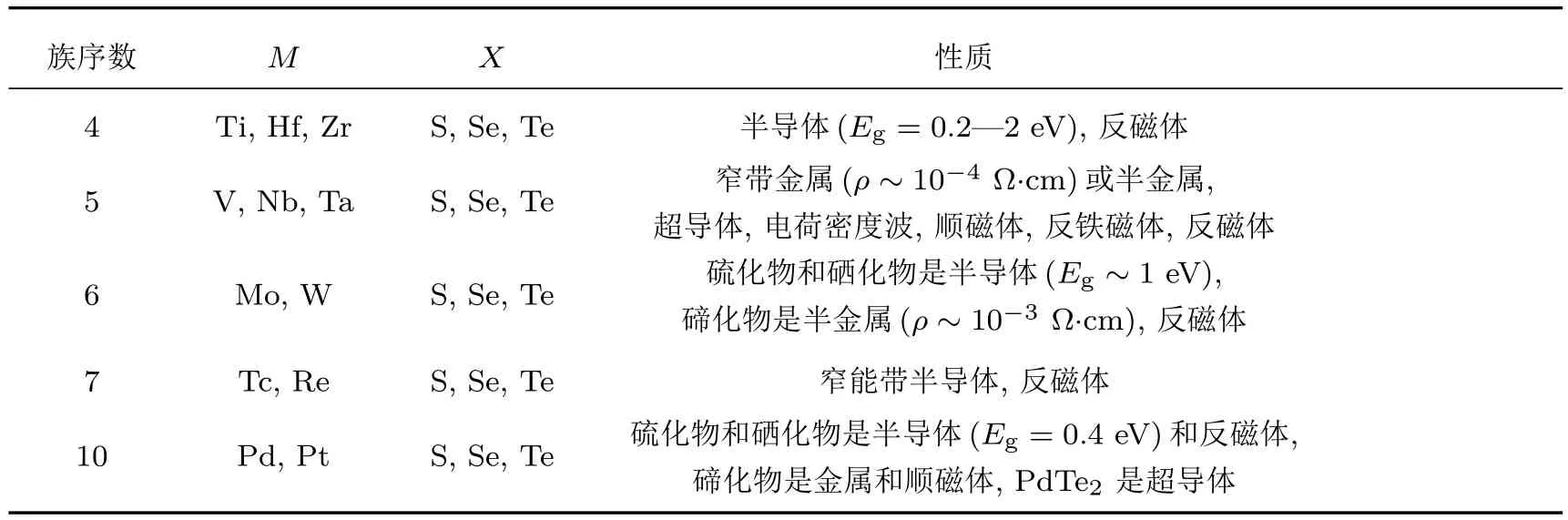

表1 TMDC材料及其性质的汇总[18]Table 1.Summary of TMDC material types and their properties[18].

1)其超薄的结构可以将载流子限制在界面1 nm的空间内,在工艺节点继续缩小的情况下有效抑制晶体管的短沟道效应,降低器件功耗,有望解决摩尔定律进一步向前发展的最大瓶颈.理论预测在极限器件尺寸下,二维晶体管性能将超越硅基器件[29,30].2016年,加州大学伯克利分校的Ali Javey等在《Science》发表论文,利用单根碳纳米管作为栅极,成功实现了具有优异开关性能、栅长为1 nm的MoS2场效应晶体管(FET),开关比达到106,亚阈值摆幅为65 mV/dec,证明MoS2可以作为器件尺寸缩小的终极沟道材料(如图2(a)和(b)所示)[31].

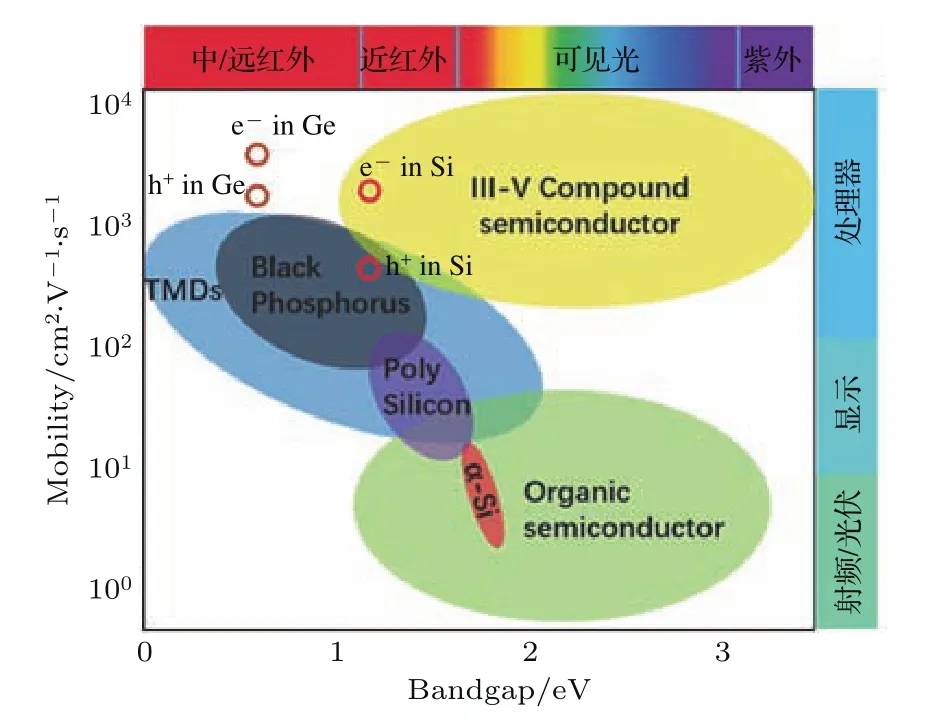

2)表面没有化学悬空键,在空气和工艺环境下有良好的稳定性,可以在极限厚度下仍然保持较高的迁移率.传统的半导体材料随着厚度减小到10 nm以下,表面态显著增加,不可避免的表面粗糙度会对载流子产生强烈的散射,导致迁移率随厚度的6次方迅速降低.而TMDC即使在单层情况下仍能保持较高的迁移率(如图3所示[32]),例如单层MoS2室温下的声子散射理论迁移率为410 cm2·V−1·s−1[33],WS2,PtSe2材料甚至超过了1000 cm2·V−1·s−1[34], 远高于同等厚度下的硅材料.

3)TMDC器件与目前的硅基微电子技术具有良好的兼容性.2014年,Chen等[35]报道了一种与硅基CMOS完全兼容的工艺,将少层MoS2集成到硅基鳍式场效应晶体管(Fin-FET)和纳米线FET中,形成Si/MoS2复合沟道.2016年,他们进一步报道了硅基集成的U形MoS2晶体管.利用掺杂的Si作为源/漏,将MoS2自对准的生长在源漏之间形成沟道.10 nm栅长的MoS2p-MOS器件展现出了优异的性能:开关比>105,Ion>150µA/µm[36].

图2 (a)1 nm栅长MoS2晶体管的结构示意图和(b)1 nm栅长MoS2晶体管的转移曲线和输出曲线[31];(c),(d)硅基集成的10 nm U形MoS2p-MOS晶体管的透射电子显微镜表征和转移曲线[36]Fig.2.(a)Schematic of 1D gated,2D semiconductor field-effect transistor(1D2D-FET)with a MoS2channel and single-walled carbon nanotube(SWCNT)gate.(b)ID-VGScharacteristics of a bilayer MoS2channel SWCNT gated FET at VBS=5 V and VDS=50 mV and 1 V.The positive VBSvoltage electrostatically dopes the extension regions n+.And ID-VDScharacteristic for the device at VBS=5 V and varying VGS[31].(c)Transmission electron microscopy picture shows uniform 4 nm MoS2over the S/D side walls and the 10 nm S/D gap.(d)Transfer curve of a 10 nm channel MoS2p-MOSFET with Ion/Ioff>105[36].

考虑到以上的因素,ITRS对二维材料在高性能低功耗逻辑器件上有着很好的预期.例如,单层MoS2器件完全可以满足2023年ITRS的低功耗逻辑器件目标:操作电压不高于0.62 V,栅长小于8.1 nm,静态电流低于100 nA/µm.弹道输运下的MoS2FET时延可以达到60 fs,这远远小于ITRS对Si基金属氧化物场效应晶体管半导体(MOSFET)的要求,更超过了ITRS最低的140 fs的要求[32].此外,单层的半导体TMDC中,自旋和能谷是锁定的,能量简并但不等价的两个能谷K和−K有着不同的光选择定则[28,37],这使得可以使用不同偏振的光(σ+,σ−)激发不同能谷的载流子,从而实现对自旋-能谷的调控[19,24,38],被认为是重要的超越CMOS器件应用.

图3 不同半导体的迁移率能带关系图(上边框的色标呈现了从紫外到红外的光谱,有边框色标呈现了半导体的不同应用)[32]Fig.3.Plot of mobility vs bandgap for various semiconductors.The color scale represents the spectrum from ultraviolet to infrared[32].

尽管早在1963年第一个MoS2薄膜晶体管诞生时,TMDC的半导体性质便已经被发现,但其在电子器件中的应用一直并未受到重视[39].2004年,WSe2首次被制备成晶体管,其具备较高载流子迁移率以及双极性的特点,但同时因为其禁带宽度以及工艺的限制,开关比偏低[40].通过量子输运理论模拟,洛桑联邦理工学院Radisavljevic和Kis[6]将单层MoS2双栅器件与3 nm厚体硅器件进行对比,发现前者漏致势垒降低效应下降52%,亚阈值摆幅降低13%,并且能够满足ITRS提出的关于逻辑器件在2023年性能指标.同时,在如此极限的条件下,器件将进入弹道输运,二维材料中电子和空穴相对质量较大,因此相对于体硅晶体管具备更大的态密度以及弹道电流.2011年,他们利用厚度仅为6.5 Å的单层MoS2作为沟道,首次实现了开关比为108的FET,掀起了TMDC的研究热潮[26].同年11月份,他们首次实现了基于单层MoS2的集成电路,该电路可以实现反相器的功能,即当室温电压增益大于1时,其可以实现从逻辑“1”到逻辑“0”的功能[41].2012年,麻省理工学院Palacios等[42]利用双层MoS2制作了增强型和耗尽型n-MOS晶体管,并在此基础上演示了反相器、静态随机存取存储器(static random access memory,SRAM)、五级环形振荡器等逻辑集成器件,振荡频率最高达到1.6 MHz.2016年,维也纳科技大学Mueller等[43]利用CVD MoS2首次实现了1 bit微型处理器,该系统由115个晶体管构成,具有可以执行用户存储在外部存储器的程序、执行逻辑操作以及与周边用户进行通讯等功能,更重要的是,其1 bit设计对于多bit数据依旧稳定,创造了目前利用二维材料制作出最复杂电路的记录.

获得高质量大面积的二维TMDC材料是研究和发展其在微电子学领域应用的前提.2012年,阿卜杜拉国王科技大学Li等[44]首次利用MoO3和硫粉作为反应源,采用CVD方法在SiO2衬底上实现单层MoS2晶体的合成.随后,众多研究组致力于大尺寸高质量的晶体生长[44−53],目前已实现了毫米级单晶以及晶圆级多晶材料的生长.同时随着生长工艺的不断优化,基于CVD生长的晶体器件性能也显著提高,中国科学院物理研究所张广宇等[54]在蓝宝石衬底上生长的单层MoS2单晶可达350 µm,其FET室温迁移率达到90 cm2·V−1·s−1.新加坡国立大学Loh等[55]利用常压CVD方法,在熔融玻璃上生长出2.5 mm的MoSe2单晶,其室温场效应迁移率高达95 cm2·V−1·s−1, 是目前CVD MoS2的最高记录.

目前针对TMDC逻辑器件研究主要集中在载流子输运[32,56]、界面与材料工程[57,58]、电学接触与掺杂[59,60]、逻辑与存储器件以及工艺集成[15,61−63]等领域.本文针对以上关键问题展开讨论,介绍一些具有代表性的研究成果,第二部分以MoS2为例讨论TMDC中的电子输运性质,重点关注迁移率及其与表/界面的关系;第三部分讨论TMDC晶体管的接触,包括降低接触电阻的主要手段;第四部分讨论TMDC存储器件的发展以及逻辑集成;最后对该领域未来的发展进行展望.

2 TMDC迁移率

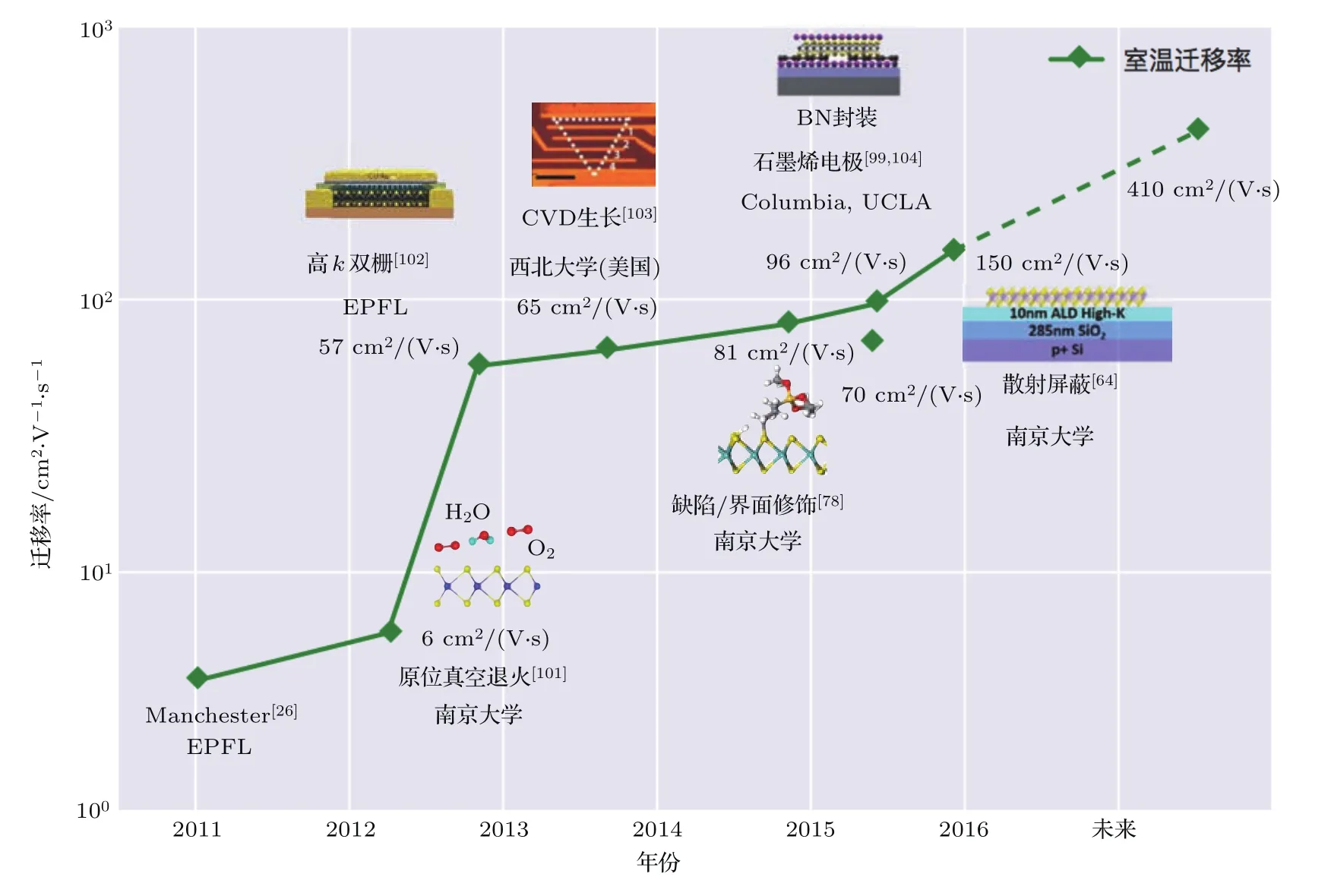

尽管TMDC是延伸摩尔定律的重要候选材料,但最近的研究结果表明,它们的电子输运受到很多外在因素的限制.目前报道的实验迁移率都远低于声子散射的理论极限值.例如,单层MoS2和WS2在室温下的理论声子极限迁移率分别约为410 cm2·V−1·s−1[33]和1100 cm2·V−1·s−1[34], 然而,对于这两种材料而言,实验记录分别仅能达到150 cm2·V−1·s−1[64]和80 cm2·V−1·s−1[65]. 因此,迁移率问题严重影响了TMDC的器件性能.经过电子输运的研究发现[32,56,58,63,66,67],这些外在因素主要包括半导体-电介质界面的库仑杂质、材料声子、氧化物表面光学声子、缺陷和电荷陷阱等(图4),它们会显著降低载流子的散射自由程,从而降低迁移率.在本部分对TMDC的各种散射机理研究进展进行阐述,以期能够寻找提高TMDC迁移率的方法和思路.

图4 MoS2器件中的电子散射机理[56] (a)电子声子对散射;(b)氧化物表面光学声子散射;(c)库仑杂质散射;(d)缺陷散射;(e)电荷陷阱Fig.4.Electron transport mechanism in MoS2channel devices[56]:(a)Electron-phonon scattering;(b)remote phonon scattering;(c)coulomb impurity scattering;(d)defection scattering;(e)electron trap.

2.1 散射机理

2.1.1 本征电子-声子散射

在无任何外在散射源的情况下,材料的迁移率会受限于电子和不同类型晶格声子的相互作用.本征声子极限迁移率是一个非常重要的概念,它决定了无任何杂质和缺陷的样品所能实现的最高迁移率,并且可以作为评价实验样品质量的标尺.丹麦技术大学Kaasbjerg等[33]发现,内部声子散射率来源于电子与纵向声学声子、横向声学声子、谷内极化纵向光学声子(Fröhlich acoustic)、谷间极化纵向声子和谷内单极光学声子等五种声子的作用,相应的动量弛豫速率函数则为这五个相应部分的和.这些作用的强弱程度会随温度变化:在100 K以下,单层MoS2中的内部声子限制性迁移率主要是由声学声子决定的,与温度T−1.7呈线性关系,随着温度升高,载流子与内部声子的作用由光学声子主导,从而此时声子限制性迁移率与T−1呈线性关系.在300 K时,在不考虑库仑杂质散射和表面光学声子散射的情况下,单层MoS2中的迁移率能够达到410 cm2·V−1·s−1.

2.1.2 氧化物表面光学声子

在半导体中,电子可以通过长程库仑作用在周围的电介质材料中激发出声子.在HfO2等高κ绝缘体中,金属-氧原子间的化学键非常容易发生极化,从而会在接触面上产生一个能够库仑散射的局域极化电场.在半导体工艺常用的绝缘体(如SiO2,Al2O3,HfO2等)中,氧化物表面光学声子所造成的电子非弹性散射会显著地降低MoS2的迁移率.如图4(b)所示,靠近MoS2材料的电介质提供了对极化振动模式的支持,那么就会产生氧化物表面光学声子(又名远程光学声子),这种远程声子散射在晶体硅[68,69]、有机晶体管[70,71]和石墨烯[72,73]器件中均被广泛观测到.界面处的远程声子散射由界面材料声子模式能量决定,其声子模式能量越低,对载流子传输的散射越明显.一般来说,随着材料表面场强的增加以及介电常数变大,其表面光学声子的能量会逐渐降低,进而导致更加严重的远程界面声子散射.对于有多重远程声子模式的材料(如六方氮化硼(h-BN)等),其远程声子散射为几种模式的叠加.由于载流子屏蔽作用的影响,远程界面声子散射主导的迁移率会随着载流子浓度增加逐渐增大.同时远程界面声子表现出极强的温度依赖性,其散射会随温度升高快速增强,导致迁移率快速下降,因此远程界面声子散射是器件高温主要散射源之一.此外,对于高κ双栅结构器件,由于新界面引入,其远程界面声子散射会变得更加严重[32].

2.1.3 库仑杂质散射

在二维系统中,由于载流子都分布在表面,其传输会严重受分布在沟道和介质界面上的带电杂质散射,每个带电杂质会产生一个长程库仑势场.图4(c)形象地表明了位于沟道界面上下表面的两个带电杂质所产生的散射势.实验证明,在晶体硅FET[74]、石墨烯[75]、单层MoS2[76]中,带电杂质都是影响迁移率的主要因素之一.在硅晶体管中,带电杂质主要来自于残存的金属离子和沟道介质界面上不饱和成键的硅原子.而在TMDC中,带电杂质的来源还包括器件制作过程中吸附的气体分子,化学物质残留、缺陷以及氧化物的表面电荷等.在同样载流子浓度的情况下,采用例如HfO2的高κ栅介质层,能够提高电子迁移率,正是因为对于库仑散射的介电屏蔽效应.德克萨斯大学达拉斯分校Ong和Fischetti[76]建立了电荷杂质散射模型,计算了在高κ氧化物顶栅结构中,单层MoS2在不同温度和电子浓度下的库仑杂质限制迁移率.他们发现,引入高κ氧化物顶栅后,室温迁移率可以提升数倍,并解释了实验上的结果[6,40,77].由于极化屏蔽作用依赖于温度,单层MoS2的库仑杂质限制迁移率会随着温度的增加而降低.随后,南京大学王欣然等[32]通过实验和理论研究发现,高载流子浓度对于库仑杂质也同样起到屏蔽效应,当载流子浓度从1012cm−2提高到1013cm−2时,迁移率也随着上升,同时他们还发现,相应的库仑杂质限制迁移率会受温度变化的影响[32].

2.1.4 缺陷散射

各种方式制备的TMDC都不可避免地存在空位(图4(d))、晶界[78−82]等各种结构缺陷.例如CVD方法生长出来的MoS2样品,其硫原子空缺密度能够达到(1.2±0.4)×1013cm−2,密度高达0.4%.这些缺陷会产生高度局域化的带间电子态或者带尾,从而影响TMDC的电子运输[83−86].有大量的理论计算和实验研究了MoS2的缺陷对能带结构和性质的影响,例如MoS2中的硫原子空位在石油化学中可以被用来催化去硫[83,84]以及加速水分解[85,86].南京大学王欣然等[79]发现硫空位缺陷导致在低载流子浓度下MoS2电荷跃迁输运,是导致低迁移率的重要原因.除了硫原子缺陷外,晶界缺陷也在样品中广泛存在.哥伦比亚大学van der Zande等[50]研究了室温下机械剥离MoS2以及CVD合成MoS2样品的迁移率,比较发现了器件的表现既取决于晶界的类型,也取决其与电流运输的相对方向.

2.1.5 电荷陷阱与金属-绝缘体相变

电子输运中的俘获效应在硅、有机材料等体相材料中被广泛研究,在二维TMDC中其也是影响载流子迁移率的重要因素之一.如图4(e)所示,晶格缺陷、化学吸附、悬挂键以及电介质衬底的粗糙界面都会成为电荷俘获源.IBM研究中心Zhu等[87]测试了单层CVD MoS2晶体管的电容和ac电导,通过拟合实验数据,首次实现了对MoS2晶体管电荷陷阱进行定量分析.他们通过实现发现在MoS2禁带中间存在两种不同类型的电荷陷阱,并且根据其在带间位置命名出“B”和“M”类型电子陷阱.同时他们发现量子类型的陷阱在带间均以高斯分布的形式存在.

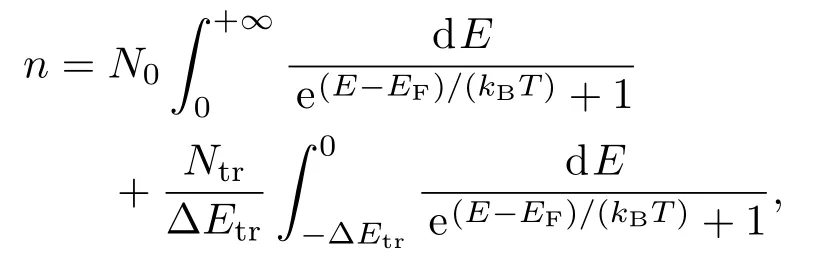

为了定量理解MoS2中的电荷陷阱对电子输运的影响,南京大学王欣然等[32]发展了一个用来解释载流子浓度减少的模型,并计算了有效的载流子迁移率.假定电荷陷阱是在禁带中以单边高斯分布的形式存在,其载流子浓度n可以通过分布函数计算:

其中,N0为外延态密度,Ntr为电荷陷阱总密度;ΔEtr,EF,kB和T分别为特征宽度、费米能级、玻尔兹曼常数和温度;等号右边第一项为扩展态决定的电子浓度,第二项为电荷陷阱决定的电子浓度.本质上,电荷陷阱通过减少传输电子的数量来降低迁移率.简单而言,被俘获的电子只能通过跳跃式来进行传输,这种方式效率非常低,对于电导率的贡献可忽略不计,因此有效迁移率µeff就等于导电的电子乘以能带迁移率:

这个模型在高载流子浓度的情况下与实验结果符合得较好,原因是此时被俘获的电子浓度只占总数的很小一部分,而在低载流子浓度下,电子跃迁输运占主导.

2.2 界面工程

鉴于单层TMDC的超薄属性,界面在TMDC电子输运中具有非常关键的作用.衬底上的悬挂键、粗糙的表面和吸附物都会带来库仑杂质和电荷陷阱.对于单层TMDC,其电子在垂直平面方向不能发生极化和屏蔽外电场,因此,它们容易受到界面库仑杂质的影响.比较常用的界面工程方法包括界面钝化、高κ介质和h-BN包裹.

自组装单分子层(self-assembled monolayers,SAM)被广泛地用于界面钝化,减少氧化物衬底的库仑杂质[88−91].由于末端基团不同,SAM的种类非常多,有些SAM还具有掺杂效果.例如,十八烷基三甲氧基硅烷(OTMS)处理氧化硅衬底,可以有效降低库仑杂质密度,使得石墨烯室温迁移率增加到47000 cm2·V−1·s−1[91]. 哈尔滨工业大学甄良等[92]研究了不同端基的SAM分子对MoS2的掺杂效应,结果表明因为SAM分子与MoS2之间的电荷转移,具有—CF3和—NH2端基的SAM分子分别具有空穴施主和电子施主的作用.莱斯大学Lou等[93]利用带有硫氢基的SAM处理SiO2衬底,使得MoS2的室温迁移率提高了六倍, 高达18 cm2·V−1·s−1. 性能提升的原因在于界面电荷转移和分子极化,降低了缺陷密度,抑制了远程声子散射.南京大学王欣然等[78]发展了一种双面(3-巯基丙基)三甲氧基硅烷(MPS)处理的方法,通过溶液SAM手段对SiO2衬底处理,贴上机械剥离MoS2,MPS包裹和热学退火,不但可以钝化衬底界面,而且可以同时修复MoS2的S空位缺陷.他们制作的单层MOS2晶体管室温迁移率提升至80 cm2·V−1·s−1, 低温迁移率提升至300 cm2·V−1·s−1(图5). 利用模型分析发现,器件中库仑杂质密度和电荷陷阱密度降为NCI=0.71×1012cm−2和Ntr=5.2×1012cm−2,这是所有SAM处理中最低的.

图5 近几年关于室温下单层MoS2FET迁移率的进展[26,64,78,99,101−104]Fig.5.Recent progress on the mobility of monolayer MoS2FET at room temperature[26,64,78,99,101−104].

使用高κ介质衬底取代SiO2的动机在于其可以通过介电屏蔽效应抑制库仑杂质散射.南京大学王欣然等[64]通过在SiO2上沉积薄层(10 nm)HfO2或Al2O3,比较不同衬底的晶体管性能(使用双面MPS处理的MoS2作为沟道),研究并验证了该理论.相比顶栅结构,这个方法不会引入额外的库仑杂质和电荷陷阱,在高载流子浓度下,迁移率会随着介电常数的增大而提高.在HfO2衬底上,MoS2室温迁移率高达150 cm2·V−1·s−1,创造了目前为止单层MoS2最高室温迁移率的记录(图5).然而,使用高κ衬底的弊端在于增加了表面光学声子散射.模型分析表明,当库仑杂质密度低于0.3×1012cm−2时,使用高κ衬底不再有优势.因而,最好的方式是使用具有低库仑杂质密度和低κ衬底,例如h-BN.

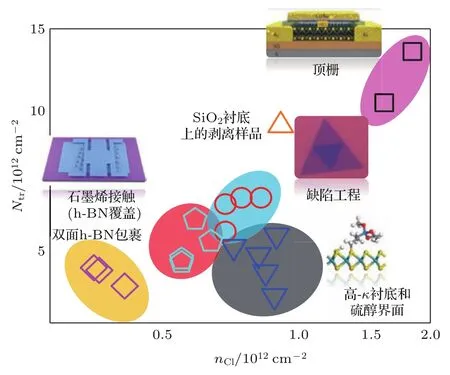

众所周知,h-BN具有非常干净的界面,对于众多二维材料而言,是一种非常理想的衬底[94]. h-BN包裹的石墨烯器件展现出140000 cm2·V−1·s−1的超高迁移率和许多新奇的量子现象[16,95−98]. 因此,h-BN包裹被期望可以降低TMDC中的库仑杂质和电荷陷阱.对于仅在顶部覆盖h-BN的MoS2而言,室温迁移率提升至60 cm2·V−1·s−1, 低温迁移率提升至280 cm2·V−1·s−1[99]. 此外, 加州大学洛杉矶分校段镶锋等[99]利用双面h-BN包裹和石墨烯接触相结合,低温迁移率超过1000 cm2·V−1·s−1.2015年,哥伦比亚大学Hone等[95]也利用相同结构,制作了多层MoS2的霍尔器件,实现了超高的低温霍尔迁移率(34000 cm2·V−1·s−1), 并且首次观察了MoS2中的Shubnikov-de Haas(SdH)振荡效应.香港科技大学王宁等[100]研究了h-BN衬底上的单层MoS2,发现能带诱导输运和陷阱诱导输运的临界载流子浓度约为1.0×1013cm−2,与我们的模型结果一致.尽管如此,双面h-BN包裹的MoS2样品,其库仑杂质密度仍然比同样结构的石墨烯高出3个数量级,这表明库仑杂质部分来源于MoS2本身的缺陷和吸附.然而,对于库仑杂质和电荷陷阱最准确的微观起源仍然是不清楚的,需要继续深入研究.最后,需要指出的是,h-BN包裹是研究TMDC本征性质最好的手段,但是大规模的器件应用仍十分困难.

2.3 单层MoS2迁移率模型

虽然前面分析了TMDC中的各种散射机理,但事实上利用不同方法制作的TMDC晶体管,电学数据(包括转移、输出曲线、迁移率随温度和载流子浓度变化等)差异很大,这里面包含了非常丰富的信息,通常容易被忽视.如果能建立一个完整的理论模型,从器件的电学数据入手,对电子散射机理进行分析,准确提取微观参数,将会指导器件性能的进一步提高.南京大学王欣然与新加坡IHPC张刚等基于本文2.1节的内容,发展了单层MoS2迁移率模型:

其中µ0为电子迁移率;µSO,µph,µCI和µD分别为表面光学声子、固有声子、库仑杂质和缺陷限制下的迁移率;σ为电导率;e为元电荷;nc为扩展态决定的载流子浓度;µeff为有效迁移率.

利用该模型可以对文献中不同工艺制备的单层MoS2晶体管数据(迁移率随温度/载流子浓度的变化)进行分析,定量提取带电杂质、电荷陷阱浓度等重要微观参数,并实现各种结构晶体管的横向对比[32].图6展示了利用迁移率模型对典型的高性能HfO2/SiO2衬底单层MoS2晶体管的分析.从转移曲线(图6(b))可见,在载流子浓度约为n0=CgVg=5.3×1012cm−2时,不同温度下的曲线存在交叠.当载流子浓度n大于n0的情况下,电导率会随着温度单调增加,相应地表现为绝缘体的导电特性;反之则电导率会单调下降,表现为金属的导电特性.研究发现,这是陷阱诱导的金属-绝缘体转变的标志.通过对比各种散射机理,发现在低带电杂质和高载流子浓度的情况下,由于屏蔽效应有效抑制了库仑散射,器件在高于200 K时的迁移率主要由声子散射主导,随着温度降低,声子散射影响迅速减弱,器件进入库仑散射主导区间.随着载流子浓度降低,载流子屏蔽效应减弱,器件迁移率下降,并且在整个变温区间内其均由声子散射/库仑散射/短程散射等多重散射机理主导.当载流子浓度接近或低于电荷陷阱的浓度,大部分或全部电子填充在带间局域态,局域化的电子在各个局域化的电荷中心以跃迁形式传输,其输运行为则表现出电荷陷阱主导的跃迁行为,其迁移率在低温下表现出明显的下降趋势,器件则表现出明显的绝缘体特性.

图6 典型HfO2/SiO2衬底的MoS2晶体管的分析[32] (a)器件结构;(b)四探针法测得不同温度下器件电导率随栅压的变化;(c)—(e)不同载流子浓度(n=1.0×1013cm−2,5.6×1012cm−2,5.6×1012cm−2)下的迁移率温度变化曲线Fig.6.Analysis of typical HfO2/SiO2Substrate MoS2MOSFET[32]:(a)Device structure;(b)four-probe conductivity as a function of Vg;(c)–(e) field-effect mobility as a function of temperature under n=1.0 × 1013cm−2,5.6×1012cm−2,and 5.6×1012cm−2.

图7 高性能单层MoS2晶体管的库仑杂质浓度和电荷陷阱浓度的相图[32]Fig.7.Phase diagram for the coulomb impurities and charge traps in the high-performance FETs from literature[32].

我们利用模型分析了文献中报道的数据(图7),得到了以下结论:1)制作顶栅晶体管可以显著提高载流子浓度,但是顶栅工艺会导致杂质与陷阱浓度增大;2)界面修饰和高κ介质可以降低杂质和陷阱浓度,结合介电屏蔽作用,有效提高了MoS2晶体管迁移率;3)双面h-BN包裹的器件库仑杂质和电荷陷阱密度已分别降低至(0.3—0.4)×1012cm−2和(4.0—4.6)×1012cm−2,是目前报道最干净的界面.该模型对TMDC具有普适性,只需要修改有效质量、介电常数、声子能量等材料的本征参数,就可以用于其他TMDC的晶体管数据分析.该工作表明,TMDC的迁移率不仅仅是一个数字指标,背后蕴藏了更丰富的物理内涵.通过对数据的细致分析,可以揭示TMDC的电子散射机理,并指导器件性能继续向前发展.

3 TMDC电学接触

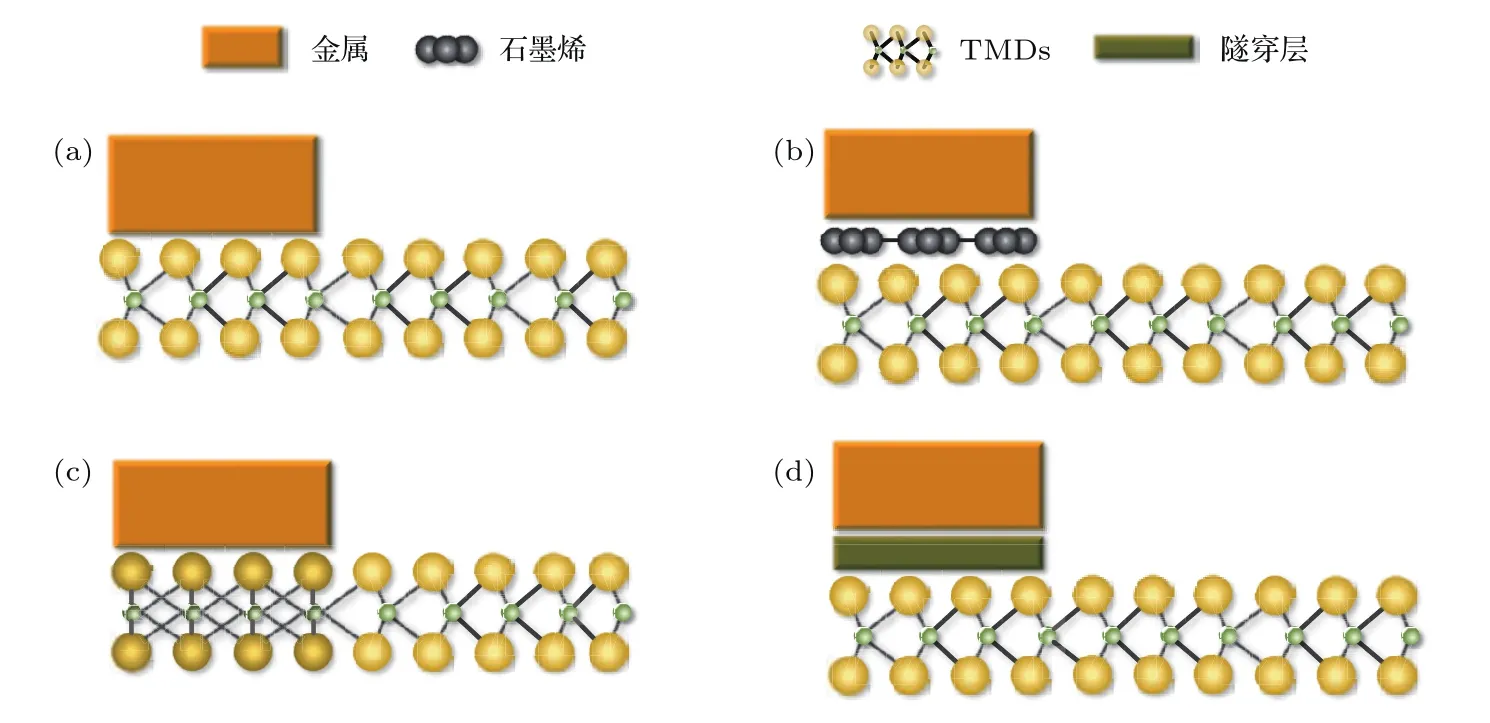

FET的总电阻由接触电阻(Rc)+沟道电阻(Rch)两部分组成.TMDC由于表面没有化学键,无法与金属成键,因此肖特基势垒较高,载流子注入效率低,接触电阻一般比硅基MOSFET高一个数量级以上,尤其在短沟道条件下成为限制器件电流的主要因素.因此,降低接触电阻是提升TMDC晶体管性能的另一个关键问题.在过去几年中,研究人员发展了多种方法有效地降低了接触电阻,主要包括金属-TMDC,石墨烯-TMDC,TMDC相变接触和隧穿接触(图8).本部分从这四个方面介绍目前TMDC晶体管电学接触的研究进展.

图8 二维半导体TMDC晶体管的电学接触类型 (a)金属-半导体接触;(b)石墨烯接触;(c)相变接触;(d)隧穿接触Fig.8.Electrical contact types of two-dimensional semiconductor TMDC transistor:(a)Metal-semiconductor contact;(b)graphene contact;(c)phase transition contact;(d)tunneling contact.

3.1 金属-TMDC接触

典型的金属-单层TMDC接触电阻在1—100 kΩ·µm量级,比硅基CMOS器件的接触电阻(0.1 kΩ·µm)高出1—3个数量级.一般来说,降低金属-TMDC接触电阻的方法分为两类:一是改变接触电极金属的种类,使其功函数与沟道材料的功函数相近,降低界面的接触电阻;二是掺杂沟道材料,改变沟道材料的载流子密度,改善界面的接触电阻.本部分将从这两个方面,系统阐述科学家在降低接触电阻方面的最新进展.

3.1.1 不同金属对接触的影响

根据肖特基势垒的理论,高/低功函数金属可以与p/n型半导体之间形成很小的肖特基势垒,从而降低接触电阻.2012年,普渡大学Das等[105]在实验上研究了不同金属(Pt,Ni,Sc和Ti)作为接触电极时MoS2器件性能的差异,发现对于n型MoS2器件,使用低功函数的金属Sc能够实现较高性能的电子注入和较低的接触电阻.同年,密歇根州立大学 Tománek等[106]通过ab initio密度泛函理论对金属-单层MoS2接触区域的电子结构、键合和几何构型进行了理论研究,发现Au-MoS2界面存在很大的隧穿势垒和很低的电子注入效率;而Ti-MoS2界面可以形成低阻值的欧姆接触,但根据肖特基理论,二者之间的肖特基势垒较大(约为0.3 eV).2013年,加州大学圣巴巴拉分校Banerjee等[107]利用Ti做电极,在多层MoS2晶体管上测得实际接触电阻为0.8 kΩ·µm,发现造成这种低阻值的原因是Ti与MoS2之间的边缘接触增加了电极与沟道之间的电子注入效率.2014年,该团队又考虑到金属-TMDC间的范德瓦耳斯相互作用,通过ab initio密度泛函理论对金属-单层TMDC材料的接触进行了系统的研究,利用隧穿势垒(金属-TMDC界面的范德瓦耳斯能隙)、肖特基势垒(金属-TMDC界面的费米面差异)和轨道重叠(金属-TMDC界面的电子云重叠)三个指标,系统评估了不同金属与单层MoS2的界面接触[108,109].他们发现金属Ti和Mo可以与单层MoS2形成欧姆接触,前者是源于Ti-MoS2界面具有很小的隧穿势垒,提高了电子注入效率;后者是因为Mo-MoS2接触界面具有更高的晶格匹配度,从而具有更高的电子注入效率.随后在实验上,该团队测得MoS2-Ti和MoS2-Mo之间的接触电阻分别为1.3 kΩ·µm[110]和2 kΩ·µm[111].

3.1.2 掺杂对接触的影响

重掺杂会使得肖特基势垒宽度降低,金属-半导体接触的电流以隧穿的方式得到极大提升.对于传统的半导体,掺杂可以通过杂质扩散或者离子注入的方式进行精确操控,而对于二维TMDC半导体材料,其特有的表面没有悬挂键和原子级的厚度等特性,因此必须寻找新的掺杂方法.

2014年,普渡大学Ye等[112]提出了一种将MoS2薄片浸泡在二氯乙烷(DCE),以实现n型氯掺杂二维TMDC材料的方法.掺杂后,氯原子占据了MoS2和WS2中的硫原子空位,使得费米能级上移,肖特基势垒降低,Ni-WS2和Ni-MoS2体系的接触电阻得到有效的降低,分别为0.7 kΩ·µm和0.5 kΩ·µm.由于MoS2和WS2存在很多的硫原子空位,相应氯原子的掺杂浓度很高,多层WS2和MoS2在零栅压下可以达到6.0×1011cm−2和9.2×1012cm−2的高掺杂密度.

表面电荷传输掺杂是指利用二维半导体材料具有极大的表面积特性,去吸附更多的小分子,进而改变半导体的载流子浓度的掺杂方法.2012年,加州大学伯克利分校Javey等[113]提出了对二维半导体TMDC运用表面吸附掺杂的方法,对二维半导体TMDC材料实现了有效掺杂,降低了接触电阻.目前,对二维半导体TMDC实现表面电荷传输掺杂的报道有很多[113−117].2014年,该团队利用联苄吡啶(benzyl viologen,BV),作为表面电荷传输施主,实现了对MoS2的有效n型掺杂[117].研究发现,使用Ni/Au电极制作的5 nm MoS2FET,掺杂前器件的接触电阻为3.3 kΩ·µm,掺杂后接触电阻降为1.1 kΩ·µm.并且,这种掺杂方法具有空气稳定、不退化的特性.此外,可以通过浸泡甲苯试剂,消除掺杂的影响.

2015年,德克萨斯大学奥斯汀分校Rai等[118]证明了高κ介电质氧化物可以作为有效的n型电荷转移掺杂剂实现对单层MoS2的掺杂.他们利用ATO(amorphous titanium suboxide)作为高κ掺杂剂,通过旋涂ATO薄膜的方法,对单层MoS2进行了n型掺杂,使用Ag/Au电极制作了单层MoS2晶体管.ATO的有效掺杂使得接触电阻低至约180 Ω·µm, 室温迁移率提高至102 cm2·V−1·s−1.通过理论计算发现,ATO掺杂是一种以界面氧空位调制的掺杂方式.ATO掺杂不仅可以改善接触,有效降低肖特基势垒,而且作为一种高κ介电材料,可以有效屏蔽库仑杂质散射,抑制表面光学声子散射,使得MoS2晶体管的性能得到极大的提升.随后,2017年,斯坦福大学Pop等[119]通过在单层MoS2晶体管的沟道表面沉积一层不饱和氧化铝AlOx的方式,对MoS2进行了n型掺杂,使得接触电阻降低至480 Ω·µm,开态电流密度提高至700µA/µm.图9展示了接触电阻、光学能隙与层数的关系.

3.2 相变接触

相变接触是指将二维材料的多个相用于器件的不同部分:半导体相用作沟道,金属相用作电极,两相之间通过化学键相连,可以实现无缝接触的一种接触方式(图8(b)).相变接触界面没有范德瓦耳斯能隙,具有原子级的接触边界,可以实现载流子的高效注入.罗格斯大学Chhowalla等[123]首先发现可以对半导体2H相MoS2纳米片进行局域化诱导相变,使得部分区域变为金属1T相MoS2.他们将金属1T相作为电极,半导体2H相作为沟道材料,制作出无缝接触的MoS2FET[127].测试表明其接触电阻在零栅压下为200—300 Ω·µm,主要来自于金属1T相和半导体2T相之间原子级的明显界面,这也是目前报道最低的接触电阻之一.相变接触对于未来发展TMDC材料的集成设计提供了一个很好的思路,但目前诱导相变的手段是通过溶液处理的方法实施的,精准度较低,制备出的器件性能不稳定.发展出无损相变诱变的手段将成为降低接触电阻的一个重要方向.

3.3 石墨烯-TMDC接触

石墨烯-TMDC接触是指用石墨烯作电极,TMDC作沟道材料形成的一种接触(图8(c)).石墨烯是一种具有超高迁移率的半金属,与TMDC可以实现原子级的接触界面;并且石墨烯具有零带隙,其功函数可以被栅压调控,有效地降低肖特基势垒.2015年,加州大学洛杉矶分校段镶锋等[99]利用石墨烯做电极,实现了MoS2的欧姆接触.实验表明,在合适的栅压控制下,石墨烯和MoS2可以形成良好的接触,其实现了在超低温(低于19 K)下真正的零势垒和线性输出特性.并且,得益于极小的接触势垒,他们的MoS2-FET实现了1300 cm2·V−1·s−1的低温场效应迁移率. 为了减少MoS2外在的散射机理影响,改善器件的界面接触,哥伦比亚大学Hone等[95]提出了一种范德瓦耳斯异质结器件,该器件将MoS2层包裹在两层h-BN内,用石墨烯做电极,制作成霍尔器件.磁输运测试结果显示,六层MoS2器件在低温下创造了高达34000 cm2·V−1·s−1的霍尔迁移率记录,证实了之前的低温特性现象是由外在的界面杂质所影响的,排除了MoS2固有体相缺陷的影响.之后,他们又利用该结构制作了双栅FET,研究表明,其具有高质量的电学接触,室温下两端载流子迁移率在33—151 cm2·V−1·s−1,亚阈值摆幅为80 mV/dec[128].

随后,新加坡国立大学Thong等[129,130]利用干法转移方法和金属催化石墨烯处理过程,在MoS2上制备了镍刻蚀石墨烯电极,这种镍刻蚀石墨烯电极和MoS2仅有约200 Ω·µm的接触电阻.相比纯镍电极,接触电阻降低了两个数量级,这是由于镍石墨烯电极具有很低的功函数,并且被处理的石墨烯存在zigzag边缘,增强了石墨烯和镍之间的隧穿效率.2014年,韦恩州立大学Zhou等[131]在WSe2上覆盖h-BN,制造了以石墨烯为源漏电极,离子液为顶栅的FET.使用超大电双层电容的离子液,极大地扩展了石墨烯功函数的可调范围.多层WSe2晶体管的接触电阻低于2 kΩ·µm.由于石墨烯的功函数靠近WSe2的能隙中间位置,因此,石墨烯-WSe2界面的肖特基势垒不能被有效消除.2016年,他们又提出了一种用掺杂TMDC材料作源漏电极,降低接触电阻的概念[132].他们利用p型掺杂的WSe2(Nb0.005W0.995Se2)作为源漏电极,h-BN作为保护层,制作的多层WSe2FET,接触电阻低至0.3 kΩ·µm,开关比大于109,饱和电流密度高达320 µA/µm.

3.4 隧穿接触

当将一层超薄绝缘层插入金属与二维TMDC之间的接触界面,便形成了金属-绝缘体-半导体(metal insulator semiconductor,MIS)结构(图8(d)),可以降低TMDC接触电阻.最初,MIS结构中的薄绝缘层使用的是MgO[133]和TiO2[134],实验结果表明插入的绝缘层可以有效降低肖特基势垒高度,但未量化研究接触电阻.2016年,斯坦福大学Wong等[135]用Ta2O5作为隧穿层,制作了CVD MoS2-Ta2O5-Ti/Au的MIS结构器件.通过对绝缘层的厚度优化分析,发现当Ta2O5为1.5 nm时,金属与CVD-MoS2接触的肖特基势垒降低至29 meV.然而,直接在无表面悬挂键的MoS2表面进行原子层沉积,通常会形成比较大的孤立岛,具有很大的界面粗糙度.同年,武汉大学廖蕾等[126]利用CVD h-BN作为隧穿绝缘层,降低肖特基势垒高度,改善金属-MoS2的接触电阻.1—2层h-BN具有原子级的超薄厚度,仅产生很小的隧穿电阻,极大地降低了肖特基势垒高度.在金属-MoS2接触界面插入超薄h-BN层后,肖特基势垒高度由原来的158 meV降低至32 meV,接触电阻从5.2 kΩ·µm降低至1.8 kΩ·µm.由于隧穿接触的优化,MoS2FET 可以在室温下具有73 cm2·V−1·s−1的场效应迁移率和330µA/µm的输出电流,在77 K温度下,迁移率和输出电流分别提高至321.4 cm2·V−1·s−1和572µA/µm.随后,2017年,哥伦比亚大学Hone等[136]制作机械剥离的单层h-BN包裹单层MoS2的三明治结构,利用金属Co作为电极,实现了低温的欧姆接触.h-BN不仅作为隧穿绝缘层降低了界面的肖特基势垒,而且调制了金属电极Co的功函数,使得接触界面的接触得到极大的改善,在20 K的低温环境下,在载流子浓度为5.3×1012/cm2接触电阻约为3 kΩ·µm,提取的肖特基势垒为16 meV.良好的接触使得他们在更低的载流子浓度下观察到了单层MoS2的SdH振荡,为研究单层MoS2的固有性质提供了不可多得的平台.

4 TMDC材料的逻辑集成器件与电路

与石墨烯相比,TMDC具有更广的可调禁带宽度,并且单层MoS2,WS2都是直接带隙半导体,因此在逻辑集成器件和光电器件领域具有巨大的应用潜力.研制基于新材料且与传统半导体产业相兼容的器件结构与工艺,就成为打破硅基器件极限的一个主要思路.本部分简单介绍TMDC逻辑集成器件方面的进展.

4.1 逻辑集成电路

逻辑电路的性能和单芯片的集成度是发展微电子学的重要指标.因此,研究TMDC在逻辑电路和器件集成方面的应用是十分有必要的.经过研究者的不断努力,基于二维TMDC的直接耦合场效应晶体管逻辑电路(direct coupled field effect transistor logic,DCFL)[41,42,137,138]和CMOS逻辑电路[139−142]已经取得一些突破.

4.1.1 DCFL逻辑电路

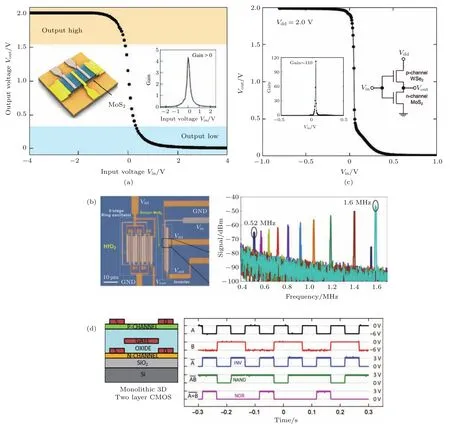

2011年,洛桑联邦理工学院Kis等[41]首次利用二维MoS2晶体管实现了反相逻辑电路.该电路由两个MoS2晶体管组成,具有良好的信号放大能力并能够实现一些基本的逻辑操作,图10(a)展示了器件的基本结构及其电压传输曲线和增益曲线.由于基于MoS2的p-MOSFET的制作工艺尚不成熟,该逻辑电路由两个基于二维MoS2的n-MOSFET组成,即所谓的DCFL电路.图10(a)的电压传输曲线显示该器件具有优秀的反相特性,此外,在±0.3 V的输入电压范围下,反相器的输出电压变化快于输入电压的变化,这表明这一逻辑电路能够用于信号的放大,这一逻辑电路的电压增益达到超过4的最大值,这保证了基于二维MoS2的逻辑门阵列构建的基本条件.

图10 基于二维MoS2逻辑器件 (a)首个MoS2的反相器逻辑电路[41];(b)基于五级MoS2反相器级联的环形振荡器[42];(c)与p型材料集成制备的基于MoS2的CMOS反相器[141];(d)三维单片异质集成的CMOS逻辑器件[143]Fig.10.Logic devices based on two-dimensional MoS2:(a)First logic inverter based on MoS2[41];(b)a fi vestage ring oscillator based on MoS2inverter[42];(c)CMOS inverter based on MoS2which is combined with p-type materials[141];(d)three-dimensional monolithic CMOS logic devices based on MoS2[143].

随后,2012年,麻省理工学院Palacios等[42]在此基础上,引入耗尽型的MoS2MOSFET作为DCFL电路的上拉有源负载.这项工作中,他们通过选择Al(功函数4.08 eV)和Pd(功函数5.12—5.60 eV)实现了阈值电压差值为0.76 V的耗尽型和增强型晶体管.与增强型晶体管相比,耗尽型晶体管具有较低的栅极开启电压,这对DCFL电路十分有效.由于引进了耗尽型的晶体管,该逻辑电路在较低的输入电压下即可完成状态翻转,确保了整个集成电路具有统一的供电电压Vdd.此外,利用输入电压和输出电压匹配这一优点,该工作进一步地将多级反相器级联,制备出了基于DCFL的五级环形振荡器,图10(b)是该环形振荡器的器件结构以及输出信号的功率谱.

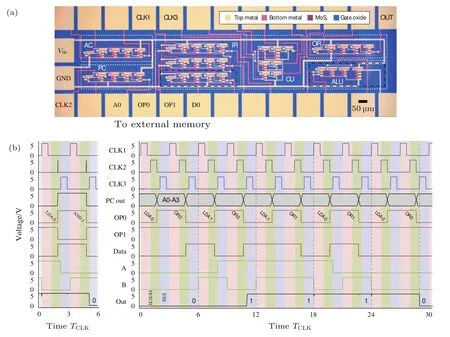

作为复杂逻辑电路的代表,近期维也纳技术大学Mueller等[43]利用MoS2实现了1位的微处理器.该处理器可以执行存储在外部存储器中的用户定义的程序,执行逻辑操作并与其周边进行通信.此外,通过适当的并联操作,这一处理器可以十分轻松地从1位设计扩展到多位结构,从而实现更加复杂的逻辑操作.该微处理器总共由115个晶体管组成,这是迄今为止由二维材料制成的最复杂的电路,图11(a)是该处理器的布局图,图11(b)给出了该微处理器的操作时序图.从时序图可以看出,这一微处理器可以有效地处理数据的读写以及运算操作.

图11 基于MoS2的微处理器[43](a)MoS2微处理器的布局设计;(b)MoS2微处理器的时序Fig.11.Microprocessor based on two-dimensional MoS2[43]:(a)Layout of MoS2microprocessor;(b)operation timing diagram of MoS2microprocessor.

4.1.2 CMOS逻辑电路

相比DCFL逻辑电路,CMOS逻辑电路的应用更为广泛,这是因为CMOS结构具有大的噪声容限以及小的静态功耗等优点.但由于MoS2,WS2等材料的p-MOSFET的制备过程尚不成熟,阻碍了其迈向逻辑集成电路的发展.因此有些研究者创新性地利用其他材料构建p-MOSFET,再与基于MoS2的n-MOSFET结合实现CMOS逻辑电路.2013年,加州大学洛杉矶分校段镶锋等[139]通过垂直堆叠MoS2/石墨烯制备出垂直结构的FET,进一步利用Bi2Sr2Co2O8(BSCO)作为p型沟道材料制备出了垂直结构的异质CMOS逻辑反相器.在这种情况下,n型MOS器件仍保持很好的开关特性,使得该电路系统具有约1.6的电压增益,显示了异质CMOS逻辑电路的潜力.2015年,韩国廷世大学Im等[140]利用MoTe2作为p型沟道材料,与MoS2的n-MOSFET构建了高性能的CMOS反相器.在该工作中,为了避免MoTe2的双极性,他们引入具有高功函数的Pt作为源漏电极金属.该反相器拥有约高达22的电压增益,同时还具有很高的噪声容限(NML≈0.35VDD,NMH≈0.39VDD).

构建具有较低供电电压的逻辑电路可以显著降低功耗,但是与此同时保证电路的高增益对于MoS2CMOS逻辑电路是一个比较大的挑战. 2016年,早稻田大学的Takenobu等[141]通过在蓝宝石衬底上结合WSe2p-MOSFET和MoS2n-MOSFET制备出了高达约110电压增益的CMOS反相器,且供电电压仅为2 V,如图10(c)所示.该反相器的噪声容限为NMH=0.42VDD以及NML=0.48VDD,十分逼近理想值(NMH=NML=0.5VDD).除了BSCO,MoTe2和WSe2之外,碳纳米管[142]、黑磷[144,145]以及其他TMDC[146,147]等也被用来与MoS2构建CMOS逻辑电路.这些方法为我们提供了思路,但由于p型材料与n型不一致,给工艺制备带来了困难.2016年,加州大学伯克利分校Hu等[143]的工作为我们引入了新的方向,他们提出了一种所谓单片三维集成的方法,将p-MOS管与n-MOS垂直叠加,这不仅解决了工艺难题,而且进一步提升了集成电路的集成度.图10(d)中展示了利用三维单片集成的方法制备的CMOS反相器逻辑电路结构.这一方法进一步打开了通向二维MoS2通向高密度、超低电压以及低功耗应用的大门.

4.2 存储电路

构建完整的集成电路系统,除了具备用于逻辑运算的功能模块外,还需要存储模块,用于数据的寄存以及存储.目前,研究者已经利用二维TMDC材料开发出各种存储电路,包括SRAM、动态随机存取存储器(dynamic random access memory,DRAM)以及非挥发性存储器.

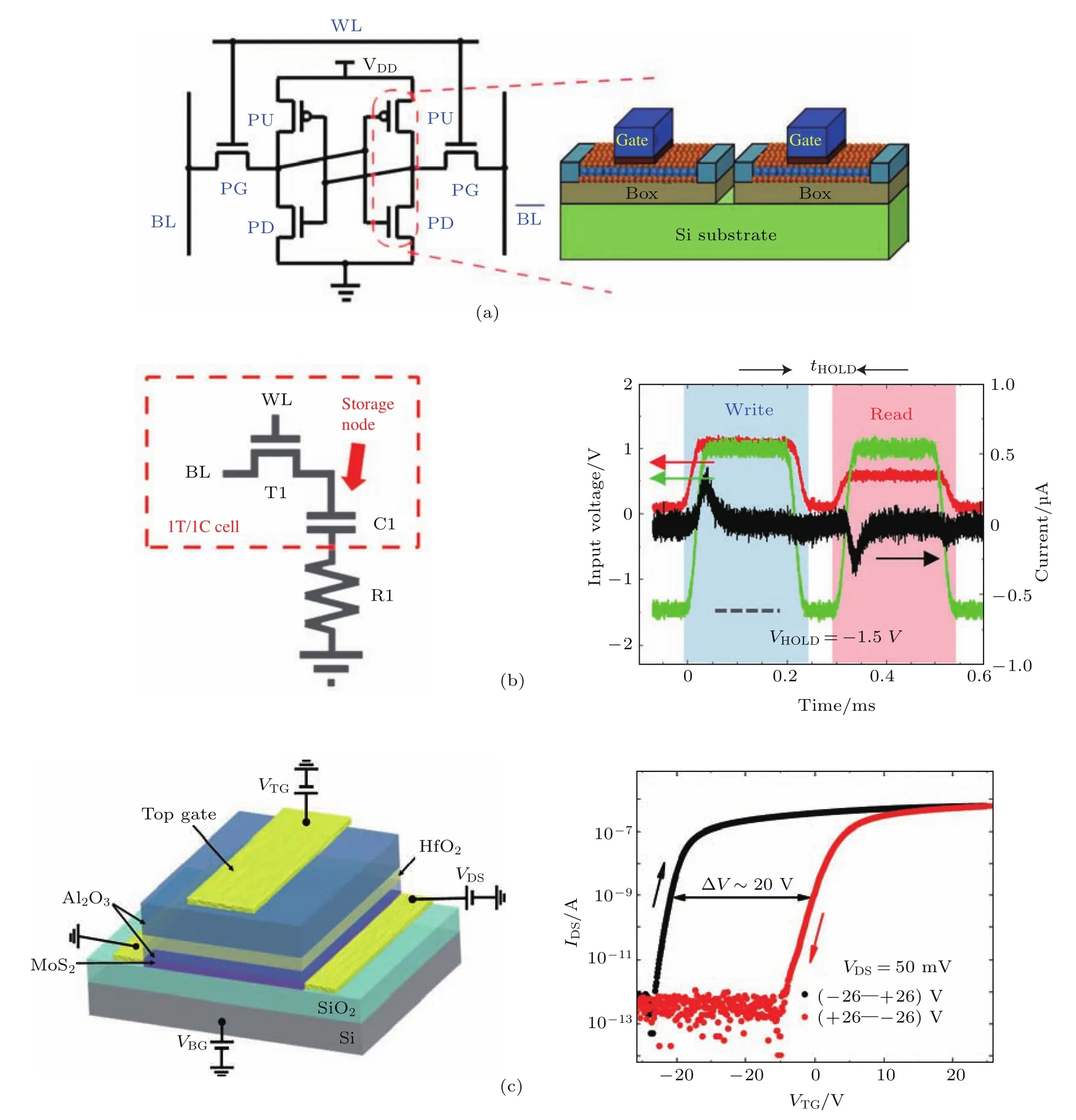

2012年,Palacios等[42]已经利用两个反相器相互驱动构建了一个简单的SRAM,但是缺少相应的字选线以及读写信号.2015年,中国台湾交通大学Chuang等[148]利用MoS2(n-MOS)和WSe2(p-MOS)构建了完整的CMOS逻辑SRAM电路,如图12(b)所示,并对这一电路进行了完整的评估.该电路工作时,表现出优异的器件静态特性以及优越的稳定性,这证明了单层TMDC材料可以很好地适用于低功耗的SRAM电路.

2016年,明尼苏达大学Koester等[149]利用MoS2成功构建了DRAM,如图12(b)所示.并以此为基础发现了MoS2MOSFET具有超低的漏电流,表明MoS2在低功耗电子领域的巨大应用潜力.他们分别构建了单晶体管/单电容DRAM以及双晶体管的DRAM,其中双晶体管的DRAM可以获得超过1 s的保持时间.

电荷陷阱存储器是典型的非易失存储器,而高κ介质由于其具有减少耦合串扰和较弱的电荷泄漏等优点,常被用作电荷陷阱层.除此之外,之前的研究证实高κ的电介质可以有效地提高MoS2的迁移率[64,78],因此陆续有利用高κ电介质制备MoS2电荷陷阱存储器的研究出现.2016年,复旦大学周鹏等[150]利用多层MoS2和Al2O3/HfO2/Al2O3电荷陷阱栅叠层制备出了双栅的电荷陷阱存储器.图12(c)是该器件结构及性能,从图中可以看出MoS2的电荷陷阱器件具有前所未有的高达约20 V的存储窗口.而且背栅的存在使得该存储窗口可以在15.6—21 V之间进行有效的调节.通过二维MoS2和传统高κ电荷陷阱存储器相结合,这项工作开辟了新的实现高性能非挥发性器件的领域.

4.3 工艺集成

前面介绍了各种基于二维TMDC材料的逻辑电路和存储电路,基本实现了数字逻辑电路所需要的电路结构.因此,如何与现行半导体工艺相结合是研究二维TMDC材料应用于逻辑集成电路的新问题.

2014年,Chen等[35]采用与CMOS相兼容的方法制备出了基于混合MoS2/Si沟道的三维FET器件,分别实现了混合MoS2和Si的Fin-FET器件以及纳米线FET器件,器件结构分别如图13(a)所示.其中,该工作通过分别利用基于Si的p-MOSFET以及基于混合Si/MoS2的n-MOSFET来实现CMOS.进一步,通过计算可以发现基于混合MoS2/Si的三维FET器件的电子迁移率主要由MoS2主导,并达到了硅的电子迁移率的两倍.而且相比于Si的Fin-FET器件,这种混合Si/MoS2沟道的Fin-FET器件,能够显著提高器件的开态电流.这极大地提升了在更小尺寸下Si晶体管的性能极限.

图12 存储器件 (a)SRAM逻辑结构(基于CMOS逻辑)[148];(b)DRAM逻辑结构、器件结构及特性[149];(c)电荷陷阱闪存器件结构及性能[150]Fig.12.Memory devices microprocessor based on two-dimensional MoS2[148]:(a)SRAM device based on MoS2;(b)DRAM device based on MoS2[149];(c)charge trap nonvolatile memory device based on MoS2[150].

随后,2015年,该团队通过在背栅上沉积氧化层(back gate oxide,BGO),后再利用与CMOS兼容的CVD方法在BGO上保形沉积多层MoS2[151].并且利用氢气等离子体对MoS2进行处理,该器件有效地降低了串联电阻,结构如图13(b)所示.利用2 nm的BGO背栅调控4 nm厚的MoS2,使得该器件在1.2 V的背栅电压下阈值电压即可产生0.5 V的偏移,从图13(b)可以看出阈值电压随着背栅电压的改变而变化.这表明可以通过BGO栅极实现对器件进行动态的配置,使其可以满足高性能或低功耗的不同需求.

如何可控地进行MoS2的CVD生长一直是限制MoS2迈向实际应用的重要因素.2016年,该团队通过在衬底上沉积多晶硅,而后刻蚀出V形沟道区域,留下部分作为源漏电极(如图13(c)左图所示)[36].之后利用多晶硅源漏电极边缘作为CVD生长MoS2的种子层,可以保证在整个晶圆片上的任意沟道区域上沉积MoS2.通过这一方法,该工作成功构建了一个U形的MOSFET器件,如图13(c)中的转移特性曲线所示.更为关键的是这一工作实现了基于MoS2的p-MOSFET器件.由于可以在整个晶圆片上制备CVD MoS2,并实现p-MOS,该工作有效地推进了MoS2与传统CMOS工艺的结合,为MoS2的最终应用奠定了有益的基础.

图13 MoS2与硅的异质集成 (a)混合Si/MoS2Fin-FET[35];(b)BGO动态配置型FET[151];(c)p型V形MoS2FET器件[36]Fig.13.Heterogeneous integration device of MoS2and Si:(a)Hybrid;(b)MoS2FET with the dynamic configuration of BGO[151];(c)V shape MoS2FET device with p-type property[36].

5 总结与展望

二维TMDC独特的电子排布和原子结构决定着其优异的电学、光学、催化等物理化学性能,在新型电子器件、能源存储以及催化反应中均展现了极高的应用潜力.当前针对二维TMDC的电子器件研究主要集中在电子输运机理、晶体管性能提高以及逻辑集成等几个方面.本文从材料的微观参数层面解读了限制载流子输运的主要散射机理以及减少抑制散射的方法;分析了金属-半导体接触对器件性能的影响,以及目前有效降低TMDC接触电阻的工艺手段;进一步从逻辑器件、存储器件到功能化微处理器等方面综述了当前TMDC逻辑集成器件以及电路的研究进展.根据最新的研究进展,二维半导体TMDC材料在微电子器件领域已经表现出超越传统硅材料的优势,比如亚10 nm沟道器件的制备[31,152−154],克服了硅材料无法逾越的短沟道效应.因此,二维TMDC材料在逻辑集成器件应用领域,仍具有十分巨大的潜力.我们认为该领域未来的研究主要方向有以下3点.

1)当前基于二维半导体TMDC晶体管的性能还不能够全面超越硅基器件.虽然在相同尺寸(厚度)下,TMDC表现出高开关比、高迁移率的优势,但其电流密度、接触电阻还存在一定的差距.探索新的材料工艺手段、结合铁电、高κ等新型介电材料的优势实现高驱动电流、低功耗的TMDC晶体管,以及实现对材料可控掺杂均是当前器件领域亟需解决的问题.

2)虽然CVD等方法可以合成大面积TMDC,但材料质量和均匀性离芯片级的要求还有很大差距,并存在工艺成本高、重复性差等问题.探索低成本、高质量、大面积的高效合成方法是推动TMDC器件应用的重要课题.

3)当前TMDC已经被证明可以硅基集成,表现出良好的硅基工艺兼容性,下一步需要降低工艺对材料和器件性能的影响、提高良率和集成度.

尽管TMDC电子器件具备传统体材料晶体管无法比拟的巨大优势,其相关研究在过去几年取得了众多进展,吸引了来自学术界以及Samsung,IBM,TSMC等众多工业界公司的关注,但目前研究大多依旧是在以高校和研究所所代表的学术界内完成的,虽然工业界对于这些新型二维材料非常关注,但是尚未投入大量的研发经费以帮助这些材料走向产业应用,主要原因之一是目前报道的器件性能距离材料本征性能以及ITRS的要求仍有一定的差距,无法满足5 nm节点以下的技术要求.中国作为全球最大的电子产品制造与消费国,近年来在全球半导体行业发展速度趋缓的大背景下,唯独中国市场保持一枝独秀,多年来市场需求使得中国半导体行业在未来很长时期内可以保持持续增长.同时,国家产业规划以及民族产业发展均显示出突破欧美韩垄断半导体核心技术的渴求,而新材料研发与应用有望成为我国半导体产业实现弯道超车的突破点.未来国家层面上研发经费投入以及学术界与产业界的产学研结合有望使得当前二维半导体器件众多悬而未决的问题得以解决,并将新型器件推广至产业应用的层面.

[1]Lange K,Muller-Seitz G,Sydow J,Windeler A 2013Res.Policy42 647

[2]Liu Q,Vinet M,Gimbert J,Loubet N 2013Electron Devices Meeting(IEDM),2013 IEEE InternationalWashington,DC,USA,December 9–11,2013 p9.2.1

[3]Mistry K,Allen C,Auth C,Beattie B 2007Electron Devices Meeting,2007.IEDM 2007.IEEE InternationalWashington,DC,USA,December 10–12,2007 p247

[4]Welser J,Hoyt J L,Takagi S,Gibbons J F 1995Electron Devices Meeting,1994.IEDM’94.Technical Digest.,InternationalSan Francisco,USA,December 11–14,1994 p373

[5]Welser J,Hoyt J L,Gibbons J F 1994IEEE Electron.Dev.Lett.15 100

[6]Radisavljevic B,Kis A 2013Nat.Mater.12 815

[7]Dennard R H,Gaensslen F H,Rideout V L,Bassous E,Leblanc A R 1974IEEE J.Solid-St.Circ.9 256

[8]Intel Enters the Third Dimension http://www.nature.com/news/2011/110506/full/news.2011.274.html[2011-5-6]

[9]ITRS2.0 http://www.itrs2.net/[2016-12-10]

[10]Castellanosgomez A 2016Nat.Photon.10 202

[11]Novoselov K S,Geim A K,Morozov S V,Jiang D,Zhang Y,Dubonos S V,Grigorieva I V,Firsov A A 2004Science306 666

[12]Li X,Wang X,Zhang L,Lee S,Dai H 2008Science319 1229

[13]Zhang Y,Tang T T,Girit C,Hao Z,Martin M C,Zettl A,Crommie M F,Shen Y R,Wang F 2009Nature459 820

[14]Elias D C,Nair R R,Mohiuddin T M,Morozov S V,Blake P,Halsall M P,Ferrari A C,Boukhvalov D W,Katsnelson M I,Geim A K,Novoselov K S 2009Science323 610

[15]Jariwala D,Sangwan V K,Lauhon L J,Marks T J,Hersam M C 2014ACS Nano8 1102

[16]Wang L,Chen Z,Dean C R,Taniguchi T,Watanabe K,Brus L E,Hone J 2012ACS Nano6 9314

[17]Lang M,He L,Xiu F,Yu X,Tang J,Wang Y,Kou X,Jiang W,Fedorov A V,Wang K L 2012ACS Nano6 295

[18]Wilson J A,Yo ff e A D 1969Adv.Phys.18 193

[19]Mak K F,He K,Shan J,Heinz T F 2012Nat.Nanotechnol.7 494

[20]Chiu M H,Zhang C,Shiu H W,Chuu C P,Chen C H,Chang C Y S,Chen C H,Chou M Y,Shih C K,Li L J 2015Nat.Commun.6 7666

[21]Liu E,Fu Y,Wang Y,Feng Y,Liu H,Wan X,Zhou W,Wang B,Shao L,Ho C H,Huang Y S,Cao Z,Wang L,Li A,Zeng J,Song F,Wang X,Shi Y,Yuan H,Hwang H Y,Cui Y,Miao F,Xing D 2015Nat.Commun.6 6991

[22]Wang Y,Liu E,Liu H,Pan Y,Zhang L,Zeng J,Fu Y,Wang M,Xu K,Huang Z,Wang Z,Lu H Z,Xing D,Wang B,Wan X,Miao F 2016Nat.Commun.7 13142

[23]Castro Neto A H 2001Phys.Rev.Lett.86 4382

[24]Schaibley J R,Yu H Y,Clark G,Rivera P,Ross J S,Seyler K L,Yao W,Xu X D 2016Nat.Rev.Mater.1 16055

[25]Liu Y,Weiss N O,Duan X D,Cheng H C,Huang Y,Duan X F 2016Nat.Rev.Mater.1 16042

[26]Radisavljevic B,Radenovic A,Brivio J,Giacometti V,Kis A 2011Nat.Nanotechnol.6 147

[27]Kuc A,Zibouche N,Heine T 2011Phys.Rev.B83 245213

[28]Xiao D,Liu G B,Feng W,Xu X,Yao W 2012Phys.Rev.Lett.108 196802

[29]Yan R H,Ourmazd A,Lee K F 1992IEEE Trans.Electron Dev.39 1704

[30]Schwierz F 2010Nat.Nanotechnol.5 487

[31]Desai S B,Madhvapathy S R,Sachid A B,Llinas J P,Wang Q,Ahn G H,Pitner G,Kim M J,Bokor J,Hu C,Wong H P,Javey A 2016Science354 99

[32]Yu Z H,Ong Z Y,Li S L,Xu J B,Zhang G,Zhang Y W,Shi Y,Wang X R 2017Adv.Funct.Mater.27 1604093

[33]Kaasbjerg K,Thygesen K S,Jacobsen K W 2012Phys.Rev.B85 115317

[34]Zhang W X,Huang Z S,Zhang W L,Li Y R 2014Nano Res.7 1731

[35]Chen M C,Lin C Y,Li K H,Li L J,Chen C H,Chuang C H,Lee M D,Chen Y J,Hou Y F,Lin C H 2014Electron Devices Meeting(IEDM),2014 IEEE InternationalSan Francisco,USA,December 15–17,2014 p33.5.1

[36]Li K S,Wu B W,Li L J,Li M Y,Cheng C C K,Hsu C L,Lin C H,Chen Y J,Chen C C,Wu C T 2016VLSI Technology,2016 IEEE Symposium onHonolulu,USA,June 14–16,2016 p1

[37]Xu X D,Yao W,Xiao D,Heinz T F 2014Nat.Phys.10 343

[38]Ye Z L,Sun D Z,Heinz T F 2017Nat.Phys.13 26

[39]Joensen P,Frindt R F,Morrison S R 1986Mater.Res.Bull.21 457

[40]Ghatak S,Pal A N,Ghosh A 2011ACS Nano5 7707

[41]Radisavljevic B,Whitwick M B,Kis A 2011ACS Nano5 9934

[42]Wang H,Yu L,Lee Y H,Shi Y,Hsu A,Chin M L,Li L J,Dubey M,Kong J,Palacios T 2012Nano Lett.12 4674

[43]Wachter S,Polyushkin D K,Bethge O,Mueller T 2017Nat.Commun.8 14948

[44]Lee Y H,Zhang X Q,Zhang W,Chang M T,Lin C T,Chang K D,Yu Y C,Wang J T,Chang C S,Li L J,Lin T W 2012Adv.Mater.24 2320

[45]Lin Y C,Zhang W,Huang J K,Liu K K,Lee Y H,Liang C T,Chu C W,Li L J 2012Nanoscale4 6637

[46]Ling X,Lee Y H,Lin Y,Fang W,Yu L,Dresselhaus M S,Kong J 2014Nano Lett.14 464

[47]Dumcenco D,Ovchinnikov D,Marinov K,Lazic P,Gibertini M,Marzari N,Lopez Sanchez O,Kung Y C,Krasnozhon D,Chen M W,Bertolazzi S,Gillet P,Fontcuberta i Morral A,Radenovic A,Kis A 2015ACS Nano9 4611

[48]Shaw J C,Zhou H L,Chen Y,Weiss N O,Liu Y,Huang Y,Duan X F 2014Nano Res.7 511

[49]Wang X,Gong Y,Shi G,Chow W L,Keyshar K,Ye G,Vajtai R,Lou J,Liu Z,Ringe E,Tay B K,Ajayan P M 2014ACS Nano8 5125

[50]van der Zande A M,Huang P Y,Chenet D A,Berkelbach T C,You Y,Lee G H,Heinz T F,Reichman D R,Muller D A,Hone J C 2013Nat.Mater.12 554

[51]Liu K K,Zhang W,Lee Y H,Lin Y C,Chang M T,Su C Y,Chang C S,Li H,Shi Y,Zhang H,Lai C S,Li L J 2012Nano Lett.12 1538

[52]Kang K,Xie S,Huang L,Han Y,Huang P Y,Mak K F,Kim C J,Muller D,Park J 2015Nature520 656

[53]Wang X,Feng H,Wu Y,Jiao L 2013J.Am.Chem.Soc.135 5304

[54]Chen W,Zhao J,Zhang J,Gu L,Yang Z,Li X,Yu H,Zhu X,Yang R,Shi D,Lin X,Guo J,Bai X,Zhang G 2015J.Am.Chem.Soc.137 15632

[55]Chen J,Zhao X,Tan S J,Xu H,Wu B,Liu B,Fu D,Fu W,Geng D,Liu Y,Liu W,Tang W,Li L,Zhou W,Sum T C,Loh K P 2017J.Am.Chem.Soc.139 1073

[56]Li S L,Tsukagoshi K,Orgiu E,Samori P 2016Chem.Soc.Rev.45 118

[57]Schmidt H,Giustiniano F,Eda G 2015Chem.Soc.Rev.44 7715

[58]Butler S Z,Hollen S M,Cao L,Cui Y,Gupta J A,Gutierrez H R,Heinz T F,Hong S S,Huang J,Ismach A F,Johnston-Halperin E,Kuno M,Plashnitsa V V,Robinson R D,Ruo ffR S,Salahuddin S,Shan J,Shi L,Spencer M G,Terrones M,Windl W,Goldberger J E 2013ACS Nano7 2898

[59]Xu Y,Cheng C,Du S,Yang J,Yu B,Luo J,Yin W,Li E,Dong S,Ye P,Duan X 2016ACS Nano10 4895

[60]Allain A,Kang J,Banerjee K,Kis A 2015Nat.Mater.14 1195

[61]Pham V P,Yeom G Y 2016Adv.Mater.28 9024

[62]Chhowalla M,Jena D,Zhang H 2016Nat.Rev.Mater.1 16052

[63]Wang Q H,Kalantar-Zadeh K,Kis A,Coleman J N,Strano M S 2012Nat.Nanotechnol.7 699

[64]Yu Z,Ong Z Y,Pan Y,Cui Y,Xin R,Shi Y,Wang B,Wu Y,Chen T,Zhang Y W,Zhang G,Wang X 2016Adv.Mater.28 547

[65]Cui Y,Xin R,Yu Z,Pan Y,Ong Z Y,Wei X,Wang J,Nan H,Ni Z,Wu Y,Chen T,Shi Y,Wang B,Zhang G,Zhang Y W,Wang X 2015Adv.Mater.27 5230

[66]Fleischauer P D,Bauer R 1987Asle Trans.30 160

[67]Salvatore G A,Munzenrieder N,Barraud C,Petti L,Zysset C,Buthe L,Ensslin K,Troster G 2013ACS Nano7 8809

[68]Moore B T,Ferry D K 1980J.Appl.Phys.51 2603

[69]Fischetti M V,Neumayer D A,Cartier E A 2001J.Appl.Phys.90 4587

[70]Veres J,Ogier S D,Leeming S W,Cupertino D C,Khaffaf S M 2003Adv.Funct.Mater.13 199

[71]Hulea I N,Fratini S,Xie H,Mulder C L,Iossad N N,Rastelli G,Ciuchi S,Morpurgo A F 2006Nat.Mater.5 982

[72]Chen J H,Jang C,Xiao S,Ishigami M,Fuhrer M S 2008Nat.Nanotechnol.3 206

[73]DaSilva A M,Zou K,Jain J K,Zhu J 2010Phys.Rev.Lett.104 236601

[74]Ando T,Fowler A B,Stern F 1982Rev.Mod.Phys.54 437

[75]Sarma S D,Adam S,Hwang E,Rossi E 2011Rev.Mod.Phys.83 407

[76]Ong Z Y,Fischetti M V 2013Phys.Rev.B88 165316

[77]Amani M,Chin M L,Birdwell A G,Oregan T P 2013Appl.Phys.Lett.102 193107

[78]Yu Z,Pan Y,Shen Y,Wang Z,Ong Z Y,Xu T,Xin R,Pan L,Wang B,Sun L,Wang J,Zhang G,Zhang Y W,Shi Y,Wang X 2014Nat.Commun.5 5290

[79]Qiu H,Xu T,Wang Z,Ren W,Nan H,Ni Z,Chen Q,Yuan S,Miao F,Song F,Long G,Shi Y,Sun L,Wang J,Wang X 2013Nat.Commun.4 2642

[80]Fuhr J D,Saul A,Sofo J O 2004Phys.Rev.Lett.92 026802

[81]Lu C P,Li G,Mao J,Wang L M,Andrei E Y 2014Nano Lett.14 4628

[82]Zhou W,Zou X,Najmaei S,Liu Z,Shi Y,Kong J,Lou J,Ajayan P M,Yakobson B I,Idrobo J C 2013Nano Lett.13 2615

[83]Moses P G,Hinnemann B,Topsøe H,Nørskov J K 2007J.Catal.248 188

[84]And J F P,Payen E 2003J.Phys.Chem.B107 4057

[85]Voiry D,Yamaguchi H,Li J,Silva R,Alves D C,Fujita T,Chen M,Asefa T,Shenoy V B,Eda G,Chhowalla M 2013Nat.Mater.12 850

[86]Karunadasa H I,Montalvo E,Sun Y J,Majda M,Long J R,Chang C J 2012Science335 698

[87]Zhu W,Low T,Lee Y H,Wang H,Farmer D B,Kong J,Xia F,Avouris P 2014Nat.Commun.5 3087

[88]Toshihiro K,Ryo Y,Kohei U 2012Self‐Assembled Monolayer(SAM)(Weinheim:Wiley‐VCH Verlag GmbH&Co.KGaA)

[89]SchreiberF 2000StructureandGrowthofSelfassembling Monolayers(Chicago:University of Chicago Press)

[90]Ulman A 1996Chem.Rev.96 1533

[91]Wang X,Xu J B,Wang C,Du J,Xie W 2011Adv.Mater.23 2464

[92]Li Y,Xu C Y,Hu P,Zhen L 2013ACS Nano7 7795

[93]Najmaei S,Zou X,Er D,Li J,Jin Z,Gao W,Zhang Q,Park S,Ge L,Lei S,Kono J,Shenoy V B,Yakobson B I,George A,Ajayan P M,Lou J 2014Nano Lett.14 1354

[94]Burson K M,Cullen W G,Adam S,Dean C R,Watanabe K,Taniguchi T,Kim P,Fuhrer M S 2013Nano Lett.13 3576

[95]Dean C R,Young A F,Meric I,Lee C,Wang L,Sorgenfrei S,Watanabe K,Taniguchi T,Kim P,Shepard K L,Hone J 2010Nat.Nanotechnol.5 722

[96]Wang L,Gao Y,Wen B,Han Z,Taniguchi T,Watanabe K,Koshino M,Hone J,Dean C R 2015Science350 1231

[97]Meric I,Dean C R,Petrone N,Wang L,Hone J,Kim P,Shepard K L 2013Proc.IEEE101 1609

[98]Shiue R J,Gao Y,Wang Y,Peng C,Robertson A D,Efetov D K,Assefa S,Koppens F H,Hone J,Englund D 2015Nano Lett.15 7288

[99]Liu Y,Wu H,Cheng H C,Yang S,Zhu E,He Q,Ding M,Li D,Guo J,Weiss N O,Huang Y,Duan X 2015Nano Lett.15 3030

[100]Chen X,Wu Z,Xu S,Wang L,Huang R,Han Y,Ye W,Xiong W,Han T,Long G,Wang Y,He Y,Cai Y,Sheng P,Wang N 2015Nat.Commun.6 6088

[101]Qiu H,Pan L J,Yao Z N,Li J J,Shi Y,Wang X R 2012Appl.Phys.Lett.100 123104

[102]Lembke D,Kis A 2012ACS Nano6 10070

[103]Sangwan V K,Arnold H N,Jariwala D,Marks T J,Lauhon L J,Hersam M C 2013Nano Lett.13 4351

[104]Cui X,Lee G H,Kim Y D,Arefe G,Huang P Y,Lee C H,Chenet D A,Zhang X,Wang L,Ye F,Pizzocchero F,Jessen B S,Watanabe K,Taniguchi T,Muller D A,Low T,Kim P,Hone J 2015Nat.Nanotechnol.10 534

[105]Das S,Chen H Y,Penumatcha A V,Appenzeller J 2013Nano Lett.13 100

[106]Popov I,Seifert G,Tománek D 2012Phys.Rev.Lett.108 156802

[107]Liu W,Kang J,Cao W,Sarkar D,Khatami Y,Jena D,Banerjee K 2013Electron Devices Meeting(IEDM),2013 IEEE InternationalWashington,DC,USA,December 9–11,2013 p19.4.1

[108]Kang J,Sarkar D,Liu W,Jena D,Banerjee K 2012Electron Devices Meeting(IEDM),2012 IEEE InternationalSan Francisco,USA,December 10–13,2012 p17.4.1

[109]Kang J H,Liu W,Sarkar D,Jena D,Banerjee K 2014Phys.Rev.X4 031005

[110]Liu W,Sarkar D,Kang J,Cao W,Banerjee K 2015ACS Nano9 7904

[111]Kang J H,Liu W,Banerjee K 2014Appl.Phys.Lett.104 093106

[112]Yang L,Majumdar K,Liu H,Du Y,Wu H,Hatzistergos M,Hung P Y,Tieckelmann R,Tsai W,Hobbs C,Ye P D 2014Nano Lett.14 6275

[113]Fang H,Chuang S,Chang T C,Takei K,Takahashi T,Javey A 2012Nano Lett.12 3788

[114]Fang H,Tosun M,Seol G,Chang T C,Takei K,Guo J,Javey A 2013Nano Lett.13 1991

[115]Du Y,Liu H,Neal A T,Si M,Peide D Y 2013IEEE Electron.Dev.Lett.34 1328

[116]Zhao P,Kiriya D,Azcatl A,Zhang C,Tosun M,Liu Y S,Hettick M,Kang J S,McDonnell S,Santosh K C,Guo J,Cho K,Wallace R M,Javey A 2014ACS Nano8 10808

[117]Kiriya D,Tosun M,Zhao P,Kang J S,Javey A 2014J.Am.Chem.Soc.136 7853

[118]Rai A,Valsaraj A,Movva H C,Roy A,Ghosh R,Sonde S,Kang S,Chang J,Trivedi T,Dey R,Guchhait S,Larentis S,Register L F,Tutuc E,Banerjee S K 2015Nano Lett.15 4329

[119]Mcclellan C J,Yalon E,Smithe K K H,Suryavanshi S V,Pop E 2017Device Research Conference(DRC),2017 75th AnnualSouth Bend,USA,June 25–28,2017 p1

[120]Liu H,Si M,Deng Y,Neal A T,Du Y,Najmaei S,Ajayan P M,Lou J,Ye P D 2014ACS Nano8 1031

[121]Baugher B W,Churchill H O,Yang Y,Jarillo-Herrero P 2013Nano Lett.13 4212

[122]Guo Y,Han Y,Li J,Xiang A,Wei X,Gao S,Chen Q 2014ACS Nano8 7771

[123]Kappera R,Voiry D,Yalcin S E,Branch B,Gupta G,Mohite A D,Chhowalla M 2014Nat.Mater.13 1128

[124]Li S L,Komatsu K,Nakaharai S,Lin Y F,Yamamoto M,Duan X,Tsukagoshi K 2014ACS Nano8 12836

[125]English C D,Shine G,Dorgan V E,Saraswat K C,Pop E 2016Nano Lett.16 3824

[126]Wang J,Yao Q,Huang C W,Zou X,Liao L,Chen S,Fan Z,Zhang K,Wu W,Xiao X,Jiang C,Wu W W 2016Adv.Mater.28 8302

[127]Kappera R,Voiry D,Yalcin S E,Jen W,Acerce M,Torrel S,Branch B,Lei S D,Chen W B,Najmaei S,Lou J,Ajayan P M,Gupta G,Mohite A D,Chhowalla M 2014APL Mater.2 092516

[128]Lee G H,Cui X,Kim Y D,Arefe G,Zhang X,Lee C H,Ye F,Watanabe K,Taniguchi T,Kim P,Hone J 2015ACS Nano9 7019

[129]Leong W S,Luo X,Li Y,Khoo K H,Quek S Y,Thong J T 2015ACS Nano9 869

[130]Stokbro K,Engelund M,Blom A 2012Phys.Rev.B85 165442

[131]Chuang H J,Tan X,Ghimire N J,Perera M M,Chamlagain B,Cheng M M,Yan J,Mandrus D,Tomanek D,Zhou Z 2014Nano Lett.14 3594

[132]Chuang H J,Chamlagain B,Koehler M,Perera M M,Yan J,Mandrus D,Tomanek D,Zhou Z 2016Nano Lett.16 1896

[133]Dankert A,Langouche L,Kamalakar M V,Dash S P 2014ACS Nano8 476

[134]Chen J R,Odenthal P M,Swartz A G,Floyd G C,Wen H,Luo K Y,Kawakami R K 2013Nano Lett.13 3106

[135]Lee S,Tang A,Aloni S,Wong H S 2016Nano Lett.16 276

[136]Cui X,Shih E M,Jauregui L A,Chae S H,Kim Y D,Li B,Seo D,Pistunova K,Yin J,Park J H,Choi H J,Lee Y H,Watanabe K,Taniguchi T,Kim P,Dean C R,Hone J C 2017Nano Lett.17 4781

[137]Yu L,Lee Y H,Ling X,Santos E J,Shin Y C,Lin Y,Dubey M,Kaxiras E,Kong J,Wang H,Palacios T 2014Nano Lett.14 3055

[138]Amani M,Burke R A,Proie R M,Dubey M 2015Nanotechnology26 115202

[139]Yu W J,Li Z,Zhou H,Chen Y,Wang Y,Huang Y,Duan X 2013Nat.Mater.12 246

[140]Pezeshki A,Hosseini Shokouh S H,Jeon P J,Shackery I,Kim J S,Oh I K,Jun S C,Kim H,Im S 2016ACS Nano10 1118

[141]Pu J,Funahashi K,Chen C H,Li M Y,Li L J,Takenobu T 2016Adv.Mater.28 4111

[142]Huang J,Somu S,Busnaina A 2012Nanotechnology23 335203

[143]Sachid A B,Tosun M,Desai S B,Hsu C Y,Lien D H,Madhvapathy S R,Chen Y Z,Hettick M,Kang J S,Zeng Y,He J H,Chang E Y,Chueh Y L,Javey A,Hu C 2016Adv.Mater.28 2547

[144]Liu H,Neal A T,Zhu Z,Luo Z,Xu X,Tomanek D,Ye P D 2014ACS Nano8 4033

[145]Su Y,Kshirsagar C U,Robbins M C,Haratipour N,Koester S J 20162d Mater.3 011006

[146]Jeon P J,Kim J S,Lim J Y,Cho Y,Pezeshki A,Lee H S,Yu S,Min S W,Im S 2015ACS Appl.Mater.Inter.7 22333

[147]Cho A J,Park K C,Kwon J Y 2015Nanoscale Res.Lett.10 115

[148]Yu C H,Fan M L,Yu K C,Hu V P H,Su P,Chuang C T 2016IEEE Trans.Electron Dev.63 625

[149]Kshirsagar C U,Xu W,Su Y,Robbins M C,Kim C H,Koester S J 2016ACS Nano10 8457

[150]Zhang E,Wang W,Zhang C,Jin Y,Zhu G,Sun Q,Zhang D W,Zhou P,Xiu F 2015ACS Nano9 612

[151]Chen M C,Li K S,Li L J,Lu A Y,Li M Y,Chang Y H,Lin C H,Chen Y J,Hou Y F,Chen C C 2015Electron Devices Meeting(IEDM),2015 IEEE InternationalWashington,DC,USA,December 7–9,2015 p32.2.1

[152]Xu K,Chen D,Yang F,Wang Z,Yin L,Wang F,Cheng R,Liu K,Xiong J,Liu Q,He J 2017Nano Lett.17 1065

[153]Nourbakhsh A,Zubair A,Sajjad R N,Tavakkoli K G A,Chen W,Fang S,Ling X,Kong J,Dresselhaus M S,Kaxiras E,Berggren K K,Antoniadis D,Palacios T 2016Nano Lett.16 7798

[154]Xie L,Liao M,Wang S,Yu H,Du L,Tang J,Zhao J,Zhang J,Chen P,Lu X,Wang G,Xie G,Yang R,Shi D,Zhang G 2017Adv.Mater.2017 1702522

PACS:85.35.–p,73.40.Cg,85.30.Tv,78.40.Fy DOI:10.7498/aps.66.218503

*Project support by the National Natural Science Foundation of China(Grant Nos.61325020,61521001)and the National Basic Research Program of China(Grant Nos.2013CBA01604,2015CB351900).

†Corresponding author.E-mail:xrwang@nju.edu.cn

Logical integration device for two-dimensional semiconductor transition metal sul fi de∗

Li Wei-Sheng Zhou Jian Wang Han-Chen Wang Shu-Xian Yu Zhi-Hao Li Song-Lin Shi YiWang Xin-Ran†

(National Laboratory of Solid State Microstructures,Collaborative Innovation Center of Advanced Microstructures,School of Electronic Science and Engineering,Nanjing University,Nanjing 210093,China)

d 11 September 2017;revised manuscript

3 October 2017)

The semiconductor industry has experienced exponential growth for more than 50 years,following the Moore’s Law.However,traditional microelectronic devices are currently facing challenges such as high energy consumption and the short-channel effect.As an alternative,two-dimensional layered materials show the ability to restrain the carriers in a 1 nm physical limit,and demonstrate high electron mobility,mutable bandgap,and topological singularity,which will hopefully give birth to revolutionary changes in electronics.The transition metal dichalcogenide(TMDC)is regarded as a prospective candidate,since it has a large bandgap(typically about 1–2 eV for a monolayer)and excellent manufacture compatibility.Here in this paper,we review the most recent progress of two-dimensional TMDC and achievements in logic integration,especially focusing on the following key aspects:charge transport,carrier mobility,contact resistance and integration.We also point out the emerging directions for further research and development.

transition metal dichalcogenides, field-effect transistors,mobility,logic integration

微电子器件沿摩尔定律持续发展超过50年,正面临着高功耗等挑战.二维层状材料可以将载流子限制在界面1 nm的空间内,部分材料展现出高迁移率、能带可调、拓扑奇异性等特点,有望给“后摩尔时代”微电子器件带来新的技术变革.其中,以MoS2为代表的过渡金属硫化物具有1—2 eV的带隙、良好的空气稳定性和工艺兼容性,在逻辑集成方面有巨大潜力.本文综述了二维过渡金属硫化物在逻辑器件领域的研究进展,重点讨论电子输运机理、迁移率、接触电阻等关键问题及集成技术的现状,并为今后的发展指出了方向.

10.7498/aps.66.218503

∗国家自然科学基金(批准号:61325020,61521001)和国家重点基础研究发展计划(批准号:2013CBA01604,2015CB351900)资助的课题.

†通信作者.E-mail:xrwang@nju.edu.cn

©2017中国物理学会Chinese Physical Society