一种可堆叠存储介质的设计

2017-09-12韩东泽张起贵

韩东泽,张 刚,张起贵

(太原理工大学信息工程学院,太原 030024)

一种可堆叠存储介质的设计

韩东泽,张 刚,张起贵

(太原理工大学信息工程学院,太原 030024)

参考服务器/客户端的可堆叠通信模式,以最常见的SATA硬盘作为存储介质,Marvell 88SM9705为核心控制芯片,设计了一种可堆叠的存储介质。经测试,88SM9705通过解析主机端发送来的SATA 3.0协议定义的帧信息结构(Frame Information Structure,FIS)中PM Port地址字段,能依次对其所连接的多个SATA硬盘进行正确的读、写等操作,实现了存储设备的可堆叠,稳定性能良好。是一种实现扩容同步提速的可堆叠存储阵列解决方案,在嵌入式存储系统领域具有很好的应用前景。

可堆叠存储介质,SATA 3.0协议,Marvell 88SM9705,嵌入式存储系统

0 引言

随着互联网的发展,每天海量数据的产生使得人们对存储器的容量和访问速度有越来越高的要求[1],而仅仅依靠提升时钟频率来提速的空间已经处于研究的瓶颈,有必要设计一种新的体系结构来满足上述需求。本文借助于端口倍增器(Port Multiplier,PM),将多个廉价的硬盘组织起来形成了一种可堆叠的存储介质架构,并在FPGA上进行了验证。Marvell 88SM9705是一款具体实现可堆叠存储介质的物理层芯片,可对连接到其上的SATA硬盘按照主机端分配的地址实现对多个硬盘的访问[2],为可堆叠存储介质的设计提供了良好的解决方案。

1 可堆叠控制芯片PM简介

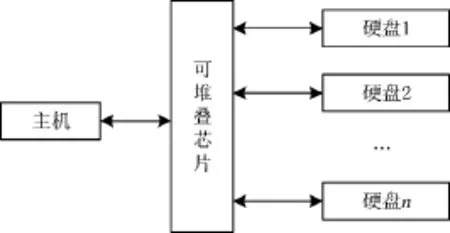

PM可以看成是一款允许活动的主机端与多个设备端通信的多路复用器。目前PM可以扩展设计到支持多达15路的设备端。88SM9705能够识别SATA自定义的OOB序列和速度协商序列,可以根据主机端发送来的FIS中的PM Port地址字段访问所连接的多个SATA硬盘,支持的通信速度最高达到6.0 Gb/s[2],是本设计所选用的核心芯片。下页图1为可堆叠存储介质连接示意图。

图1 可堆叠存储介质总体连接示意图

2 可堆叠原理

网络中,通过为服务器和客户端分配不同的IP地址,使相同服务器和客户端被区分开[3]。当服务器要向某个客户端发送消息时,在消息中会加入该客户端的IP地址,客户端收到消息,解析提取地址并与自己的地址比较,如果地址匹配,则接收消息并进行相应的操作,否则放弃该消息[4],这种通信结构即为可堆叠。由此可见,要想实现可堆叠,被访问目标设备必须具有自主访问功能和拥有独立的地址。

2.1 自主访问

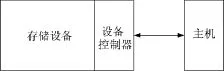

SATA硬盘是在ATA硬盘基础上加以改进,把控制器放在了设备端,当主机访问这种设备时,将命令和数据封装成消息,设备端的SATA控制器收到消息后,解析消息,提取命令和数据,完成了硬盘的自主访问。图2为具有自主访问功能的SATA设备结构图。

图2 SATA自主访问存储结构

2.2 可堆叠

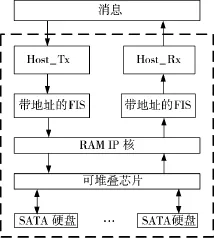

由于SATA硬盘本身是没有带地址的,所以还不是可堆叠的存储设备。要想实现可堆叠,正如服务器客户端模式一样,必须为能自主访问的SATA硬盘分配地址。当主机在访问多个设备时,在FIS消息中加入设备地址,设备端控制器通过提取地址来判断是否对该设备进行操作。而目前这一功能的实现,需要借助第三方芯片来区分每一个硬盘设备。具体的内部通讯如图3所示。

接收到数据后,主机在封装FIS消息的同时,在消息中加入设备的地址信息,之后控制芯片解析消息提取地址,根据地址把消息发送到相应的硬盘,这样做的好处是对内就形成了一个可堆叠架构[5],对外只有一个接口,形成一个大容量的存储设备。

图3 可堆叠存储介质内部通讯图

3 可堆叠存储介质设计

3.1 总体设计

本设计选用Xilinx公司的Virtex-5开发平台作为主机端,Marvell公司的88SM9705的PM芯片作为可堆叠芯片,两路SATA硬盘组与9705连接作为设备端,在具体的通信过程中,Virtex-5给9705发送SATA3.0定义的帧信息结构FIS,通过更改FIS的PM Port字段成对设备地址的分配[6]。图4为利用9705芯片设计的可堆叠存储介质实物图。

图4 用9705设计的可堆叠存储介质连接实物图

3.2 可堆叠芯片初始化

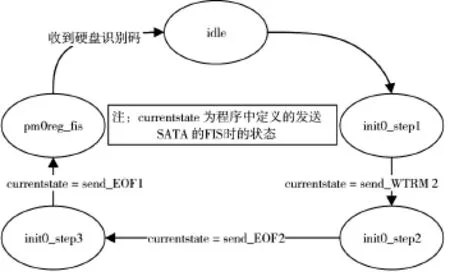

88SM9705芯片在正式投入使用之前必须对其各个端口进行初始化。若初始化成功,芯片端口对应指示灯会亮起,否则初始化失败。具体初始化的方法在生产芯片时早已设定好,本文主要工作为编写相应的状态机,通过FPGA给其发送激活FIS即可。下页图5为端口0的具体激活状态转移图,其他端口类似。

各个状态含义如下:

idle:空闲状态;

init0_step1:将9705上端口0的SCR2寄存器接到芯片上的相同的SATA设备分配地址将它们加以区分,之后在激活可堆叠芯片的基础上,通过状态机程序对指定的多个SATA硬盘访问,完成数据的读写。

图5 可堆叠芯片初始化端口0状态转移图

3.3.1 主机地址的分配

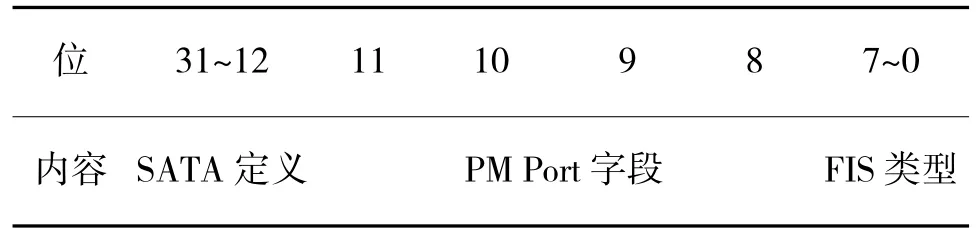

主机要想给任意一个连接到可堆叠芯片上的SATA设备发送消息,就必须要给发送的消息加上设备地址。为此PM Port字段已被添加到所有SATA3.0 FIS的第一个双字中,如表1。这些位在此前被定义为保留位,引进可堆叠芯片PM之后经过检测和初始化,主机端就可以改变PM Port字段的值来访问连接到PM上的设备,实现了对这些设备地址的分配管理。

表1 PM Port在FIS中的位置

PM Port字段占用了SATA3.0 FIS中的4位。若FIS是由主机端传输到设备端,该字段由主机填写,若FIS是由设备端传至主机端,该字段由PM填写。

3.3.2 主机对多个SATA设备写状态机的设计

主机在写每个SATA设备之前必须给设备发送写命令FIS,设备在收到写命令后会回复DMA模式的第0位置1;

init0_step2:将9705上端口0的SCR2寄存器的第0位置0;

init0_step3:将9705上端口0的SCR2寄存器的第X位清除;

pm0reg_fis:发送端口设备识别命令,验证端口0是否被初始化激活。

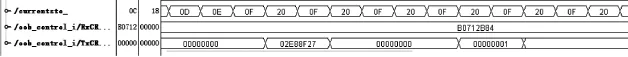

图6表示激活端口0时Chipscope抓取到的结果。

图6 激活端口0

3.3 可堆叠存储介质访问的设计

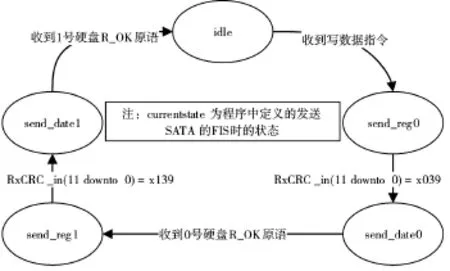

可堆叠存储介质结构设计的核心思想为给连激活FIS,请求与主机建立DMA通信,建立成功后主机才会发送数据FIS。本次设计的状态机实现的功能为将两个扇区连续的写入两个不同硬盘的相同位置,如图7所示。

各个状态含义如下:

idle:空闲状态;

send_reg0:给设备0发送写数据FIS;

send_date0:给设备0发送写数据FIS;

send_reg1:给设备1发送写数据FIS;

send_date1:给设备1发送写数据FIS;

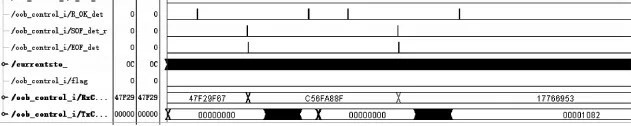

图8为按照图7的状态转移图编写的VHDL程序在chipscope中抓取到的执行结果,从图中可以看出每给一个硬盘写完一个扇区,该硬盘就会返回一个R_OK原语表示写入数据成功。

图7 连续写两个扇区到不同硬盘状态转移图

图8 连续写两个扇区到不同硬盘

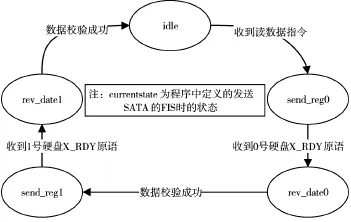

3.3.3 主机对多个SATA设备读状态机的设计

主机复位后处于空闲状态,当接收到读数据命令后,发送读设备0的命令FIS,收到X_RDY原语后,转到下一个状态,准备接收设备发送来的数据,接收完数据校验无误后,发送读取设备1的FIS开始对设备1进行读操作,过程与读设备0类似。本次设计的状态机实现的功能为将写入设备两个扇区读取出来,从而验证状态机程序的正确性。状态转移图如图9所示。

图9 连续写两个扇区到不同硬盘状态转移图

各状态含义如下:

idle:空闲

send_reg0:给设备0发送读数据FIS;

rev_date0:接收设备 0发送来数据 FIS;send_reg1:给设备1发送读数据FIS;

rev_date1:接收设备1发送来数据FIS;

4 结果与讨论

经过ISE综合工具Synthesize,得到系统的最高时钟频率[8]为207.245 MHz,连续发送两个扇区需要1 156个时钟。经计算过可得,传送两个扇区的数据需要5.58 ns,即传输速度可达到183.5 MB/s。本此设计的可堆叠存储介质只是可堆叠存储阵列的一个通道,而在阵列中,各个通道并行工作互不干扰。以此推算,阵列上的通道数越多,传输速度也将会大幅度增加,可以满足更高存储速度的要求。

5 结论

本文参考服务器客户端的通信模式,设计了一种可堆叠存储介质,可以作为廉价的高速大容量存储设备设计的解决方案,为进一步挖掘SATA 3.0协议的PM功能奠定了基础,同时也是设计高速、大容量可堆叠存储阵列的前期准备,具有良好的嵌入式应用前景。

[1]张杰.一种高速数据存储方法的研究[D].合肥:中国科学技术大学,2013.

[2]郭燕妮,何杰,张刚.基于FPGA的C/S模式网络硬盘设计与实现[J].电子技术应用,2014,40(12):30-32,39.

[3]戴宁.基于TCP/IP协议的网络通信服务器设计[D].西安:西安电子科技大学,2014.

[4]张刚,张博,张陌.ASIC的片内云架构和基于该架构的设计方法:中国,201310074630[P].2013-09-01.

[5]JOSE S.Virtex-5 FPGA rocket IO GTP transceiver user guide[R].Xilinx Coporation,2008.

[6]何宾.Xilinx FPGA设计权威指南[M].北京:清华大学出版社,2014.

A Design of Stackable Storage Medium

HAN Dong-ze,ZHANG Gang,ZHANG Qi-gui

(School of Information Engineering,Taiyuan University of Technology,Taiyuan 030024,China)

Referring to the communication model of server and client,the paper designs a stackable storage medium using the 88SM9705 chip of Marvell with the general SATA hard disks as the storage medium.The test results indicate that 88SM9705 chip could recognize the PM Port address field of Frame Information Structure(FIS)defined in the SATA 3.0 protocol,and read and write SATA hard disks connected with the chip.Completing the stackable storage device,and it has good stability,which is a solution of capacity expansion with speed increase to the stackable storage array.There is a better application prospect of embedded storage systems filed.

stackable storage medium,SATA 3.0 protocol,marvell 88SM9705,embedded storage systems

TP333.2

A

10.3969/j.issn.1002-0640.2017.08.030

1002-0640(2017)08-0132-04

2016-06-19

2016-08-12

韩东泽(1990- ),男,山西阳泉人,硕士研究生。研究方向:嵌入式系统的设计。