基于FPGA的傅里叶变换成像光谱仪实时数据采集与显示系统设计*

2017-09-06王具民殷世民陈洪波高丽伟陈真诚

王具民,殷世民,陈洪波,高丽伟,陈真诚

(桂林电子科技大学生命与环境科学学院,广西桂林541004)

基于FPGA的傅里叶变换成像光谱仪实时数据采集与显示系统设计*

王具民,殷世民,陈洪波,高丽伟,陈真诚*

(桂林电子科技大学生命与环境科学学院,广西桂林541004)

利用可见光相机模拟干涉仪,基于FPGA设计了傅里叶变换成像光谱仪实时数据采集与显示系统,为后续的实时光谱复原奠定了良好的技术基础。该系统主要由采集、存储、数据变换及显示4个部分组成,主要涉及SAA7113、ILI9325等芯片的配置、SDRAM控制器的设计、像素的提取、色彩空间的变换等。经71 ms初始化完成后,各部分协调运行,能够实时输出目标的图像信息,具有运算速度快,便于升级维护,可进行二次开发等优点。

FPGA;成像光谱仪;傅里叶变换;实时;数据采集与显示

随着现代电子技术的飞速发展,基于傅里叶变换成像光谱仪对目标的实时探测与识别已成为目前光谱仪研究领域的热点之一,而实时光谱复原技术是有效解决该问题的关键。

傅里叶变换成像光谱仪[1]利用干涉仪获得目标的干涉图,然后对干涉图的每一行进行傅里叶变换得到该行所对应的目标点的光谱信息[2]。干涉仪系统是精密的光学仪器,价格高昂,实际工程应用中,一般采用可见光相机来模拟干涉仪系统,具体做法为利用图像处理系统采集一帧可见光图像,然后对可见光图像的每一行数据进行傅里叶变换来模拟光谱复原的过程。

干涉图采集是傅里叶变换成像光谱仪实时光谱复原系统的前端部分,是后续进行实时光谱复原的关键。

成像光谱仪帧频高、信息量大,其光谱复原实时处理系统通常是以Fourier变换专用芯片或高速DSP器件为核心[2],但这种系统体积大,算法复杂,硬件处理电路升级困难,不便于移植和推广;而FPGA以其效率高、成本低、可重构性强等优势,在视频图像处理领域中扮演着越来越重要的角色。

基于以上分析,本文将可见光相机的输出作为输入图像信号,设计并实现了一种基于FPGA的干涉图采集、存储与显示系统。采集由SAA7113芯片完成,其作用是把AI11路模拟输入的视频信号解码成标准的“VPO”形式的数字信号;存储由Verilog HDL实现的SDRAM控制器将采集的图像数据存到片外的SDRAM中;数据转换部分主要涉及到各芯片配置、具有高低速率匹配、像素分离、色彩空间变换等功能;图像显示部分由ILI9325芯片驱动的彩色触摸屏来实现。系统能够实时采集、存储并显示目标的图像信息,为后续进行光谱复原奠定了良好的硬件基础。

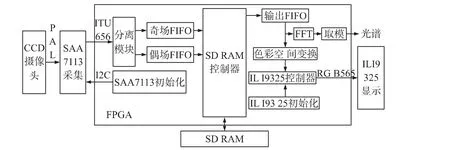

1 系统的总体设计

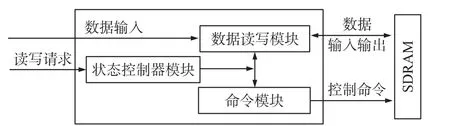

系统的硬件结构主要由视频采集模块、存储模块、图像变换模块和显示模块4个部分组成,如图1所示。采集部分主要是由CCD摄像头采集的PAL制式的电视视频信号经过解码芯片SAA7113的处理输出ITU656,YUV4∶2∶2格式的数字视频,经分离模块作用分奇偶两场存储并最后交付SDRAM存储。FPGA完成对SAA7113、SDRAM、ILI9325的初始化并按色彩空间变换公式把输出FIFO中的数据转换成RGB5∶6∶5格式,用ILI9325显示出来。虚线框中为光谱复原过程,是后续要做的工作。

图1 采集与显示系统框图

2 系统各功能模块设计

2.1 图像采集模块设计

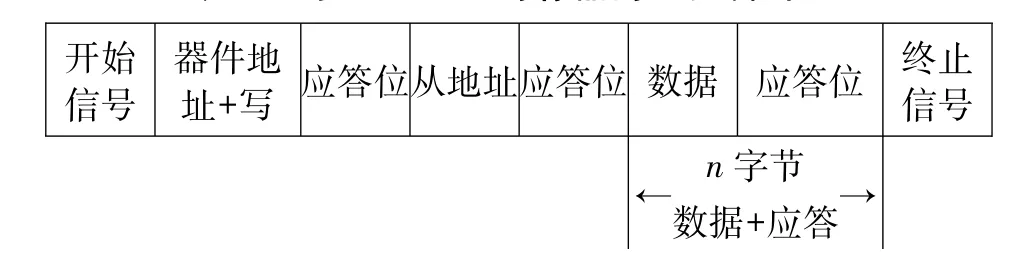

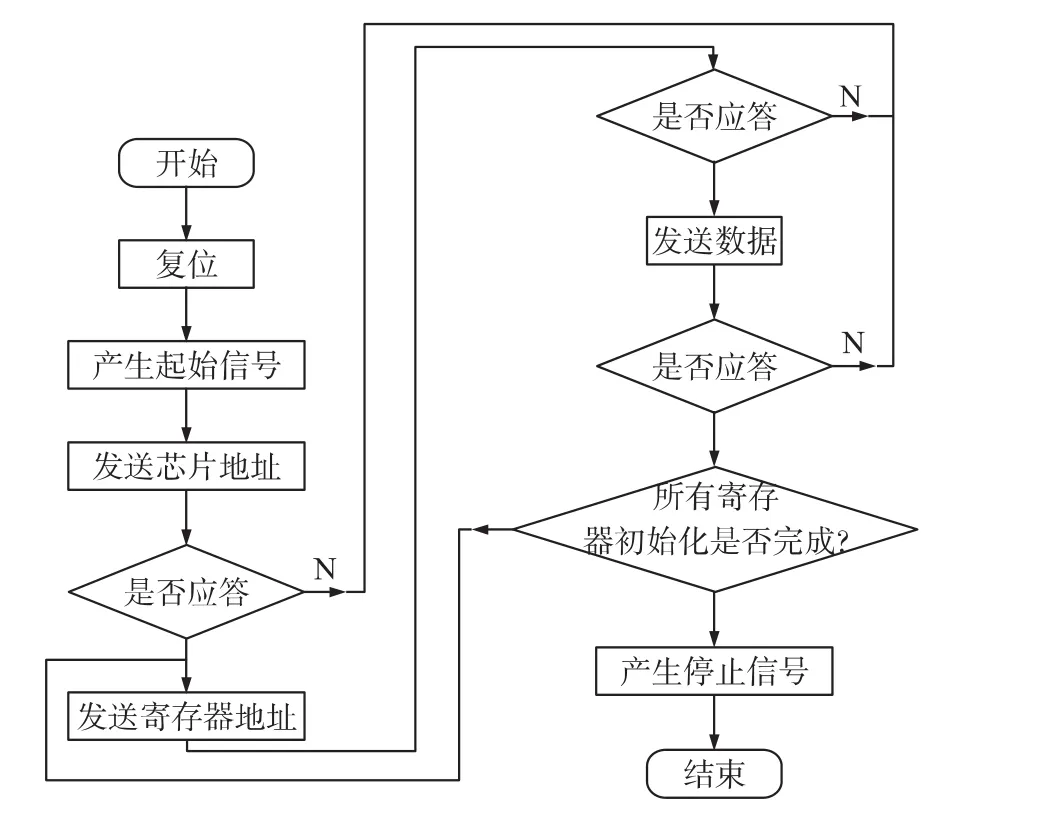

采集模块设计关键是SAA7113芯片的初始化,而初始化是FPGA通过I2C总线对其寄存器进行写操作来完成[3-4]。其写操作格式如表1所示。

表1 对SAA7113寄存器的“写”操作[5]

开始信号发出后,先发送SAA7113的芯片地址,原理图中RTS0引脚没通过3.3 kΩ电阻接地,所以其芯片地址+写标志=8'b0100_1010;如应答再发送所要配置的寄存器地址,最后发送配置数据。应答位为SAA7113在接收到8 bit数据后,在第9个时钟周期,拉低SDA线产生的回应信号;从地址为寄存器地址。

本文采用模块化编程思想,顺序执行各任务模块;开始信号、发送芯片地址、发送寄存器地址、发送数据及终止信号均封装成一个一个的任务模块;每次执行一个任务模块时,均启动一个计数器,计数器达到一定值清零,程序转去执行下一个任务。以上操作中,在需要应答的地方,无论哪一任务模块无应答,均执行复位操作,重新初始化,直到全部寄存器初始化完毕。流程图如图2所示。

图2 SAA7113初始化流程图

数据传输时,采用大端模式以位bit为单位进行,即一个字节,最高位(MSB)优先传输,每个字节后必须跟一个响应位,即一帧数据共有9 bit。发送到SDA线上的每个字节必须是8 bit的,但每次传输可以发送的字节数量不受限制。

2.2 图像存储模块设计

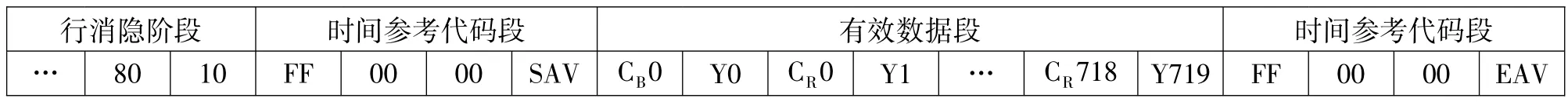

CCD摄像机输出PAL制式的电视视频信号的信息量大,需要海量数据的暂时存储[6]。本文采用开发板内嵌的K4S281632O-LC75来存储。其控制器框图如图3所示。

图3 SDRAM控制器设计框图

状态控制器模块在上电后发出初始化命令编码,SDRAM进入初始化阶段,经200μs延迟得到稳定的电压和时钟后,预充电所有逻辑BANK,并进行8次刷新操作,然后设置模式寄存器。至此初始化操作完毕,接着状态控制器进行阻塞模式,等待读写请求的到来。读写时都要先激活行,在时钟上升沿由A0~A11确定行地址,经tRCD延迟,由A0~A9和A11给出列地址,至此就达到了读写具体存储单元的目的[7]。但在读时,要经过CAS潜伏期[8],第1笔有效数据才出现在数据总线上,写入数据时则没有潜伏期。无论是读,还是写,之后都要预充电,因为即使是没有访问过的存储体也会因行选通而使存储电容受到影响。此模块每隔60 ms发送一次刷新给命令模块来完成定时刷新[9],有预充电还有刷新的原因是预充电是不定期对一个或所有逻辑Bank中的工作行的操作,而刷新则是定时依次对所有逻辑Bank中的所有行进行的操作。

数据读写模块及命令模块根据接收到的状态码解码成相应的命令来控制SDRAM。数据读写模块是数据传输通道,负责数据的存与取。SDRAM的时序很复杂,要严格按照时序来操作。命令模块负责状态译码并向SDRAM发送相应的控制命令。具体控制命令由一些专用控制引脚CS,RAS,CAS和WR和地址线辅助完成。

SDRAM虽然支持数据猝发传输方式[10],但最多一次只能存储一行(只取512个点)的数据,且输入的干涉图数据是隔行扫描得到的,存储时将奇场视频数据存储到SDRAM偶行地址中,偶场视频数据存储到奇行地址中,进行快速傅里叶变换时,逐行取出进行变换即可。

2.3 图像变换模块设计

2.3.1 输出的数据格式与分离

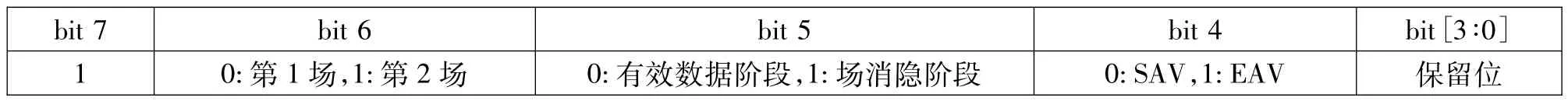

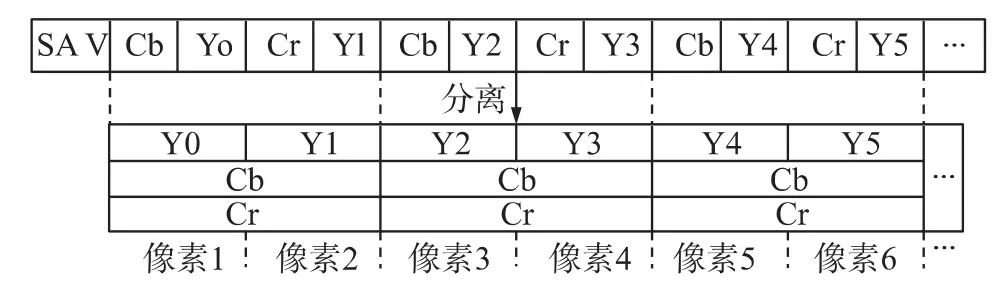

SAA7113输出ITU.656 YUV 4∶2∶2格式的视频信号,格式如表2所示,其亮度Y和色差Cb、Cr的比例为4∶2∶2。这是由于亮度和色差采用不同的采样速率导致的。在每个LLC上升沿输出一个字节的解码数据,每个像素需要两个LLC周期且都有自己的亮度数据Y,但是输出的数据中每两个相邻的像素共用一组色差数据Cb、Cr,输出时钟27 MHz。

实验中,我们只取512×512个点,奇场256行(27~282),偶场256行(340~595)。其中EAV和SAV是时间参考信号,其格式如表3所示。

表2 ITU 656 YUV 4∶2∶2标准数字电视信号

表3 SAV和EAV的数据格式

实验中,以80 h为第1场开始,9dh为第1场结束,c7h为第2场开始,dah为第2场结束。

图4为奇偶场中单行数据的分离过程[11]。

图4 奇、偶场中单行数据分离过程

2.3.2 色彩空间变换

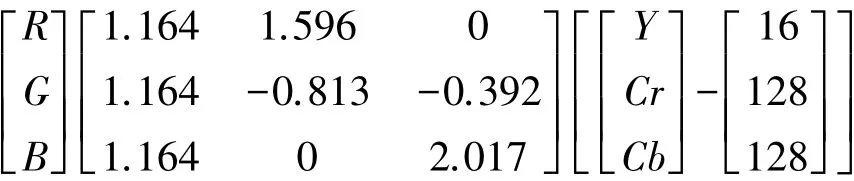

而要用LCD显示,就需要进行色彩空间变换,即将ITU.656格式的数字视频信号转换为RGB5∶6∶5的信号,因此需要分离出亮度,色差,并进行转换。其转换公式为:

由公式可知,转换需要进行浮点运算,而本设计用到的FPGA芯片一般不支持浮点运算,但使用FPGA进行定点运算比较容易,所以必须对系数进行适当放大[11]。公式可改写为:

最终的运算结果再右移10 bit即可。对于转换后的RGB值进行检查,如果大于255,将其赋值为255;如果小于0,则赋值为0。

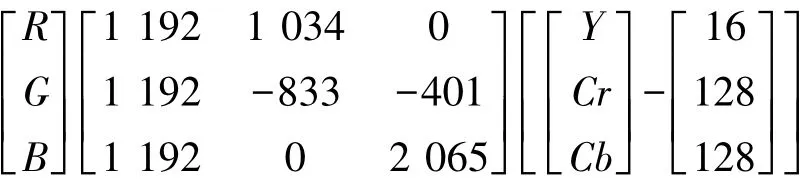

2.4 图像显示模块设计

显示选用的是ILI9325芯片控制的2.4 inch TFT彩色触摸液晶屏。ILI9325控制器设计框图,如图5所示。ILI9325支持8、9、16、18 bit并行和SPI串行共5种数据传输方式。传输方式由引脚IM[3:0]的高低电平决定。本文采用的是8 bit数据传输模式,此时IM=4'b0011,所用引脚为DB10~DB17。输入的数据仍为16 bit,分两次发送,先发送高8 bit,再发送低8 bit。

图5 ILI9325控制器设计

分频模块为各模块提供5 MHz的时钟;为了数据可靠的写入与读出,有必要降低时钟频率。

初始化模块根据实际需要配置ILI9325的寄存器以确定其显示方向,灰度与像素的关系,工作模式等,此时{cs,rs}==2'b00。

显示模块用于完成划定显示区域、移动GRAM (显存)坐标到显示的位置、写GRAM等操作,此时{cs,rs}==2'b01。显示区域由寄存器0x0050 (HSA),0x0051(HEA),0x0052(VSA),0x0053 (VEA)来指定。其中HAS、HEA分别表示水平开始位置、水平结束位置。实验中,取R50H=38H,R51H=B7H,R52H=60H,R53H=DFH。GRAM的地址会根据AM,ID[1:0]的设置而自动的加1,超过分界会自动循环[12],取max(x)=512,max(y)= 512;addr=y+x×512。经过以上配置后,就可以写GRAM了。在显示时虽然对图像进行缩放处理1/4,仍然需要把原始图像的数据全部写入到ILI9325,只不过ILI9325不把全部数据写入内部的GRAM,而是ILI9325自己根据调整因子有选择的把原始图像的数据写入GRAM。

图6 仿真验证

初始化模块和显示模块在控制模块的作用下协调工作。初始化信号有效后,初始化模块通过写模块完成对ILI9325的寄存器的配置。初始化完成后,初始化模块发出完成信号,控制模块收到后将初始化有效信号拉低并将显示有效信号置高,显示色彩空间转换后的RGB图像。

初始化模块与显示模块中的写模块是同一个模块,根据写时序,分别完成初始化和传送RGB图像数据的功能。具体操作可通过4个控制引脚RD、WR、RS、CS来完成[12]。其中RD读,下降沿有效,在本设计中并未使用;WR写,上升沿有效;RS命令/数据选择,低电平时把数据赋给地址指针寄存器,高电平时写到数据口的数据被放进相应寄存器; CS是片选信号,低电平有效。另外RESET是复位引脚,低电平有效,至少要保持1 ms;编写驱动程序时,要注意TFT液晶的各种电压信号在上电和断电时特定的顺序[13]。

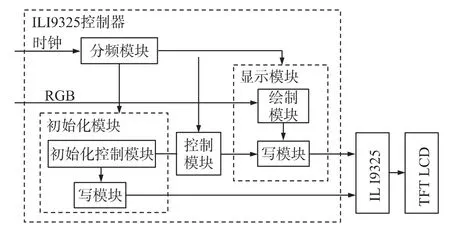

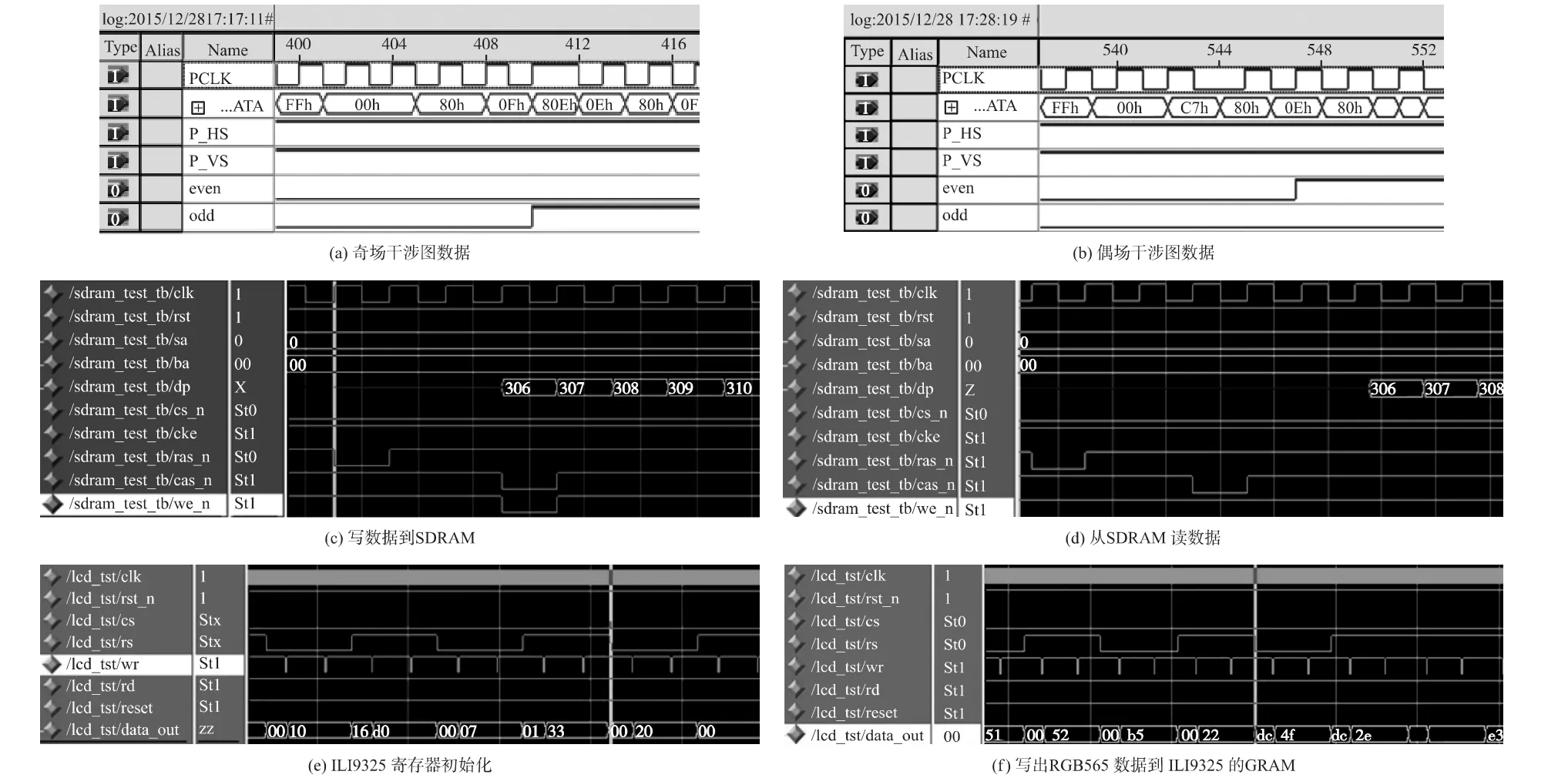

3 实验结果及结论

3.1 仿真与验证

图6(a)、图6(b)是SignalTapⅡ仿真的结果,表明SAA6113模数转换成功,成功得到的奇偶场数据,也表示SAA6113初始化成功。图6(c)、图6(d) ModelSim仿真结果,SDRAM读写时序满足数据手册要求,对写入的数据可原样读出,其中读SDRAM时,CAS潜伏期为2。图6(e)为ILI9325初始化时序仿真,图6(f)为写GRAM时序仿真,时序均满足数据手册要求,经硬件测试,可成功显示Img2Lcd取模,MATLAB转化为mif的RGB565图片。综上,各功能模块均正常工作,为后续进行光谱复原奠定了良好的基础。

3.2 结论

本文利用可见光相机输出的图像来模拟干涉图信号,设计并实现了一种基于FPGA的干涉图采集、存储与显示系统,具有速度快、体积小、便于在线升级等优点,能够实现目标图像的实时采集、存储与显示,仿真结果证明了系统设计的正确性,为后续的光谱复原实时处理部分的实施奠定了良好的技术基础。

[1]Kastek M,Piatkowski T,Trzaskawka P.Infrared Imaging Fourier Transform Spectrometer as the Stand-off Gas Detection System[J].Metrology and Measurement Systems,2011,18(4):607-620.

[2]殷世民,计忠瑛,崔燕,等.傅里叶变换成像光谱仪CCD像元响应非均匀性校正[J].航天器工程,2010,19(1):41-45.

[3]Kuznetsov A V,Andreeva E V.Features of Application of Video Capture Devices in Television Pyrometers[J].Instruments&Experimental Techniques,2011,54(3):440-442.

[4]朱诚诚,石晶晶,陈斯,等.基于Verilog HDL的IIC总线IP核设计[J].电子器件,2015(6):1336-1340.

[5]Corcoran P.Two Wires and 30 Years:A Tribute and Introductory Tutorial to the I2C Two-Wire Bus[J].Consumer ElectronicsMagazine IEEE,2013,2(3):30-36.

[6]刘杰,赛景波.基于DDR2 SDRAM乒乓双缓冲的高速数据收发系统设计[J].电子器件,2015(3):650-654.

[7]Goossens S,Chandrasekar K,Akesson B.Power/Performance Tradeoffs in Real-Time SDRAM Command Scheduling[J].IEEE Transactions on Computers,2015(99):1-14.

[8]JangW.Error-Correcting Code Aware Memory Subsystem[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,2014,33(11):1706-1717.

[9]Riho Y,Nakazato K.Partial Access Mode:New Method for Reducing Power Consumption of Dynamic Random Access Memory[J].Very Large Scale Integration Systems IEEE Transactions on,2014,22(7):1461-1469.

[10]Li N,Wang J.A Highly Efficient SDRAM Controller Supporting Variable-Length Burst Access and Batch Process for Discrete Reads[J].International Journal of Electronics,2015,103(3): 406-423.

[11]刘佳庆.基于FPGA的视频解码系统的设计与研究[D].哈尔滨理工大学,2013.

[12]熊鑫.基于FPGA的嵌入式多媒体播放设计[D].西安电子科技大学,2011.

[13]张旭,张红娟,靳宝全,等.基于MST703的TFT-LCD驱动方案研究与设计[J].电子器件,2015,38(6):1268-1272.

王具民(1987-),男,汉,安徽亳州人,桂林电子科技大学生命与环境科学学院,硕士,主要研究方向为光电成像与信号处理,polycer@sina.com;

陈真诚(1965-),男,汉,湖南永州人,桂林电子科技大学生命与环境科学学院,博士,主要研究方向为生物传感与智能仪器,polycer@163.com。

The Design of Real-Time Data Acquisition and Display System of Fourier Transform Imaging Spectrometer Based on FPGA*

WANG Jumin,YIN Shimin,CHEN Hongbo,GAO Liwei,CHEN Zhencheng*

(School of Life and Environmental sciences,Guilin University of Electronic Technology,Guilin Guangxi 541004,China)

By using visible light camera to simulate interferometer,we had designed a real-time data acquisition and display system of Fourier transform imaging spectrometer based on FPGA,which should establish a good technical foundation for the subsequent real-time spectrum recovery of spectrometer.The system ismainly composed of four parts of data acquisition,storage,conversion and display,mainly involves the configuration of SAA7113 and ILI9325 chip,the SDRAM controller design,the extraction of pixels,the color space transformation etc.It takes71milliseconds to initialize all parts.After initialization being completed,by the four parts of the system working coordinately,the system can output the target’s image in real-time with some advantages such as fast computation speed,easy to upgrade and being developed in second time etc.

FPGA;imaging spectrometer;Fourier transform;in real-time;data acquisition and display

C:7210G

10.3969/j.issn.1005-9490.2017.01.020

TN47

:A

:1005-9490(2017)01-0103-05

项目来源:国家自然科学基金项目(61265006,61271119,81460273)

2016-02-04修改日期:2016-02-18