硬件加速系统中的PCIe-SRIO桥技术

2017-09-03许家麟韩思齐孙宁霄吴琼之

许家麟,韩思齐,孙宁霄,吴琼之

(北京理工大学 信息与电子学院,北京100081)

硬件加速系统中的PCIe-SRIO桥技术

许家麟,韩思齐,孙宁霄,吴琼之

(北京理工大学 信息与电子学院,北京100081)

针对一种基于PCI Express和Serial RapidIO混合式互连架构的硬件加速系统,介绍了其中基于FPGA实现的低延迟、多通道、跨平台的PCIe-SRIO桥接方法。介绍了该PCIe-SRIO桥的逻辑架构,详细叙述了数据调度方法,给出了系统实现成果以及性能测试结果。该成果解决了标准计算机与硬件加速部件的高速接口问题,比同功能的专用ASIC器件具有更好的适应性以及扩展性。

硬件加速;PCI Express;RapidIO;FPGA

基于混合架构的硬件加速是计算机领域中很重要的研究方向之一。它是指将一些特定的任务从通用CPU移植到硬件处理模块上并进行相应的算法优化。由于硬件设备的专用结构,这些硬件处理模块往往比在基于顺序指令集的CPU上运行同样功能的软件在速度上有大幅度的提升[1]。

文中的主要研究内容是通用CPU和嵌入式计算硬件之间的桥接。这是硬件加速系统的关键技术问题之一,既要求较高的传输速率,也要求数据类型、长度、通道数量的灵活性。当前,计算机系统多采用PCI Express(PCIe)与外设进行数据交互。而高性能的分布式嵌入式处理系统则多采用Serial RapidIO(SRIO)作为接口标准。实现PCIe总线到RapidIO桥,意味着实现了通用计算机与多结点、多类型的分布式硬件计算子系统的接口能力,为硬件加速系统提供了跨架构的数据传输通道。文中介绍了一种基于FPGA的PCIe-SRIO桥接方法,在性能和功能上有效的支撑了大规模硬件加速系统的实现。

文献3中提出了一种PCI-SRIO的桥转接技术,重点描述了PCI到RapidIO各种事务的转接方法,为本文提供了一种设计思路,但是PCI总线已逐渐被淘汰,而PCIe-SRIO桥转接技术的需求则在各应用领域逐渐显现出来。文献2介绍了一种用于CPU与FPGA间DMA通信方案,采用了Scatter Gather的内存管理方法,提高了DMA效率,并且提供了驱动以及API,可应用于Xilinx、Altera的多种FPGA,为本文实现PCIe-SRIO桥接奠定了基础。文献4和文献5分别介绍了FPGA实现RapidIO协议以及RapidIO互连网络。然而,以上文献都是在单独的讨论某一方面的具体问题,例如DMA或者RapidIO的实现。相比之下,本文主要从通用计算机与嵌入式处理系统融合的角度上讨论如何建立两个架构间的高速桥接,并进行了系统实现。

1 系统架构

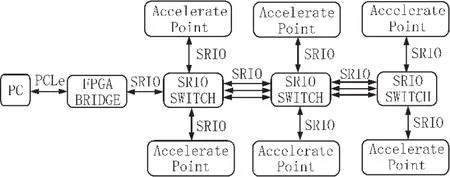

图1给出了本文所针对的硬件加速系统的拓扑结构。负责桥接的FPGA以PCIe接口连接至计算机,计算机通过DMA实现与FPGA的数据交换。FPGA实现PCIe-SRIO桥接,并将数据交由SRIO路由设备分发至各个SRIO网络结点进行处理。处理完成的数据则沿原路径反向传输回计算机。

图1 计算机与嵌入式系统的SRIO互连结构图

计算机作为此硬件加速网络的一个终端节点,既是数据源端也是数据输出端,同时还是整个系统的控制核心。因此,该体系架构要求FPGA实现的PCIe-SRIO桥接具有极高的传输能力和灵活性,具体表现为以下几点:

高传输率:传输速率应能满足计算机与计算网格之间的实时数据交换,否则硬件加速的处理能力将失去意义。

多线程:在硬件加速应用中,输入输出数据的分集、类型、长度以及依赖关系等等会随着算法设计而发生很大变化。在软件上则经常体现为多个不同功能的线程并发工作,每个线程都会有各自的数据传输需求。

信令系统:除了高速数据传输,桥接设备应该还能实现信令的传递,使得计算机可以与某个RapidIO网络结点进行数据流传输的同时对该结点进行监视和控制。

多平台:应能工作在不同的操作系统下,并且能够根据具体的网络结构和数据传输需求调整PCIe-SRIO桥的配置。

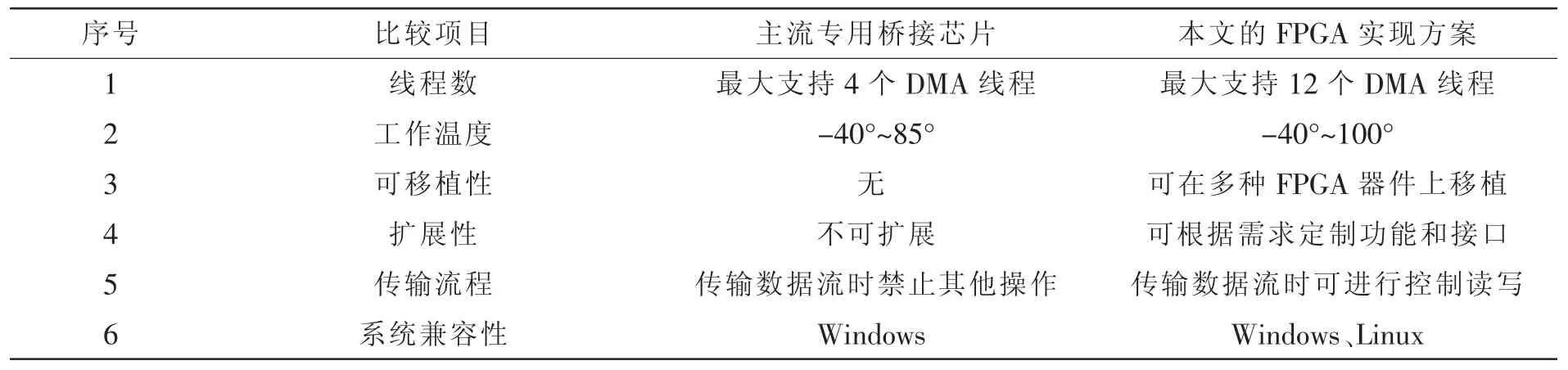

在工程领域,目前主流的桥接方案是采用专用ASIC 芯片,例如 IDT(Integrated Device Technology)公司的TSI721。然而,固定功能的ASIC在一些特定的应用场合下会面临诸多问题,例如传输线程数较少、温度范围窄、可扩展性不足等。文中所选用的FPGA方案与ASIC方案的对比参见表1。

表1 ASIC与FPGA实现实现桥接的性能和功能对比

2 逻辑框架

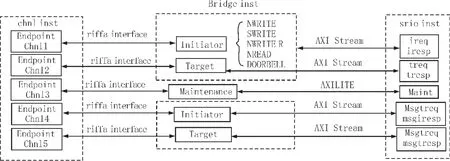

本系统中PCIe到SRIO的数据搬移、调度和管理均由FPGA逻辑固件实现。逻辑设计可以分成PCIe处理模块、SRIO处理模块、桥接模块3个部分。PCIe处理模块主要负责与上位机驱动的DMA过程,SRIO模块负责按照RapidIO协议进行逻辑层的打包并实现传输层和物理层,桥接部分则实现以上两个模块的对接并且实现数据的调度。整体结构如图2所示。

PCIe的DMA实现部分,选用了RIFFA(ReusableIntegrationFrameworkforFPGAAccelerators,可复用的集成FPGA加速架构)解决方案。它实现了CPU与FPGA间的DMA传输,支持Windows、Linux操作系统,并支持多种计算机编程语言和多种FPGA器件。

SRIO模块的主要任务是提供RapidIO协议规定的各种事务操作的基本接口。RapidIO协议是一种基于包的数据交换协议。最常用的几种包格式有:SWRITE(写数据流)、NREAD(读数据)、NWRITE_R(有响应写数据)、NWRITE(无响应写数据)。其中SWRITE适合于大量数据流的传输,与DMA实现对接;NREAD与NWRITE_R适合实现寄存器的读写。SRIO模块主要以Xilinx的SRIO IP核[6]为基础,接口形式为HELLO FORMAT,展现给用户为AXI[7]接口。SRIO模块内部包含3种接口:I/O接口、Message接口、Maintenance接口,其中前两者又分别独立为发起端(initiator)、目的端(target),即一共有 5 个独立的内部数据通道,均为AXI形式。这5个通道与PCIe模块一侧的Endpoint channel1-5分别一一对应。

图2 PCIe-SRIO桥逻辑架构

3 SRIO事务流程

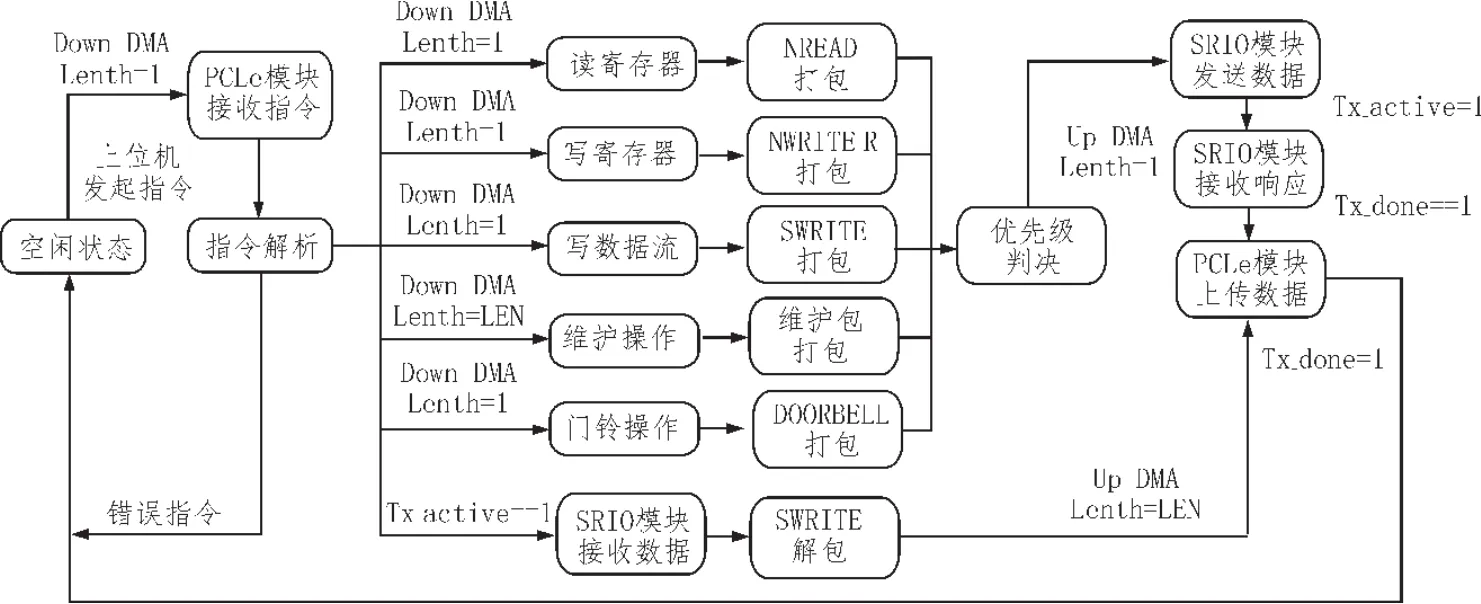

本设计的核心内容是将SIRIO的各个事务操作映射到PCIe和主机端的操作流程。在满足RapidIO协议的同时,此处我们还需要解决SRIO模块与PCIe模块之间的接口适配问题。SRIO处理模块的接口形式AXI Stream,其数据流传输是一种根据tlast信号表征数据流结束的一种无限长度传输机制。而PCIe的DMA传输是一种定长度传输机制。这两者存在着天然的不兼容问题,给事务流程的设计带来一定的难度。

同时,为了解决前述的信令需求,在基本的SRIO读写操作基础上扩展了寄存器读写协议,将系统中所有的参数、命令、状态等信令机制全部封装为寄存器读写。这样一来,桥接模块需要完成的指令类型就包含了读寄存器、写寄存器、读数据流、写数据流、维护包操作几种类型。对于不同的指令类型具体处理流程如下:

1)读写寄存器指令:

分别打包为NREAD、NWRITE_R格式,并且使能TX_active信号,状态机进入接收响应数据状态,接收数据长度为1。SRIO端的响应接口会分别接收到写响应以及回读寄存器值。成功接收到数据后,TX_done拉高,状态机跳转至DMA上传阶段,发起长度为1的DMA上行操作,完成一次寄存器读写。

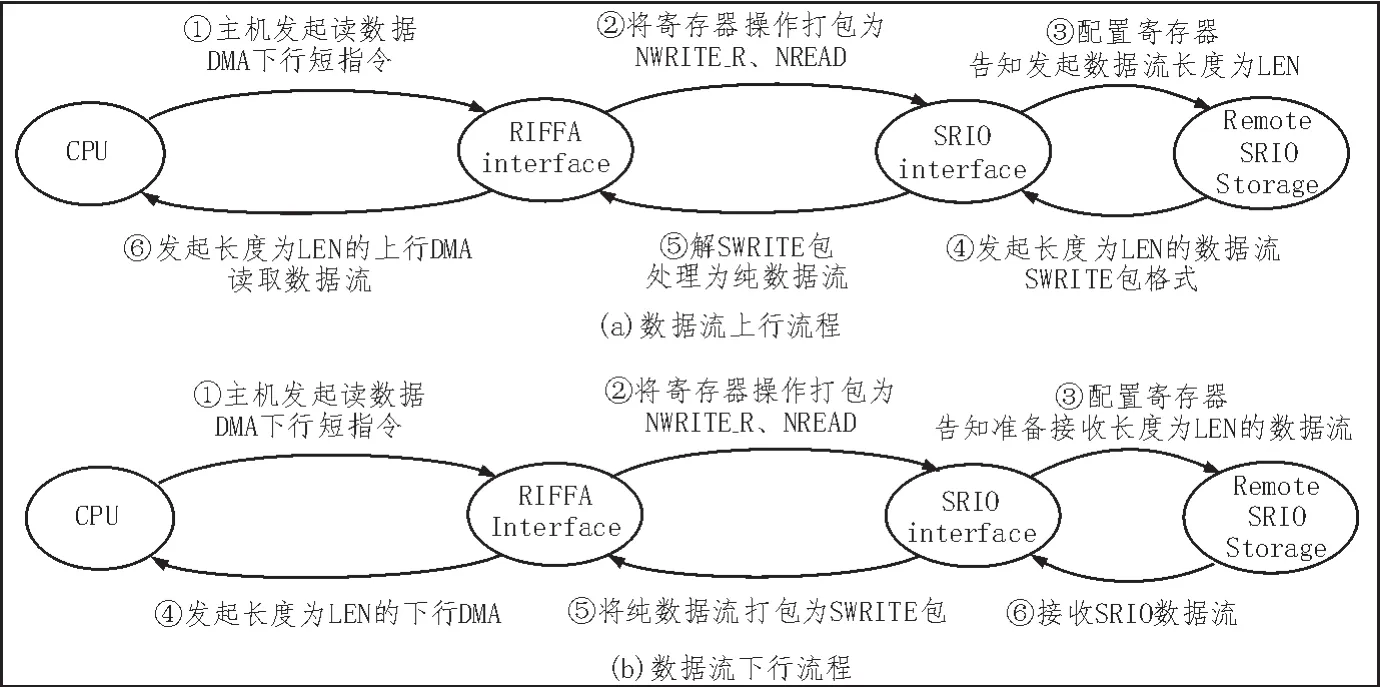

2)读数据流操作:

需要在读数据流前通过寄存器读写来控制远端SRIO设备发起设定长度LEN的SWRITE操作,然后状态机进入发起一次长度为LEN的DMA上行状态,数据量传输结束后跳回空闲状态,完成一次数据流读取操作。

3)写数据流操作:

系统中要求远端设备预知下行数量LEN,因此也要通过寄存器读写来控制远端SRIO设备做好接收数据准备,也可以通过doorbell控制DSP等SRIO设备,这里主要是面向执行硬件加速的FPGA处理板。完成寄存器控制后,状态机进入DMA下行阶段,长度为预先设置的LEN。

4)维护包操作:

类似于读写寄存器操作,状态机进入指令解析后从指令中获取hop count、地址、数据信息,并通过SRIO IP核完成maintenance打包的AXI-LITE接口实现寄存器读写,然后使能TX_active信号,状态机进入接收响应数据状态,接收数据长度为1。SRIO端的AXI-LITE接口会写响应或者回读寄存器值。成功接收到数据后,TX_done拉高,状态机跳转至DMA上传阶段,发起长度为1的DMA上行,完成一次维护包操作。

其中下行的各种包格式在进入SRIO发送模块之前,会进行逻辑判决。传输数据流用的SWRITE包的打包单元是256字节的小包,在传输大量数据流时,判决模块会在两小包间查询是否有DOORBELL、NWRITE_R、NREAD 等拥有更高的优先级的包存在,如果有则优先发送这些包,因此系统可以实现在数据流传输的过程中读写寄存器,访问远端设备状态。

实际系统应用中,实现数据流的上下行传输是由一系列寄存器操作和数据流操作完成的。RapidIO协议中常用于数据流传输的包是SWRITE,这种包具有最高的打包效率,可以最大限度的提升系统的数据传输带宽,因此在发送数据时选用的是这种包格式。

针对数据流读取操作,通常是主端发起NREAD来获取数据流,但是这种打包效率较低。由于FPGA的程序设计是透明的,而且对远端SRIO设备的控制都处理为寄存器操作,可以轻松实现控制远端SRIO设备发起数据流写操作,因此仍使用SWRITE包进行传输,再由桥模块解包并完成数据流上传。具体流程如图4所示。

状态机的设计包容错误指令,以流水线的形式实现PCIe指令/数据到RapidIO包的转换,整个流程的时间开销为固定的9个时钟周期(时钟频率150Mhz),使延迟量控制在了60 ns,适用于实时性较强的系统。

图3 数据调度处理流程

图4 数据流处理流程

4 系统实现与测试

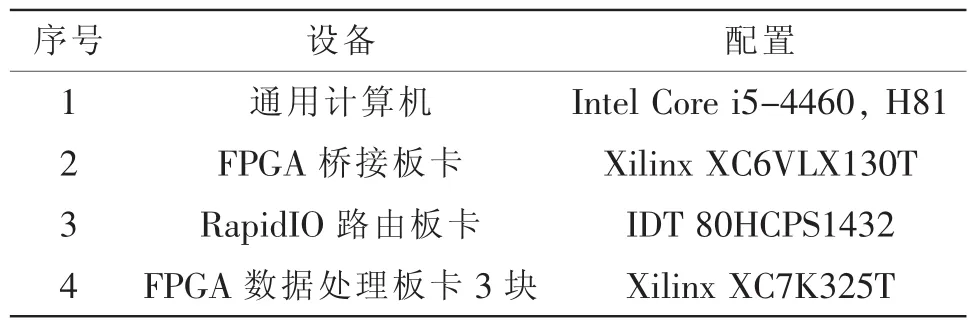

文中提出的解决方案在某FPGA硬件加速系统中得到了应用。通用计算机搭配PCIe-SRIO桥,通过4X SRIO连接RapidIO路由板卡,进而连接至若干FPGA数据处理板卡。具体的测试系统配置如表2所示。

表2 测试系统配置表

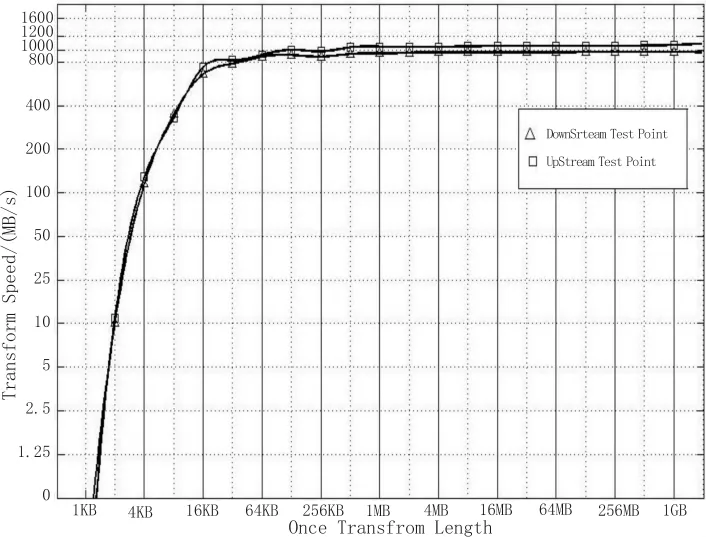

基于上述测试环境,计算机通过桥接模块与各FPGA处理板卡实现数据传输,由主机和处理FPGA互发SWRITE数据包来进行上下行速率测试。测试结果如下图所示,方块曲线代表SWRITE下行速度随着包长度变化的趋势,三角曲线则代表SWRITE上行速度的变化趋势。测试结果表明,该桥接模块的上行、下行传输在包长度达到16 kB后,即可达到700~800 MB/s的速率;包长度超过1 MB后,则可稳定的达到1 GB/s的速率。

5 结束语

文中展示了基于PCIe DMA传输的PCIe-SRIO桥接在FPGA上的实现方法,并给出了系统实现和性能测试结果。RapidIO作为目前高性能嵌入式系统广泛应用的互连技术,在实践中会对PCIe-SRIO桥接的功能和性能提出越来越高的要求,而基于FPGA可编程特性使得本文的PCIe-SRIO桥接方案具有非常大的灵活性和可扩展性。我们未来的工作方向有:1)改善数据调度流程进一步提高流数据的传输带宽;2)研究信令系统传输能力的改善潜力;3)在国产化FPGA、CPU以及操作系统下实现本系统。

图5 桥接模块传输数据流的性能测试结果

[1]Possa P,Schaillie D,Valderrama C.FPGA-based hardware acceleration:A CPU/accelerator interface exploration[C]//Electronics,Circuits and Systems(ICECS), 2011 18th IEEE International Conference on.IEEE,2011:374-377.

[2]Jacobsen M D.Smart Frame Grabber:A Hardware Accelerated Computer Vision Framework[D].University of California,SAN DIEGO,2014.[3]Fuller.The Interconnect Problem[J].Journal of the American College of Cardiology, 2015, 65(10):1-12.

[4]ARM, “AMBA AXI and ACE Protocol Specification AXI3, AXI4, and AXI4-Lite ACE and ACELite”, Oct.2011.

[5]王辉球.一种基于FPGA的Serial RapidIO交换设计[J].电子世界, 2014(6):122-122.

[6]秦小娟.SRapidIO总线在通信设备中的应用[D].南京:东南大学,2014.

[7]冯龙辉,张兴明,杨镇西,等.基于RapidIO控制符产生单元设计与实现 [J].电子技术应用,2015,41(11):48-50.

[8]上官珠,范国忠,高文昀,等.基于RapidIO协议的高速数据互联模块设计[J].现代电子技术,2014,(15):28-31.

[9]邓豹.RapidIO交换互连与配置管理研究[J].航空计算技术,2014(2):124-127.

[10]陈刚,张京,唐建.一种基于FPGA的PCIe总线及其DMA的设计方法 [J].兵工自动化,2014(5):75-77.

[11]赵会彬,马卫平,梁晓英.基于PCIE点对点传输的FPGA系统 [J].计算机系统应用, 2014,23(4):201-204.

[12]吴峰锋,贾嵩,王源,等.一种低时延的串行RapidIO端点设计方案 [J].北京大学学报:自然科学版,2013,49(4):570-578.

[13]陈宏铭,李蕾,姚益武,等.基于AXI总线串行RapidIO端点控制器的FPGA实现[J].北京大学学报:自然科学版, 2014,50(4):697-703.

[14]王维,刘垚,孔超,等.基于RapidIO技术的网络交换板卡的设计与实现 [J].应用声学,2012(3):229-234.

[15]母其勇,王永良,高飞,等.基于SRapidIO及PCIe协议的雷达多通道数据光纤高速记录系统[J].计算机应用, 2015(z2):30-33.

[16]张娟娟,陈迪平,柴小丽.VxWorks下RapidIO互连系统的实现[J].计算机工程, 2011,37(3):236-237.

[17]郑建,徐海.Serial RapidIO桥接以太网设计和实现[J].微处理机, 2015(1):16-18.

PCIe-RapidIO bridge for hardware acceleration systems

XU Jia-lin, HAN Si-qi, SUN Ning-xiao,WU Qiong-zhi

(School of Information and Electronics, Beijing Institute of Technology, Beijing 100081, China)

This paper presents a hybrid interconnection architecture based on both PCI Express and Serial RapidIO for hardware acceleration applications.It introduces a low-latency,multi-channels and platform-compatibility PCIe-SRIO bridge running in FPGA.This paper introduces the logic architecture of the PCIe-SRIO bridge, describes the data scheduling method in details, and provides the system implementation and performance test results.This PCIe-SRIO bridge can provide high speed interface between standard computers and hardware accelerators,and it has better adaptability and expansibility than ASIC devices with the same function.

hardware acceleration;PCI express;RapidIO;FPGA

TN919.5

:A

:1674-6236(2017)15-0189-05

2016-07-06稿件编号:201607043

许家麟(1992—),男,山东菏泽人,硕士研究生。研究方向:电子科学与技术、信号与信息处理。